Fターム[5F101BD33]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | セル配置、セル構造 (2,456)

Fターム[5F101BD33]の下位に属するFターム

ANDゲート、NANDゲート構造 (1,834)

Fターム[5F101BD33]に分類される特許

201 - 220 / 622

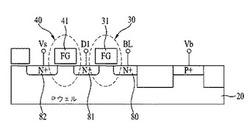

不揮発性メモリ素子及びその駆動方法

【課題】プログラム及び消去動作部分と読み出し動作部分とを分離させることによって、耐久性またはサイクル特性を画期的に改善させる不揮発性メモリ素子及びその駆動方法を提供する。

【解決手段】単一ポリEEPROMの不揮発性メモリ素子は、第1タイプウェル10上に形成されるフローティングゲート50と、第2タイプウェル20上に形成されるとともにフローティングゲート50と直列連結される複数のトランジスタ30,40と、を備え、これらのトランジスタ30,40のうち、いずれかひとつはプログラム及び消去のための第1トランジスタ30であり、他のひとつは読み出し(reading)のための第2トランジスタ40である。

(もっと読む)

半導体素子及び半導体素子のパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を倍加させる半導体素子のパターン形成工程及び該工程を容易に適用可能な構造の半導体素子を提供する。

【解決手段】半導体素子は、第1方向に相互平行に延びている複数のラインパターンを含む。複数のラインパターンのうちから選択される複数の第1ラインパターンは、第2方向に沿って交互に選択されて両側で各々隣接している2つのラインパターンの両端部のうち、素子領域の第1端部にさらに近い各端部に比べて、第1端部からさらに遠く位置する第1端部を有する。複数のラインパターンのうちから選択される複数の第2ラインパターンは、第2方向に沿って交互に選択され、両側で各々隣接している2つのラインパターンの両端部のうち、第1端部にさらに近い各端部より、第1端部からさらに近く位置する第2端部を有する。

(もっと読む)

半導体装置

【課題】シリコン基板に結晶欠陥が発生するのを抑制して、動作の信頼性が確保され高い歩留まりが得られる半導体装置を提供する。

【解決手段】シリコン基板2に形成された溝にトレンチ分離酸化膜3が形成されている。そのトレンチ分離酸化膜3上にフローティングゲート電極10a〜10dおよびコントロールゲート電極12a〜12dが形成されている。フローティングゲート電極等によって挟まれた領域にシリコン基板2の表面を露出する開口部3aが形成されている。開口部3aを埋込むとともにコントロールゲート電極を覆うようにBPTEOS膜16が形成されている。BPTEOS膜16によって埋込まれた開口部3a内にボイド21が形成されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】狭い開口幅のトレンチを形成する場合に活性領域部分が倒壊するのを防止する。

【解決手段】シリコン基板1上に電荷保持層4、電極膜5を積層形成し、一括加工によりトレンチ1a、1bを形成する。上面およびトレンチ1a、1b内にプラズマCVD法によりシリコン酸化膜6を形成する。狭いトレンチ1a内にボイドVaを形成する。シリコン酸化膜6をエッチバックしてボイドVaの上端部を開口する。このとき、トレンチ1aの上部にこれらと直交するようにシリコン酸化膜6を梁部6aとして残すパターニングをする。この後、レジストの剥離、ウェット処理を経るが、梁部6aを設けているので、倒壊するのを防止できる。ポリシラザン膜を埋め込み、水蒸気キュアをしてシリコン酸化膜7に転換する。

(もっと読む)

半導体装置及びその製造方法

【課題】電荷消去特性及び電荷保持特性に優れた半導体装置を提供する。

【解決手段】半導体領域101と、半導体領域の表面に形成されたトンネル絶縁膜102と、トンネル絶縁膜の表面に形成された電荷蓄積絶縁膜103と、電荷蓄積絶縁膜の表面に形成されたブロック絶縁膜104と、ブロック絶縁膜の表面に形成された制御ゲート電極105と、を具備する半導体装置であって、トンネル絶縁膜は、半導体領域の表面に形成され、シリコン及び酸素を含有する第1の領域102aと、第1の領域の表面に形成され、シリコン及び窒素を含有する第2の領域102bと、電荷蓄積絶縁膜の裏面に形成され、シリコン及び酸素を含有する第3の領域102dと、第2の領域と第3の領域との間に形成され、シリコン、窒素及び酸素を含有し、第2の領域の窒素濃度よりも低い窒素濃度を有し、第3の領域の酸素濃度よりも低い酸素濃度を有する第4の領域102cと、を含む。

(もっと読む)

3次元半導体装置及びその動作方法

【課題】3次元半導体装置及びその動作方法を提供する。

【解決手段】3次元半導体装置及びその動作方法が提供される。この装置は、基板上に配置される複数のワードライン構造体と、ワードライン構造体の間に介在される活性半導体パターンと、ワードライン構造体と活性半導体パターンとの間に介在される情報格納要素とを具備する。ワードライン構造体の各々は、互いに離隔されながら積層された複数のワードラインを具備するとともに、活性半導体パターンは、互いに異なる導電型を有しながら交互に配列される電極領域と、チャンネル領域とを具備する。

(もっと読む)

半導体装置

【課題】ソース及びドレインとの接触抵抗のばらつきが少なく、ソース同士が容易に接続

可能なコンタクトプラグ構成の半導体装置を提供する。

【解決手段】ソース及びドレイン領域18、19を有する半導体基板11と、浮遊ゲート

膜22を有し、ソース及びドレイン領域18、19の間の表面に配設されたゲート電極膜

28と、ゲート電極膜28の上に上下を絶縁されたソース接続膜33と、ゲート電極膜2

8及びソース接続膜33を被うサイドウォール絶縁膜37及びバリア絶縁膜39と、バリ

ア絶縁膜39を埋め込む下部及び上部層間絶縁膜41、43と、ソース領域18に接続さ

れ、下部及び上部層間絶縁膜41、43を貫通し断面が楕円形の柱状体をなし、柱状体の

側面でソース接続膜33と接続されたソースコンタクト45と、ドレイン領域19に接続

され、下部及び上部層間絶縁膜41、43を貫通し断面が楕円形の柱状体をなすドレイン

コンタクト47とを備える。

(もっと読む)

半導体装置、及びその製造方法

【課題】ショートの発生と面積の増大とを抑止しつつ、誤書き込みの防止が可能な半導体装置、及びその製造方法を提供すること

【解決手段】本発明にかかる半導体装置は、第1メモリセル領域40a内で、Y方向にソース拡散層を挟んで隣接する第1メモリセル80a及び第2メモリセル80bと、第2メモリセル領域40b内で、第2メモリセル80bのX方向側に配置された第3メモリセル80gと、第3メモリセル領域40c内で、第1メモリセル80aのX方向側に配置された第4メモリセル80hと、第1メモリセル80aと第3メモリセル80gのワードゲートWGを接続する第1接続部91aと、第2メモリセル80bと第4メモリセル80hのワードゲートWGを接続する第2接続部91bとを備え、4つのメモリセル80a、80b、80g、80hのコントロールゲートCGが、それぞれ分離して形成されているものである。

(もっと読む)

不揮発性記憶素子、その製造方法及び不揮発性記憶装置

【課題】電気的性能及び耐プロセス性能が優れた不揮発性記憶素子、その製造方法及び不揮発性記憶装置を提供する。

【解決手段】セリウムと、3価を取り得る金属元素であってセリウムとは異なる金属元素と、を含む蛍石型構造の酸化物を含み、印加される電圧及び通電される電流の少なくともいずれかによって互いに異なる抵抗を有する複数の状態の間を遷移可能な記録層を備えたことを特徴とする不揮発性記憶素子が提供される。また、上記の不揮発性記憶素子と、前記不揮発性記憶素子の前記記録層への電圧の印加、及び、前記記録層への電流の通電、の少なくともいずれかによって、前記記録層を前記互いに異なる抵抗を有する複数の状態の間を遷移させて情報を記録する駆動部と、を備えたことを特徴とする不揮発性記憶装置が提供される。

(もっと読む)

酸化膜の作成方法及び半導体装置の製造方法

【課題】低温の酸化処理により酸化膜を形成する。

【解決手段】酸化膜の作成方法は、主鎖にSi−N結合を有する高分子化合物を含む第1の膜16と主鎖にSi−O結合を有する高分子化合物を含む第2の膜15とを積層する工程と、前記第1の膜16及び前記第2の膜15を水蒸気又は水性の雰囲気中で加熱処理し、前記第1の膜16及び前記第2の膜15を酸化膜18に変化させる工程と、を具備する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 メモリセルにおけるショートチャネル効果の抑制と誤書き込みの防止の両方を実現し、不揮発性半導体記憶装置の高性能・低コスト化をはかる。

【解決手段】 半導体基板101上に複数の不揮発性メモリセルを配置して構成される不揮発性半導体記憶装置であって、メモリセルは、基板101の表面部に離間して設けられたソース・ドレイン領域120と、ソース・ドレイン領域120の直下の基板101内に設けられ、基板101よりも誘電率が低い埋め込み絶縁膜151と、ソース・ドレイン領域120の間に形成されるチャネル領域上に設けられた第1ゲート絶縁膜102と、第1ゲート絶縁膜102上に設けられた電荷蓄積層103と、電荷蓄積層103上に設けられた第2ゲート絶縁膜104と、第2ゲート絶縁膜104上に設けられた制御ゲート電極105とを備えた。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 隣接するゲート電極間に配置されたシールド電極の電位を安定的に保持し、シールド電極によって近接効果を軽減することが可能な不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】 本発明では、半導体基板1上に互いに隣接して配置された浮遊ゲート11と制御ゲート16とを有するゲート電極G1、G2間に、ゲート側壁絶縁膜22を介してシールド電極25を配置している。そして、このシールド電極25は、少なくとも一部が金属とシリコンからなるシリサイド層で構成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】動作信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】シリコン基板11上に、それぞれ複数の絶縁膜及び電極膜14が交互に積層された積層体を設ける。電極膜14は、X方向に延びる複数本の制御ゲート電極CGに分断する。また、積層体内に、選択ゲート電極SGb、SGs、制御ゲート電極CG1〜CG4を貫き、一端がソース線SLに接続され、他端がビット線BLに接続されたU字ピラー30を設ける。そして、最上層の制御ゲート電極CG4に、他の制御ゲート電極CG1〜CG3とは異なる電位を印加する。

(もっと読む)

メモリ回路におけるリーケージ電流を制限する回路および方法

【課題】スタンバイモードにおける集積回路のリーケージ電流を制限する小型かつ容易に集積できる電流制限回路を実現する。

【解決手段】電流制限回路70はスタンバイモードで動作する間に携帯用無線装置10のメモリ回路24のリーケージ電流を制御する。第1の半導体ウエル64が第2の半導体ウエル66に配置されたメモリ回路24を隔離する。スタンバイモードにおいて、電流制限回路は非導通モードに切り替えられ第2の半導体ウエル64と第1の半導体ウエル66で形成されるダイオードおよび基板62と第2の半導体ウエル64で形成されるダイオードのリーケージ電流を制限する。

(もっと読む)

半導体装置

【課題】コンタクト抵抗が低い半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の半導体基板と、埋め込み酸化膜と、第2導電型の半導体層と、を備えるSOI基板に作られ、前記埋め込み酸化膜は、自己に穿設された、前記半導体基板と前記半導体層とを連通する、第1の開口を有し、前記半導体基板は、その表面部分に埋め込み状態に形成され、前記第1の開口内の前記半導体層の埋設部と互いに電気的に接続している、第2導電型の接続層を有し、前記半導体層及び前記埋め込み酸化膜を貫通して、前記接続層の表面部分に至る第2の開口内に埋め込まれて、側面において前記半導体層と電気的に接続し、底面において前記接続層と電気的に接続する、コンタクト電極と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、チャネルストップ領域を素子分離絶縁膜の下の半導体基板中に制御性良く形成することを目的としている。

【解決手段】 本発明は、第1導電型の半導体基板100の表面に設けられた第1の溝部6aと、第1の溝部6aの底面中央部から前記半導体基板の裏面方向に延び、前記第1の溝部6aの幅より小さい幅を有する第2の溝部6bとからなる分離溝6と、この分離溝6内に埋め込まれた素子分離絶縁膜5と、分離溝6の両側の前記半導体基板の表面にそれぞれの側で互いに離間して設けられた前記第1導電型と反対の第2導電型の拡散層10と、拡散層間10の半導体基板上にゲート絶縁膜7を介して形成されたゲート電極20と、第2の溝部6bの底部表面から所定深さにわたり設けられた、第1導電型と同じ導電型でありかつ半導体基板100の不純物濃度よりも高い不純物濃度を有するチャネルストップ領域30と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ビアホール下方でのスペーサ膜の閉塞を回避するとともに、ビアプラグの上方で隣接する配線層との間の余裕距離を確保することができる半導体装置を提供する。

【解決手段】シリコン基板1上に設けられた上面から下面まで貫通するコンタクトプラグ32を有する第1の層間絶縁膜30と、第1の層間絶縁膜30上に形成され、コンタクトプラグ32の形成位置に対応する位置の上面から下面まで貫通するビアホール41を有する第2の層間絶縁膜40と、ビアホール41内にコンタクトプラグ32と電気的に接触するように導電性材料が埋め込まれたビアプラグ43と、を備え、ビアホール41を形成する側壁は、第2の層間絶縁膜40の上面から下面に向かって、基板面に平行な方向の断面積が徐々に減少する順テーパ状を有し、ビアホールの上端部から所定の深さまでの側壁に、第2の層間絶縁膜40とは異なる絶縁性材料からなるスペーサ膜42が埋め込まれている。

(もっと読む)

半導体装置

【課題】電極間絶縁膜として高誘電率絶縁膜を用いた場合における隣接する電荷蓄積層間の寄生容量の増加を抑制できる半導体装置を提供すること。

【解決手段】半導体装置は、半導体基板1と、半導体基板1上に設けられたメモリセルアレイであって、ワード線方向に複数の不揮発性メモリセルが第1の絶縁膜10を介して並んだメモリセル列を含み、複数の不揮発性メモリセルの各々は、トンネル絶縁膜2と、電荷蓄積層3と、誘電率が7以上またはシリコン窒化膜の誘電率よりも高い第2の絶縁膜5と、制御電極6とを備え、第2の絶縁膜5のワード線方向の幅が、電荷蓄積層3の上面から該上面と対向する制御ゲート電極6の対向面に向かって単調に増加し、かつ、前記メモリセル列中のワード線方向に隣接する二つの不揮発性メモリセルの二つの第2の絶縁膜5が、制御ゲート電極6の下面において離れている前記メモリセルアレイとを備えている。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】 フラッシュメモリのフローティングゲートを形成する際に、STI膜間のフロ

ーティングゲート形成領域に、ボイドを発生させることなくポリシリコンを埋め込む。

【解決手段】 STI膜15を等方性エッチング技術を用いてエッチングし、STI膜1

5の側壁を後退させる。次に、後退させたSTI膜15の側壁に第2のシリコンナイトラ

イド膜18を堆積させた後、フローティングゲート形成領域16の上部の間口が広く、シ

リコン基板1に近づくにつれて徐々に間隔が狭くなるようにエッチングしてSTI膜15

の側壁にスペーサ19を形成する。これにより、ポリシリコン20の埋め込み不良の発生

が防ぐことができる。

(もっと読む)

不揮発性半導体記憶装置およびその閾値制御方法

【課題】信頼性よく、かつ高速にメモリセルにデータを書き込むことができる。

【解決手段】NOR型フラッシュメモリは、第1〜第4の電源切替部135〜138を備える。第1の電源切替部135は、ロウデコーダ115内の第1のプリデコーダ131に対して専用の電源電圧VSWiを供給するため、電源電圧VSWiの負荷容量が小さくなり、選択ワード線WL電圧の遷移速度が向上する。また、第2の電源切替部136は、第2のプリデコーダ132、ロウメインデコーダ133およびロウサブデコーダ134に対して、書き込み時とベリファイ読み出し時で電圧レベルが変化しない電源電圧VSW2iを供給するため、電源電圧VSW2iの負荷容量が大きくても書き込み時間には大きく影響しない。これにより、書き込みとベリファイ読み出し間の選択ワード線WL電圧の切替を迅速に行うことができる。

(もっと読む)

201 - 220 / 622

[ Back to top ]