Fターム[5F101BD33]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | セル配置、セル構造 (2,456)

Fターム[5F101BD33]の下位に属するFターム

ANDゲート、NANDゲート構造 (1,834)

Fターム[5F101BD33]に分類される特許

121 - 140 / 622

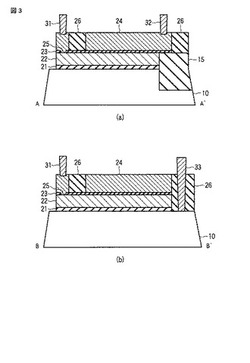

半導体装置と不揮発性半導体記憶装置

【課題】キャパシタのコンタクトプラグ形成に伴うショート不良を低減させることができ、素子信頼性の向上をはかる。

【解決手段】半導体装置であって、半導体基板10上に、第1の絶縁膜21,第1の導電層22,第2の絶縁膜23,及び第2の導電層24が積層され、且つ導電層22,24の一部が接続された積層構造部と、導電層22を接続部を含む第1の領域と接続部を含まない第2の領域に分離する層間絶縁膜26と、第2の領域の一周辺部で、導電層21,絶縁膜22,及び基板10に形成された素子分離溝に埋め込まれた素子分離絶縁膜15と、第1の領域に接続された第1のコンタクトプラグ31と、第2の領域に接続され且つ素子分離絶縁膜15の上方に形成された第2のコンタクトプラグ32と、第2の領域側の一周辺部に隣接する領域で基板10に接続された第3のコンタクトプラグ33を備えた。

(もっと読む)

半導体記憶装置

【課題】コストを増大させずとも、書き込みに高電圧を必要とせず、不良が発生しにくく、書き込み時間が短く、データの書換えができない半導体記憶装置を提供する。

【解決手段】ダイオード接続した第1のトランジスタと、ダイオード接続した第1のトランジスタのソース電極及びドレイン電極の一方の端子にゲートが接続する第2のトランジスタと、ダイオード接続した第1のトランジスタのソース電極及びドレイン電極の一方の端子及び第2のトランジスタのゲートに接続する容量素子を有するメモリ素子を含む半導体記憶装置である。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】素子分離絶縁膜の埋め込み後の化学機械研磨法による研磨で、浮遊ゲート電極をストッパ膜として使用できるようにする。

【解決手段】シリコン基板1にゲート絶縁膜4、下層多結晶シリコン膜5a、上層多結晶シリコン膜5bを積層形成する。上層多結晶シリコン膜5bは、成膜時に炭素を1×1018atoms/cm3以上例えば2×1020〜2×1021atoms/cm3の範囲の濃度で添加される。素子分離溝1bを形成した後に、素子分離絶縁膜2を埋め込み、化学機械研磨法の研磨で素子分離溝1b内以外の部分を除去する。この時、上層多結晶シリコン膜5bがスクラッチの発生を抑制できるストッパ膜として利用でき、シリコン窒化膜などを不要とした構成とすることができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み/消去におけるディスターブを抑制し、かつ面積の増大を抑えた不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルMCを含む第1セルアレイ32が形成された第1導電型の第1のウェル領域と、複数のメモリセルMCを含む第2セルアレイ32が形成された第1導電型の第2のウェル領域と、第1、第2のウェル領域を含む第2導電型の第3のウェル領域とを備える。さらに、第1セルアレイ32が含むメモリセルと第2セルアレイ32が含むメモリセルとに共通に接続されたビット線BLと、ビット線BLに接続されたカラムデコーダ13とを備える。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法

【課題】オフ状態のソースとドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に、書き込みトランジスタのソースを書き込みビット線に、読み出しトランジスタのソースとドレインとを、それぞれ、読み出しビット線及びバイアス線に接続する。さらに、キャパシタの他方の電極を読み出しワード線に接続する。配線数を減らすために、読み出しビット線を書き込みビット線や他の列のバイアス線で代用する。

(もっと読む)

不揮発性フラッシュメモリ

【課題】低消費電力、低減されたリーク問題、および単純なプロセスを伴った新規なフラッシュメモリ、新規なプログラミング方法、およびそのセンシングスキームを提供する。

【解決手段】ワード線218、第1のビット線204、および第2のビット線206を備えた不揮発性メモリセル200を動作させる方法は、メモリセル200をプログラミングする工程を有し、そのプログラミングする工程が、高い正電圧のバイアスを第1のビット線に印加し、接地バイアスを第2のビット線に印加し、高い負電圧のバイアスをワード線に印加することを備え、正帯電ホールが誘電体層212を介してトラッピング層214に突き抜けるようにする。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】不揮発性半導体記憶装置の高集積化,高耐圧化,高速化,加工容易性を同時に実現する。

【解決手段】トンネル絶縁膜上のフローティングゲート電極層,ゲート間絶縁膜,第1,第2コントロールゲート電極層及び金属シリサイド膜を備えるメモリセルトランジスタと、高電圧用ゲート絶縁膜21上の高電圧用ゲート電極層51,一部分開口したゲート間絶縁膜25,第1,第2コントロールゲート電極層48,46及び金属シリサイド膜53を備える高電圧トランジスタと、トンネル絶縁膜20上のフローティングゲート電極層50,一部分開口したゲート間絶縁膜25,第1,第2コントロールゲート電極層48,46及び金属シリサイド膜53を備える低電圧トランジスタと、メモリセルトランジスタ,高電圧トランジスタ及び低電圧トランジスタのソース・ドレイン領域上に直接配置されるライナー絶縁膜27とを備える不揮発性半導体記憶装置の製造方法。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体を用い、オフ状態でのソースとドレイン間のリーク電流(オフ電流)が少ない書き込み用トランジスタ、該書き込み用トランジスタと異なる半導体材料を用いた読み出し用トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。該メモリセルへの情報の書き込み及び書き換えは、書き込み用トランジスタをオン状態とすることにより、書き込み用トランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給し、その後、書き込み用トランジスタをオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。

(もっと読む)

不揮発性半導体記憶装置、および不揮発性半導体記憶装置の製造方法

【課題】ライトディスターブ(WDT)が発生しない不揮発性半導体記憶装置を提供する。

【解決手段】第1方向に延伸する第1素子分離絶縁領域42と、その第1素子分離絶縁領域42と異なる第2素子分離絶縁領域42と、第1メモリセル2と、第2メモリセル15とを具備する不揮発性半導体記憶装置1を構成する。ここで、その第1メモリセル2は、第2方向に延伸する第1コントロールゲート21を備える。その第2メモリセル15は、その第1コントロールゲート21に対向する第2コントロールゲート35を備える。その第1コントロールゲート21は、第1引き出し電極3に接続されている。その第1引き出し電極3は、その第2コントロールゲート35の側面から離れた位置のその第1素子分離絶縁領域42を掘り下げた第1掘り下げ領域7の内部に設けられるものである。

(もっと読む)

半導体装置及びその製造方法

【課題】不揮発性メモリを用いた半導体装置において、消去動作の高速化及び低消費電力化を実現する。

【解決手段】チャネル形成領域、トンネル絶縁膜及び浮遊ゲートを順に積層した不揮発性メモリにおいて、チャネル形成領域を酸化物半導体層により構成する。さらに、チャネル形成領域の下側に、浮遊ゲートと対向する位置に消去用の金属配線を設けた構造とする。上記構造により、消去動作において、浮遊ゲートに蓄積された電荷はチャネル形成領域を介して金属配線に引き抜かれる。これにより、半導体装置の消去動作を高速化し、低消費電力化を実現できる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的とする。

【解決手段】チャネル形成領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極及び第1のドレイン電極と、を有する第1のトランジスタと、酸化物半導体層と、第2のソース電極及び第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、第2のソース電極または第2のドレイン電極の一方と、第2のゲート絶縁層と、第2のゲート絶縁層上に第2のソース電極または第2のドレイン電極の一方と重畳するように設けられた電極と、を有する容量素子と、を有し、第1のゲート電極と、第2のソース電極又は第2のドレイン電極の一方とは電気的に接続されている。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のソース電極および第1のドレイン電極と、第1のソース電極および第1のドレイン電極と電気的に接続され、酸化物半導体材料が用いられている第1のチャネル形成領域と、第1のチャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、を有する第1のトランジスタと、容量素子と、を有し、第1のトランジスタの第1のソース電極または第1のドレイン電極の一方と、容量素子の電極の一方とは、電気的に接続された半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】本発明の一態様は、酸化物半導体を用いたデバイスにおいて高い移動度を達成し、信頼性の高い表示装置を提供する。

【解決手段】表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層を形成し、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加熱処理を行うことにより、酸化物半導体層に酸素を供給し、酸化物絶縁層上に、水素を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

スプリットゲート不揮発性メモリセルの作製に有用な半導体構造を形成する方法

半導体層(12)に半導体デバイス(10)を形成する方法が提供される。方法は、半導体層(12)の上方に選択ゲート誘電体層(14)を形成すること、選択ゲート誘電体層(14)の上方に選択ゲート層(16)を形成すること、選択ゲート層の少なくとも一部分を除去することによって、選択ゲート層(16)の側壁を形成することを含む。方法は、選択ゲート層(16)の側壁の少なくとも一部分に、および選択ゲート層(16)の少なくとも一部分の下に、犠牲層(22)を成長させること、犠牲層(22)を除去して、選択ゲート層の側壁の少なくとも一部分の表面および選択ゲート層の下の半導体層の表面を露出させることをさらに含む。方法は、制御ゲート誘電体層(28)、電荷蓄積層(32)、および制御ゲート層(34)を形成することをさらに含む。 (もっと読む)

不揮発性メモリセル、これを有するメモリアレイ、並びに、セル及びアレイの操作方法

【課題】自己収束消去動作を容易にすると共に保持状態の期間におけるメモリデバイスの電荷蓄積層内での電荷保持能力を保持してもいるトンネル誘電体構造を有する不揮発性メモリデバイスの提供。

【解決手段】半導体基板101であって、該基板の表面より下に配置され且つチャネル領域106によって分離されたソース領域102及びドレイン領域104を備えた半導体基板と、前記チャネル領域より上に配置されたトンネル誘電体構造102であって、低いホールトンネリング障壁高さを有する少なくとも1つの層を備えたトンネル誘電体構造と、前記トンネル誘電体構造より上に配置された電荷蓄積層130と、前記電荷蓄積層より上に配置された絶縁層140と、前記絶縁層より上に配置されたゲート電極150とを有するメモリセル、該メモリセルのアレイ及び操作方法と共に開示する。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトランジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

記憶装置

【課題】ロジック回路を増やすことなく、第三者がメモリセルにアクセスできずかつ必要な場合にはいつでもアクセス可能なメモリセルを有する記憶装置を提供する。

【解決手段】本実施形態は、第1のメモリセルと、第2のメモリセルと、を有し、第2のメモリセルに設けられた第2のトランジスタの第2のチャネルが酸化物半導体膜からなる記憶装置であって、第2のメモリセルからのデータの読み出しは第2のトランジスタに紫外線を照射している時に行われる記憶装置によって解決する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタ160と、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置

【課題】スイッチ用トランジスタとメモリ用トランジスタとからなる2トランジスタ構造のNOR型メモリセルによって構成される不揮発性メモリの信頼性を向上させることのできる技術を提供する。

【解決手段】スイッチゲート電極SGとメモリゲート電極FGとを離間して配置し、スイッチゲート電極SGのドレイン領域Drm側の片側面およびメモリゲート電極FGのソース領域Srm側の片側面にそれぞれサイドウォール14を形成し、スイッチゲート電極SGとメモリゲート電極FGとの間は絶縁膜14aにより埋め込む。ドレイン領域Drmおよびソース領域Srmはそれぞれ低濃度の半導体領域12と高濃度の半導体領域15により構成するが、スイッチゲート電極SGとメモリゲート電極FGとの間の距離をサイドウォール14の2倍未満とし、ここには低濃度の半導体領域12のみを形成する。

(もっと読む)

121 - 140 / 622

[ Back to top ]