Fターム[5F101BD40]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | 基体材料 (372) | 3、5族 (150)

Fターム[5F101BD40]に分類される特許

61 - 80 / 150

半導体装置の製造方法

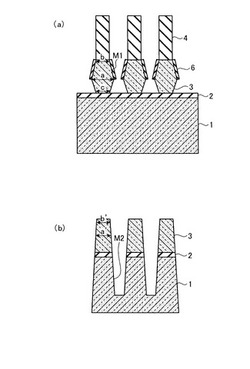

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置の駆動方法

【課題】新たな構造の半導体装置、及びその駆動方法を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のpチャネル型トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電荷を保持させることで行う。また、保持期間において、メモリセルを選択状態とし、且つ、読み出し用トランジスタのソース電極およびドレイン電極を同電位とすることで、ノードに蓄積された電荷を保持する。

(もっと読む)

半導体メモリ装置

【課題】短チャネルでも動作するフローティングゲートを有する半導体メモリ装置を提供する。

【解決手段】フローティングゲート104に窒化インジウム、窒化亜鉛等の仕事関数が5.5電子ボルト以上の高仕事関数化合物半導体を用いる。このことにより、基板101とフローティングゲート104の間のフローティングゲート絶縁膜103のポテンシャル障壁が従来のものより高くなり、フローティングゲート絶縁膜103を薄くしても、トンネル効果による電荷の漏洩を低減できる。フローティングゲート絶縁膜103をより薄くできるのでチャネルをより短くできる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、窒素、リン、又は砒素など15族元素のいずれか一以上の元素が添加されている。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

半導体記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能(不揮発性)で、且つ、書き込み回数にも制限が無い、新たな構造の半導体記憶装置を提供する。

【解決手段】半導体記憶装置に、複数のメモリセルがマトリクス状に配設されたメモリセルアレイと、制御信号に応じて、複数のメモリセルの中から動作を行うメモリセルを選択するデコーダと、デコーダに対して制御信号を出力するか否かを選択する制御回路と、を設ける。なお、複数のメモリセルのそれぞれは、酸化物半導体によってチャネル領域が形成される選択トランジスタをオフ状態とすることによってデータの保持を行う。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法

【課題】消費電力の少ない新規の半導体メモリ装置を提供する

【解決手段】書き込みトランジスタWTr_n_mのソースと読み出しトランジスタRTr_n_mのゲートとキャパシタCS_n_mの一方の電極を接続し、書き込みトランジスタWTr_n_mのゲートとドレインを、それぞれ書き込みワード線WWL_nと書き込みビット線WBL_mに、キャパシタCS_n_mの他方の電極を読み出しワード線RWL_nに、読み出しトランジスタRTr_n_mのドレインを読み出しビット線RBL_mに接続した構造とする。ここで、読み出しビット線RBL_mの電位はフリップフロップ回路FF_mのような反転増幅回路に入力され、反転増幅回路によって反転された電位が書き込みビット線WBL_mに出力される構造とする。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】SRAMは高速で省電力なメモリであるが、携帯機器等で使用するにはさらなる省電力化が求められる。

【解決手段】オフ抵抗が極めて高いトランジスタを書き込みトランジスタとし、書き込みトランジスタのドレインを書き込みビット線に、ソースをCMOSインバータの入力に接続し、読み出しトランジスタのドレインを読み出しビット線に、ソースをCMOSインバータの出力に接続したメモリセルを用いる。書き込みトランジスタのソースにはキャパシタを意図的に設けてもよいが、CMOSインバータのゲート容量あるいはCMOSインバータの正極や負極との間の寄生容量等を用いることもできる。データの保持はこれらのキャパシタに蓄積された電荷によっておこなえるため、CMOSインバータの電源間の電位差を0とできる。このため、CMOSインバータの正負極間を流れるリーク電流がなくなり、消費電力を低減できる。

(もっと読む)

結晶性酸化物半導体膜の作製方法

【課題】優れた結晶性を有する酸化物半導体膜を作製する。

【解決手段】酸化物半導体の膜を形成するに際し、基板を第1の温度以上第2の温度未満に加熱しつつ、基板の、典型的な長さが1nm乃至1μmの部分だけ、第2の温度以上の温度に加熱する。ここで、第1の温度とは、何らかの刺激があれば結晶化する温度であり、第2の温度とは、刺激がなくとも自発的に結晶化する温度である。また、典型的な長さとは、その部分の面積を円周率で除したものの平方根である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込みワード線に電気的に接続する容量素子またはノイズ除去回路を設けることで、駆動回路等からメモリセルに入力されうる制御信号とは異なる短パルスやノイズ等の信号を低減または除去することができる。これにより、メモリセルが有するトランジスタが瞬間的にオンすることでメモリセルに書き込まれたデータが消失してしまう誤動作を防ぐことが可能である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな駆動方法を提供する。また、新たな駆動方法により、メモリ素子への書き込み電位のばらつきを低減し、信頼性を向上させる。

【解決手段】半導体装置の駆動方法において、書き込み電位を段階的に上昇させて、同時に読み出し電流を確認し、読み出し電流の結果を書き込み電位に利用して書き込みを行う。つまり、正しい電位で書き込みが行われたか確認しながら書き込みを行うことで、信頼性の高い書き込みを行うことが可能である。

(もっと読む)

半導体メモリ装置の駆動方法

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを長期間にわたり保存する半導体メモリ装置の駆動方法を提供する。

【解決手段】書き込みトランジスタのドレインと素子トランジスタのゲート、および、容量素子の一方の電極を接続したメモリセルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に接続し、キャパシタの他方の電極を読み出しワード線に接続する。そして、容量素子に蓄えられた電荷量を、読み出しワード線の電位を変化させることにより確認し、基準以上に電荷量が減少している場合にはメモリセルのリフレッシュをおこなう。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込みを高速化した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置110は、ベース半導体層10aと、電極70aと、チャネル半導体層30aと、ベーストンネル絶縁膜20aと、チャネルトンネル絶縁膜40aと、電荷保持層50aと、ブロック絶縁膜60aと、を有するメモリ部MC1を備える。チャネル半導体層30aは、ベース半導体層10aと電極70aとの間に設けられ、電極70aに対向するチャネル部31aを含む。ベーストンネル絶縁膜20aは、ベース半導体層10aとチャネル半導体層30aとの間に設けられる。チャネルトンネル絶縁膜40aは、電極70aとチャネル部31aとの間に設けられる。電荷保持層50aは、電極70aとチャネルトンネル絶縁膜40aとの間に設けられ、電荷を保持する。ブロック絶縁膜60aは、電極70aと電荷保持層50aとの間に設けられる。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

不揮発性メモリのゲートのパターニング方法

【課題】不揮発性メモリ(NVM)領域及び前記NVM領域と重ならないよう非NVM領域を有する半導体基板の上にNVMのゲートスタックを形成する。

【解決手段】

上記の製造方法は、半導体基板上のNVM領域及び非NVM領域に選択ゲート層を形成する工程と、NVM領域及び非NVM領域における選択ゲート層を同時にエッチングする工程と、NVM領域及び非NVM領域における半導体基板上に電荷蓄積層を形成する工程と、NVM領域及び非NVM領域における電荷蓄積層上に制御ゲート層を形成する工程と、NVM領域及び非NVM領域における電荷蓄積層を同時にエッチングする工程とを備える。NVM領域における選択ゲート層をエッチングする工程は、電荷蓄積層の部分が選択ゲート層の第1部分上にあり、かつ選択ゲート層の第1部分の側壁と重なるように行い、かつ、制御ゲート層の部分を電荷蓄積層の部分上にあるように行う。

(もっと読む)

半導体装置

【課題】高集積化を図り、単位面積あたりの記憶容量を増加させた新たな構造の半導体装置を提供することを目的の一とする。高集積化に伴い増加する回路素子数の低減が可能で、かつ、素子数低減による電力削減が可能な、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ビット線と、m(mは3以上の自然数)本のワード線と、ソース線と、m本の信号線と、第1乃至mのメモリセルと、駆動回路と、を有する半導体装置において、メモリセルは、第1のトランジスタ、容量素子に蓄積された電荷を保持する第2のトランジスタを含み、第2のトランジスタは酸化物半導体層で形成されるチャネルを有する。上記構成において、駆動回路は、第j(jは3以上の自然数)の信号線に出力される信号を用いて第(j−1)の信号線に出力される信号を生成する。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】周辺回路領域の素子の寿命が劣化するのを抑制しつつ、浮遊ゲート電極と制御ゲート電極とのカップリング性を確保する。

【解決手段】シリコン基板11は、セル領域および周辺回路領域が設けられている。トンネル絶縁膜12は、セル領域および周辺回路領域のシリコン基板11上に形成されている。浮遊ゲート電極膜13は、セル領域および周辺回路領域のトンネル絶縁膜12上に形成されている。電極間絶縁膜16は、セル領域の浮遊ゲート電極膜13上に形成されている。シリコン酸化膜14および電極間絶縁膜16は、周辺回路領域の浮遊ゲート電極膜13上に形成されている。制御ゲート電極膜17は、セル領域および周辺回路領域の電極間絶縁膜16上に形成されている。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】専有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、該記憶ゲートを絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1及び第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された読み出し信号線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

61 - 80 / 150

[ Back to top ]