Fターム[5F101BD40]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | 基体材料 (372) | 3、5族 (150)

Fターム[5F101BD40]に分類される特許

121 - 140 / 150

トランジスタ、集積回路および集積回路形成方法

【課題】トランジスタ、集積回路、および、集積回路形成方法を提供する。

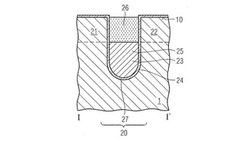

【解決手段】半導体基板1内に形成されたゲート溝27内にゲート誘電体24を介してゲート電極23が配置された構成を有する。該ゲート電極23は、導電性炭素材を有している。

(もっと読む)

半導体装置の作製方法

【課題】大面積基板に、高性能な半導体素子、及び集積回路を高スループットで生産性よく作製することを目的とする。

【解決手段】単結晶半導体基板(ボンドウエハー)より単結晶半導体膜を転置する際、単結晶半導体基板を選択的にエッチング(溝加工ともいう)し、作製する半導体素子の大きさに複数に分割された複数の単結晶半導体層を、異種基板(ベース基板)に転置する。従って、ベース基板には、複数の島状の単結晶半導体層(SOI層)を形成することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】外部から局所的に圧力がかかっても破損しにくい半導体装置を提供する。また、外部からの局所的押圧による非破壊の信頼性が高い半導体装置を歩留まり高く作製する方法を提供する。

【解決手段】単結晶半導体領域を用いて形成された半導体素子を有する素子基板上に、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体を設け、加熱圧着することにより、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体及び素子基板が固着された半導体装置を作製する。

(もっと読む)

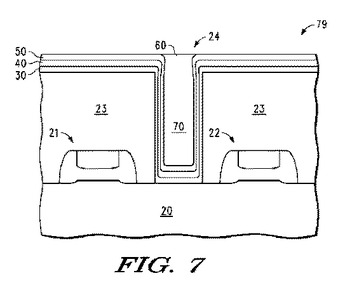

ボイドの無いコンタクトプラグ

コンタクトプラグを形成する半導体素子形成プロセスでは、チタンまたはタンタルコンタクト層(30)、窒化チタンバリア層(40)、及びタングステンシード層をコンタクト開口部(24)に順番に堆積させる。次に、コンタクトホール(24)への充填を、コンタクト開口部の底面から上に向かって、銅層(60)を電気メッキすることにより行なって、ボイドがコンタクト開口部(24)内に形成されることがないようにする。全ての余分な材料をCMPプロセスにより除去してコンタクトプラグ(70)を形成し、この場合、CMPプロセスを使用して、コンタクト層/シード層/バリア層(30,40,50)のうちの一つ以上の層を薄くする、または除去することもできる。  (もっと読む)

(もっと読む)

不揮発性メモリ素子及びその動作方法

【課題】動作信頼性が高くて高集積化が可能である不揮発性メモリ素子及びその動作方法を提供する。

【解決手段】不揮発性メモリ素子は半導体基板110aを含み、電荷保存層120は、半導体基板上110aに提供され、例えばポリシリコン、金属、シリコン窒化膜、量子ドット、またはナノクリスタルを含むことができ、制御ゲート電極140は、電荷保存層140上に提供され、第1補助ゲート電極130aと第2補助ゲート電極130bは、電荷保存層140の一側に離隔配置され、半導体基板110aから絶縁される。この不揮発性メモリ素子によれば、メモリトランジスタ内部にソース及びドレイン領域が省略され、代わりに第1補助ゲート電極130a及び第2補助ゲート電極130bが配され、不純物ドーピングによるソース及びドレイン領域より微細線幅に形成され、従って不揮発性メモリ素子の集積度向上に寄与できる。

(もっと読む)

メモリーセル、及びデータ記録方法

本発明は、少なくとも一のビット・データを記憶するメモリーセル(10)に関する。当該メモリーセルは、少なくとも二つの電気的接続(40、130)と、少なくとも一のポテンシャル井戸(200)を有するバンド曲線(EL)を伴う半導体構造(11)で構成されている。供給電圧(Us=Uspeis)を二つの電気的接続へ印加することによってポテンシャル井戸が電荷担体で帯電された状態が増大し、放電電圧(Us=Usperr)を印加することによって減少するほか、維持電圧(Us=Ubei)を印加することによってこの状態が維持されて、それぞれ帯電したポテンシャル井戸の状態がメモリーセルのビット・データ片を決定する。本発明によれば、この半導体構造が空間電荷ゾーン(Wn)を有しており、ポテンシャル井戸が半導体ヘテロ接合(80)によって形成されている。この半導体ヘテロ接合と空間電荷ゾーンは、維持電圧が印加されている場合は空間電荷ゾーン内に、供給電圧が印加されている場合は空間電荷ゾーンの周縁もしくは外に、放電電圧が印加されている場合は空間電荷ゾーン内に、半導体ヘテロ接合が位置するように、空間的に相対的な配置がなされている。 (もっと読む)

半導体装置の作製方法及び不揮発性半導体記憶装置の作製方法

【課題】絶縁耐圧の良好な絶縁層を製造する技術を提供することを目的とする。また、絶縁耐圧の良好な絶縁層を有する半導体装置を製造する技術を提供することを目的とする。

【解決手段】シリコンを主成分とする半導体層若しくは半導体基板に対して高密度プラズマ処理を行うことにより、半導体層の表面若しくは半導体基板の上面に絶縁層を形成する。このとき、供給ガスを希ガス、酸素及び水素を含むガスから希ガス及び酸素を含むガスに途中で切り替えて高密度プラズマ処理を行う。

(もっと読む)

不揮発性半導体記憶装置及びその作製方法、半導体装置及びその作製方法、並びに絶縁膜の作製方法

【課題】膜特性に優れる絶縁膜を製造する技術を提供することを目的とする。特に、緻密で高耐圧な絶縁膜を製造する技術を提供することを目的とする。また、電子トラップの少ない絶縁膜を製造する技術を提供することを目的とする。

【解決手段】酸素を含む絶縁膜に対して、高周波を用いて電子密度が1×1011cm−3以上、且つ電子温度が1.5eV以下の条件でプラズマ処理を行う。また、プラズマ処理は、酸素を含む雰囲気下で行う。

(もっと読む)

半導体記憶装置

【課題】微細化しても読み出しエラーが生じ難いAG−AND型フラッシュメモリの半導体記憶装置を得ること。

【解決手段】半導体基板10上にゲート絶縁膜11を介して配置された複数の第1ゲート電極13と、これら複数の第1ゲート電極の各々の上に配置された電気絶縁性のアイソレーション部15と、半導体基板上にトンネル酸化膜21を介して配置された複数の第2ゲート電極19とを備え、1つの第1ゲート電極13を挟んで2つの第2ゲート電極19が対峙している半導体記憶装置30を構成するにあたり、第1ゲート電極13の線幅方向の側方からその上のアイソレーション部15の線幅方向の側方に亘る領域上に電気絶縁膜17を介して第2ゲート電極19を延在させ、かつ複数の第2ゲート電極19の各々の下端部を水平方向に突出させることで各第2ゲート電極19に張り出し部Jを形成する。

(もっと読む)

浮遊ゲートメモリデバイスと製造

互いに分離されたゲート間誘電領域を持つトランジスタを含む浮遊ゲートメモリアレイと、それを製造する方法。浮遊ゲートトランジスタは、アレイ内の浮遊ゲートトランジスタの各々が、浮遊ゲートと、制御ゲートと、その間にゲート間誘電層を持つように形成される。各トランジスタのゲート間誘電層は、アレイ内の他のトランジスタの各々のゲート間誘電体から分離される。そのような構造を製造する方法も提供される。  (もっと読む)

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリの消去動作として、PウェルやNウェルなどの基板端子を用いないで、不揮発性メモリ素子における電荷蓄積部に注入された電荷を放出する、すなわちNAND型不揮発性メモリのデータの消去動作する方法を提供することを課題とする。

【解決手段】NAND型不揮発性メモリにおけるデータの消去方法において、不揮発性メモリ素子における電荷蓄積層に格納された電荷の放出について、ビット線、ソース線、及び制御ゲートに電位を印加することにより行う。そして、不揮発性メモリ素子における電荷蓄積層に格納された電荷の放出を、電荷を放出する不揮発性メモリ素子のソース端子、ドレイン端子、及び制御ゲートに電位を印加することにより行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置を提供することを目的とする。

【解決手段】一対の不純物領域の間にチャネル形成領域を形成する半導体基板と、その上層部に、第1の絶縁層、浮遊ゲート電極、第2の絶縁層、制御ゲート電極を設ける。浮遊ゲート電極は少なくとも二層構造とし、第1の絶縁層に接する第1の浮遊ゲート電極は、半導体基板のバンドギャップより小さいことが好ましい。また、第2の浮遊ゲート電極は、金属材料若しくは合金材料又は金属化合物材料で形成されていることが好ましい。半導体基板のチャネル形成領域の伝導帯の底のエネルギーレベルより、浮遊ゲート電極の伝導帯底のエネルギーレベルを低くすることにより、キャリアの注入性を向上させ、電荷保持特性を向上させるためである。

(もっと読む)

不揮発性半導体記憶装置のベリファイ方法

【課題】低消費電力の不揮発性半導体記憶装置を提供する。

【解決手段】直列に接続された複数の不揮発性メモリ素子を有する不揮発性半導体記憶装置であって、前記不揮発性メモリ素子は互いに離間して形成された一対の不純物領域の間にチャネル形成領域を有する半導体層と、前記半導体層の上層部であって、前記チャネル形成領域と略重なる位置に、第1の絶縁層、浮遊ゲート、第2の絶縁層、制御ゲートとを有し、前記不揮発性メモリ素子へのデータの書き込み、消去、第1の読み出し及びベリファイ機能における第2の読み出しは当該不揮発性メモリ素子の制御ゲートに印加される電圧を変化させることにより行われ、前記消去に伴うベリファイ機能における第2の読み出しは前記複数の不揮発性メモリ素子のうち選択された前記不揮発性メモリ素子の制御ゲートの電位のみを変動することにより行われ、当該電位には第1の読み出し電位とは異なる電位を供給する。

(もっと読む)

半導体装置の製造方法

【課題】 二重露光を用いて微細化を図れる半導体装置の製造方法を提供すること。

【解決手段】 第1のパターンを含むメモリセル領域と、第2のパターンを含む周辺回路領域を備えた半導体装置を製造する際に、メモリセル領域と周辺回路領域を含む基板の領域上にレジスト膜を形成し、メモリセル領域上のレジスト膜中に第1のパターンに対応した潜像を形成するための第1の露光と、周辺回路領域上のレジスト膜中に第2のパターンに対応した潜像を形成するための第2の露光を含む多重露光により、レジスト膜を露光する際に、レジスト膜上における第1の露光と第2の露光の境界領域12を、ガードリング5,7間の素子分離領域10’上に設定し、レジスト膜を現像してレジストパターンを形成し、レジストパターンをマスクにして被加工基板をエッチングする。

(もっと読む)

不揮発性メモリ装置及びその製造方法

【課題】不揮発性メモリ装置を提供する。

【解決手段】半導体基板内に形成されたソース領域と、ソース領域と一部オーバーラップされるように形成されたゲート絶縁膜と、ソース領域とオーバーラップされる領域で電界を一定に形成させる構造を有し、ゲート絶縁膜の上部に形成されたフローティングゲートと、フローティングゲートの上部からフローティングゲートの一側壁に沿って絶縁されて形成されたコントロールゲートと、フローティングゲートとコントロールゲートとの間に介在されたゲート間絶縁膜及びコントロールゲートの他側と隣接して形成されたドレイン領域とを含む。

(もっと読む)

不揮発性メモリ装置およびその駆動方法

【課題】メモリセルあたりの面積が更に縮小されたスプリット・ゲートセルを実現する。

【解決手段】表面部に二つの不純物拡散層である第1拡散層と第2拡散層とが配置された半導体基板と、第1拡散層と第2拡散層との間の領域に配置される二つの電荷蓄積層であって前記半導体基板と第1絶縁膜を介して配置される第1の電荷蓄積層および第2絶縁膜を介して配置される第2の電荷蓄積層と、第1の電荷蓄積層に隣接して配置され第1の電荷蓄積層の電位を制御し得る第1の制御ゲート電極と、第2の電荷蓄積層に隣接して配置され第2の電荷蓄積層の電位を制御し得る第2の制御ゲート電極と、第1の制御ゲート電極と第2の制御ゲート電極とに隣接して配置され前記半導体基板と第3絶縁膜を介して配置される補助ゲート電極とを単位とし第1の電荷蓄積層側と第2の電荷蓄積層側の二つのメモリセルを有するメモリセル対を1以上直列に配置してなることを特徴とする直列配置メモリ装置。

(もっと読む)

分子トランジスタおよびその製造方法、並びにそれを用いた不揮発性メモリおよび圧電センサ

【課題】電流ヒステリシスが低減された分子トランジスタおよびその製造方法、並びにそれを用いた不揮発性メモリおよび圧電センサを提供する。

【解決手段】シリコン酸化膜14と、シリコン酸化膜14上に形成されたカーボンナノチューブ15と、カーボンナノチューブ15を両者の間に挟むように配置されたソース電極13およびドレイン電極12と、カーボンナノチューブ15の導通を制御するゲート電圧をカーボンナノチューブ15に印加するためのシリコン基板11とを備える分子電界効果トランジスタ10において、シリコン酸化膜14上に、シリコン酸化膜14表面に化学的に結合した自己組織化単分子膜16を形成し、カーボンナノチューブ15上に有機強誘電体層17を形成し、自己組織化単分子膜16と有機強誘電体層17との間にカーボンナノチューブ15を挟持する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 ゲート電極の側壁部に電荷蓄積部を配置してなる不揮発性メモリセルにおいて、アライメントずれによる特性バラツキを抑制し、メモリセル面積の縮小化を図る。

【解決手段】 半導体基板2上に形成されたゲート絶縁膜5、ゲート絶縁膜5上に形成されたゲート電極6、ゲート電極6の行方向の両側壁部に形成された電荷蓄積部7、ゲート電極6と電荷蓄積部7の下方に位置するチャネル領域3、及び、チャネル領域3の行方向に両側の半導体基板2表面に埋め込み拡散層で形成された2つの拡散層領域4を備え、行方向に隣接する2つのメモリセルのゲート電極6が、2つの拡散層領域4と電荷蓄積部7の上方を通過して相互に接続して行方向に延伸するゲート電極配線6aを形成し、2つの拡散層領域4がゲート電極配線6aの下方に位置し、列方向に隣接する2つのメモリセルの各拡散層領域4が相互に接続して、列方向に延伸する埋め込み拡散配線4aを形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 ゲート電極の側壁部に電荷蓄積部を配置してなる不揮発性メモリセルにおいて、アライメントずれによる特性バラツキを抑制し、書き込み時間の短縮を図る。

【解決手段】 半導体基板2上に形成されたゲート絶縁膜5とトンネル絶縁膜8、ゲート絶縁膜5上に形成されたゲート電極6、ゲート電極6の行方向の両側壁部のトンネル絶縁膜8上に半導体基板2の表面と平行な平板状に形成された電荷蓄積部7、ゲート電極6と電荷蓄積部7の下方に位置するチャネル領域3、及び、チャネル領域3の行方向に両側の半導体基板2表面に埋め込み拡散層で形成された2つの拡散層領域4を備え、行方向に隣接する2つのメモリセルのゲート電極6が、2つの拡散層領域4と電荷蓄積部7の上方を行方向に延伸するゲート電極配線6aで相互に接続され、ゲート電極配線6aはその下面が電荷蓄積部7の上面と絶縁膜を介して近接するように形成されている。

(もっと読む)

溝に横方向第1ゲート及び縦方向第2ゲートを含むスプリットゲート記憶装置

スプリットゲート記憶装置には、第1ゲート誘電体に接触した第1ゲート電極と、第2ゲート誘電体に接触した第2ゲート電極とが含まれる。第1拡散領域は、半導体基板中に画成された溝(108)の一部の下に横たわり、第2拡散領域は、基板(102)の上部を占有する。第1ゲート誘電体(110)は、溝を内張りする。第1及び第2ゲート誘電体の内の1つには、一層の不連続記憶素子(DSE)(120)が含まれ、第1及び第2ゲート電極の内の1つは、少なくとも部分的に溝内に配置される。一事例では、第1ゲート電極は制御ゲートであり、第1誘電体は一層のDSEを含む。他の事例では、第1ゲート電極は選択ゲートであり、第2誘電体は一層のDSEを含む。第2ゲート誘電体は基板の上面全体に横たわる。  (もっと読む)

(もっと読む)

121 - 140 / 150

[ Back to top ]