Fターム[5F101BD40]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | 基体材料 (372) | 3、5族 (150)

Fターム[5F101BD40]に分類される特許

101 - 120 / 150

不揮発性メモリを搭載する半導体装置および不揮発性半導体記憶装置の製造方法

【課題】工程数の増大を抑制しつつ、捕獲させた電荷を安定して保持させることが可能な不揮発性半導体記憶装置を提供する。

【解決手段】選択トランジスタTr1およびメモリトランジスタTr2を半導体基板1上に横方向に並べて形成することでFAMOSを構成し、メモリトランジスタTr2のフローティングゲート電極5cは、選択トランジスタTr1のサイドウォール5a、5bに使用されているのと同一のシリコン窒化膜から構成する。

(もっと読む)

半導体デバイス上に共形酸化物層を形成するための方法

半導体基板上に酸化物層を形成するための方法及び装置を開示する。1つ又は複数の実施形態では、半導体基板の温度を約100℃未満に制御することによって、プラズマ酸化を使用して、共形酸化物層を形成することができる。1つ又は複数の実施形態による半導体基板の温度を制御するための方法は、静電チャックならびに冷却剤及びガス対流を利用することを含む。  (もっと読む)

(もっと読む)

積層構造の不揮発性メモリ装置、メモリカード及び電子システム

【課題】積層構造のセルアレイと周辺回路との配置及び連結とを単純化して、集積度を高めた積層構造の不揮発性メモリ装置、メモリカード及びシステムを提供する。

【解決手段】不揮発性メモリ装置は、基板を含む。積層NANDセルアレイは、基板上に垂直に積層された複数のNANDストリングを含む少なくとも1つのNANDセットと、少なくとも1本の信号ラインとを有する。少なくとも1本の信号ラインは、少なくとも1つのNANDセットに共通結合するように、基板上に配される。

(もっと読む)

集積されたhigh−k誘電体と金属ベースの制御ゲートを有するフラッシュセル

集積されたhigh-k誘電層と金属制御ゲートを有する半導体デバイスが記載されている。当該半導体デバイスの製造方法が記載されている。当該半導体デバイスの実施例は、浮遊ゲート上に設けられたhigh-k誘電層を有する。前記high-k誘電層は凹部を画定する。前記凹部内に金属制御ゲートが形成される。  (もっと読む)

(もっと読む)

導電物質を形成する方法、導電物質を選択的に形成する方法、プラチナを形成する方法、及び、導電構造を形成する方法

導電物質を選択的に形成する方法及び金属導電構造を形成する方法を開示する。下部に横たわる物質領域を露出するように有機物質をパターン化することができる。下部に横たわる物質の上に位置する有機物質の残留部分と反応することなく下部に横たわる物質と反応するプラチナ前駆ガス等の前駆ガスに、下部に横たわる物質を晒してもよい。前駆ガスを原子層蒸着処理に用いてもよく、その間、前駆ガスは導電構造を形成するように下部に横たわる物質と選択的に反応して有機物質とは反応しない。導電構造は、例えば、半導体デバイス製造の様々な段階においてパターニング用マスクとして用いることができる。 (もっと読む)

窒化シリコン電荷トラップ層を有する不揮発性メモリ

フラッシュメモリデバイス及びフラッシュメモリデバイスを形成する方法を提供する。1つのバージョンでは、フラッシュメモリデバイスは、炭素、ホウ素、又は酸素を含むドーパントを有するドープト窒化シリコン層を含む。ドープト窒化シリコン層は、層中に発生する窒素ダングリングボンド及びシリコンダングリングボンドの数及び濃度を増大させ、不揮発性メモリデバイスのユニットセルの電荷保有能力及び電荷保持時間を増加させる。  (もっと読む)

(もっと読む)

スプリットゲート・メモリセルの形成方法

方法は、半導体基板(12)上にゲート材料の第一層(18)を形成すること、第一層上にハードマスク層(20)を形成すること、開口(22)を形成すること、ハードマスク層上と開口内とに電荷蓄積層(24)を形成すること、電荷蓄積層上にゲート材料の第二層(26)を形成すること、ハードマスク層を被覆している、第二層の一部と電荷蓄積層の一部とを除去することであって、第二層の第二部分が開口内に残存している、除去すること、ハードマスク層上と第二部分上とに、第一ビットセル及び第二ビットセルの両方を画定するパターン化されたマスク層(28、30、32)を形成すること、パターン化されたマスク層を用いて第一ビットセル及び第二ビットセルを形成することを含み、第一ビットセル及び第二ビットセルはそれぞれ、第一層から形成された選択ゲート(38、40)と、第二層から形成された制御ゲート(34、36)とを含む。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】高耐圧トランジスタのオフ時のリーク電流を抑制し、周辺回路内部の電圧を安定化することが可能な、NAND型フラッシュメモリ等に適用される半導体記憶装置を提供する。

【解決手段】周辺回路領域PRにおいて、シリコン基板11の一部にシリコンよりバンドギャップの広いSiCやGaN等の半導体層14が形成されている。メモリセル13は、シリコン基板11内に形成されている。周辺回路を構成するトランジスタ15は半導体層14内に形成されている。半導体層14のバンドギャップは、シリコンのバンドギャップより広いため、トランジスタ15がオフ状態において、トンネル電子が発生しない。このため、GIDLの発生を抑制することができる。

(もっと読む)

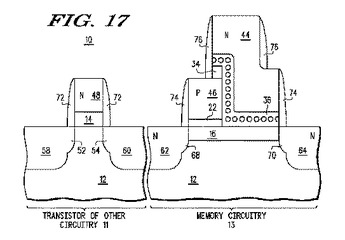

スプリット・ゲート・メモリ・デバイスの形成方法および装置

スプリット・ゲート・メモリ・デバイス(10)は、第1の仕事関数を有する選択ゲート(46)を基板(12)の第1の部分の上に有する。第2の仕事関数を有する制御ゲート(44)は、第1の部分に隣接する基板の第2の部分の上にある。スプリット・ゲート・メモリ・デバイス(10)の多数キャリアが電子であるとき、第1の仕事関数は第2の仕事関数よりも大きい。スプリット・ゲート・メモリ・デバイス(10)の多数キャリアがホールであるとき、第1の仕事関数は第2の仕事関数よりも小さい。基板(12)内の第1の電流電極(62)および第2の電流電極(64)は、制御ゲートおよび選択ゲートの下にあるチャネルによって分離される。制御ゲートおよび選択ゲートの異なる仕事関数は、デバイス性能を最適化するために各ゲートに対して異なる閾値電圧をもたらす。nチャネルデバイスでは、選択ゲートはp導電型であり、制御ゲートはn導電型である。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル当たり2ビットを記憶可能な不揮発性半導体記憶装置を提供することを課題とする。

【解決手段】半導体基板の表面層に備えられたチャネル領域を挟む一対の不純物拡散領域と、チャネル領域上に備えられたゲート絶縁膜をチャネル長方向で挟む一対の電荷保持膜と、ゲート絶縁膜及び一対の電荷保持膜上に備えられた単一層からなるゲート電極とを含むメモリセルを、チャネル長方向及びチャネル幅方向のそれぞれに少なくとも2つずつ隣接して有し、チャネル長方向に隣接するメモリセル間の不純物拡散領域が、隣接するメモリセルで共有され、チャネル長方向に隣接するメモリセルのゲート電極上に、チャネル長方向に隣接するメモリセルで共有されるワード線を備え、一対の不純物拡散領域が、チャネル幅方向で隣接するメモリセルにおいてそれぞれビット線として共有された不揮発性半導体記憶装置により上記課題を解決する。

(もっと読む)

NAND型不揮発性半導体メモリ装置およびその製造方法

【課題】アルミニウム酸化物膜をブロック絶縁膜とする高性能なMONOS型のNAND型不揮発性半導体メモリ装置およびその製造方法を提供する。

【解決手段】半導体基板に、直列接続された複数のメモリセルトランジスタと、選択トランジスタを備えるNAND型不揮発性半導体メモリ装置である。メモリセルトランジスタは、半導体基板上の第1の絶縁膜102aと、電荷蓄積層104と、アルミニウム酸化物である第2の絶縁膜106aと、第1の制御ゲート電極108aと、第1のソース/ドレイン領域を有する。選択トランジスタは、半導体基板上の第3の絶縁膜102bと、アルミニウム酸化物であり、4価カチオン元素、5価カチオン元素、N(窒素)のうち少なくとも1種の元素を含有する第4の絶縁膜106bと、第2の制御電極108bと、第2のソース/ドレイン領域を有する。

(もっと読む)

不揮発性半導体メモリ装置およびその製造方法

【課題】電荷トラップ量の大きな電荷蓄積膜を有する高性能なMONOS型の不揮発性半導体メモリ装置およびその製造方法を提供する。

【解決手段】半導体基板上のトンネル絶縁膜と、トンネル絶縁膜上の電荷蓄積膜と、電荷蓄積膜上のブロッキング絶縁膜と、ブロッキング絶縁膜上の制御ゲート電極と、制御ゲート電極の両側の半導体基板に形成されるソース/ドレイン領域を備え、電荷蓄積膜が、少なくともシリコン窒化膜と、シリコン窒化膜上のLaおよびSiを含む絶縁膜を備えることを特徴とする不揮発性半導体メモリ装置およびその製造方法。

(もっと読む)

半導体装置の作製方法

【課題】より高集積化され、薄型化及び小型化された半導体装置を作製することを目的の一とする。また、半導体装置において、高性能化、低消費電力化を目的の一とする。

【解決手段】剥離層を用いて基板から剥離された半導体素子層を、他基板に形成され、平坦化された無機絶縁層に覆われた半導体素子層上に積層する。上層の半導体素子層を基板より剥離後、剥離層を除去し半導体素子層下に形成される無機絶縁膜を露出する。平坦化された無機絶縁層及び無機絶縁膜を密着させて接合する。また、半導体素子層の有する半導体層は半導体基板より分離され、作製基板に転置された単結晶半導体層である。

(もっと読む)

半導体強誘電体記憶デバイスの製造方法

【課題】実用化が可能である程度の期間データを保持することのできる半導体強誘電体記憶デバイスの製造方法を提供できるようにすること。

【解決手段】ソース領域とドレイン領域を有する半導体基板または半導体領域上に、ハフニウム・アルミニウム酸化物を主成分とする絶縁体バッファ層、強誘電体膜およびゲート電極がこの順に積層されているトランジスタを有する半導体強誘電体記憶デバイスの製造方法であって、半導体表面処理、絶縁体バッファ層形成、強誘電体膜形成、ゲート電極形成および熱処理工程を含み、前記絶縁体バッファ層形成を、窒素と酸素のモル比が1:1〜1:10-7の混合ガスの雰囲気中にて行うことを特徴とする半導体強誘電体記憶デバイスの製造方法。

(もっと読む)

半導体強誘電体記憶デバイスの製造方法

【課題】実用化が可能である程度の期間データを保持することのできる半導体強誘電体記憶デバイスの製造方法を提供できるようにすること。

【解決手段】ソース領域とドレイン領域を有する半導体基板または半導体領域上に、ハフニウム酸化物を主成分とする絶縁体バッファ層、強誘電体膜およびゲート電極がこの順に積層されているトランジスタを有する半導体強誘電体記憶デバイスの製造方法であって、半導体表面処理、絶縁体バッファ層形成、強誘電体膜形成、ゲート電極形成および熱処理工程を含み、前記絶縁体バッファ層形成を、窒素と酸素のモル比が1:1〜1:10-7の混合ガスの雰囲気中にて行うことを特徴とする半導体強誘電体記憶デバイスの製造方法。

(もっと読む)

半導体デバイスの低温酸化のための方法

【課題】 半導体基板上に酸化物層を製造する方法の提供。

【解決手段】 ある実施形態において、半導体基板上に酸化物層を形成する方法は、プラズマリアクタの真空チャンバ内で基板支持体上に酸化すべき基板を載置するステップであって、チャンバが基板支持体から遠隔のイオン発生領域を有する、前記ステップと;チャンバにプロセスガスを導入するステップであって、プロセスガスが水素(H2)と酸素(O2)の少なくとも一つ - 約3:1までの水素(H2)と酸素(O2)の流量比で示される - 又は水蒸気(H2O蒸気)を含む、前記ステップと;チャンバのイオン発生領域に誘導結合プラズマを生成させて、基板上に酸化シリコン層を形成するステップと;を含む。

(もっと読む)

半導体デバイスの製造方法およびそれによって得られる半導体デバイス

基板(4)上に半導体デバイスを製造する方法は、基板(4)のメモリ領域(1)に不揮発性メモリ(10)を形成することを含む。基板(4)への不揮発性メモリ形成は、メモリ領域(1)に、浮遊ゲート構造と、制御ゲート構造とを形成することを含む。制御ゲート構造は、浮遊ゲート構造とともに積層型構造に位置する。1以上のゲート材料層は、基板(4)の論理領域(3)に形成される。制御ゲート構造とゲート材料層の形成後、充填材料層(130、130’)は論理領域(3)とメモリ領域(1)に堆積される。論理領域(3)とメモリ領域(1)に位置する充填材料の厚さを、1以上のゲート材料層の表面が少なくとも露出するまで薄くすることによって、充填材料層(130、130’)は除去される。論理デバイスは論理領域(3)に形成され、論理デバイスの形成は、ゲート材料層から論理ゲート構造を形成することを含む。  (もっと読む)

(もっと読む)

不揮発性メモリデバイス用インターポリ誘電体を形成するための統合スキーム

【課題】 不揮発性メモリデバイスの漏れ電流を維持するか又は減少させつつ、デバイス寸法の減少を可能にする電子デバイス及び電子デバイスを形成する方法の提供。

【解決手段】 一実施形態において、不揮発性メモリデバイスを製造する方法は、基板上にフローティングゲート多結晶層を堆積させるステップと、フローティングゲート多結晶層上に酸化シリコン層を形成するステップと、酸化シリコン層上に第一酸窒化シリコン層を堆積させるステップと、第一酸窒化シリコン層上に高k誘電物質を堆積させるステップと、高k誘電物質上に第二酸窒化シリコンを堆積させるステップと、第二酸窒化シリコン層上に制御ゲート多結晶層を形成するステップとを含む。一実施形態において、高k誘電物質層は、酸窒化シリコンハフニウムを含む。

(もっと読む)

電荷蓄積構造

【課題】 低い電圧でデータ格納が可能なセミコンダクタ・オン・インシュレータタイプの構造及びその製造プロセスを提供する。

【解決手段】 本発明は、ドナー基板(10)の半導体層(11)と、絶縁体層(60)と、レシーバ基板(20)とを備えるセミコンダクタ・オン・インシュレータタイプの構造において、レシーバ基板(20)上にドナー基板(10)を接合するステップを備え、基板の少なくとも1つが絶縁体層でコーティングされる、セミコンダクタ・オン・インシュレータタイプの構造の製造プロセスであって、電荷キャリアを保持するのに適切な電気的に活性なトラップを備える、いわゆる、トラップ界面(30)を接合界面に形成するステップを備えることを特徴とする、製造プロセスに関する。また、本発明は、トラップ界面を備えるセミコンダクタ・オン・インシュレータタイプの構造に関する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】寄生容量を低減化,カップリング容量比を向上し、書き込み/消去電圧を低圧化できる。

【解決手段】pウェル領域2と、n+領域5と6間のウェル領域に跨ってゲート絶縁膜12を介して形成された選択ゲート電極(SG)と、n+領域6と接するドレイン電極Dとからなる選択トランジスタと、n+領域1と、n+領域5と電気的に接続し、n+領域1と離間するn+領域4と、n+領域1の上のトンネル絶縁膜8と、n+領域1からn+領域4の上面に跨って形成されたゲート絶縁膜12と、ゲート絶縁膜よりも厚い選択絶縁膜10と、トンネル絶縁膜,ゲート絶縁膜,および選択絶縁膜上のフローティングゲート電極(FG)と、選択絶縁膜上に形成され、FGと側方で対向して形成されたコントロールゲート電極(CG)とからなるメモリトランジスタと、選択絶縁膜を挟んでFGと対向するフローティングのn+領域1が形成される不揮発性半導体記憶装置および製造方法。

(もっと読む)

101 - 120 / 150

[ Back to top ]