Fターム[5F101BF02]の内容

不揮発性半導体メモリ (42,765) | 動作 (2,287) | 特性ヒステリシスしきい値 (921) | 記憶保持 (529)

Fターム[5F101BF02]に分類される特許

201 - 220 / 529

半導体装置の駆動方法

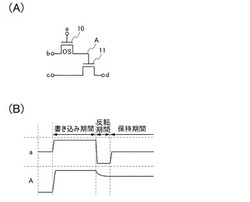

【課題】酸化物半導体層によってチャネル領域が形成されるトランジスタのソース及びドレインの一方に電気的に接続されたノードにおいて電荷の保持を行う半導体装置に記憶された情報の経時変化を抑制すること。

【解決手段】書き込み期間と保持期間の間に、トランジスタのゲートに強い負電位を与える期間(反転期間)を設ける。反転期間において、当該トランジスタのドレインから酸化物半導体層に対する正電荷の供給が促進される。これにより、酸化物半導体層内又は酸化物半導体層及びゲート絶縁膜の界面への正電荷の蓄積を短期間で収束させることができる。そのため、反転期間後の保持期間における当該トランジスタのドレインに電気的に接続されたノードにおける正電荷の減少を抑制することが可能である。すなわち、当該半導体装置に記憶された情報の経時変化を抑制することが可能である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルに書き込み用のトランジスタ、読み出し用のトランジスタおよび選択用のトランジスタを備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】不揮発性メモリと容量素子を有し、性能を向上させる半導体装置を提供する。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MG6nとp型ウエルPW1との間および制御ゲート電極CG4nとメモリゲート電極MG6nとの間には、内部に電荷蓄積層5bを有する絶縁膜5が形成されている。この絶縁膜5は、酸化シリコン膜5aと、その上に形成された窒化シリコン膜5bと、その上に形成された酸化シリコン膜5cと、その上に形成されかつ酸化シリコン膜5cよりも薄い絶縁膜5dとの積層膜からなる。この絶縁膜5dは、ポリシリコンからなるメモリゲート電極MG6nに接している。絶縁膜5dは、Hf,Zr,Al,Ta,Laのうちの少なくとも1種を含む金属化合物により形成されているため、フェルミピニングを生じることができ、誘電率が高い。

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】電磁波又は光が照射されても広義のリーク電流が増大せず、書き込み状態及び消去状態の安定した判別を可能とする。

【解決手段】電磁波シールド性能及び遮光性能を持つ層30及び31のどちらにも半導体層60の領域面積よりも大きい領域面積を持たせ、且つこの層30及び31を、半導体層60の上下を挟み込むように設けることで、電磁波及び光が半導体層60に侵入することを防ぐことができる。この結果、広義のリーク電流が格段に低減され、書き込み状態及び消去状態の判別を安定して行うことができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】各メモリセルの書込消去特性を極力一定にできる不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルトランジスタMTは、活性領域Saが素子分離溝2によって互いに分離している。これらのメモリセルトランジスタMTは、それぞれ、活性領域Saの上面上または上方にトンネル絶縁膜3を介して電荷蓄積機能を有する電荷トラップ膜4を備えている。積層絶縁膜Bは、トンネル絶縁膜3および電荷トラップ膜4を少なくとも含んで構成され、トンネル絶縁膜3が素子分離溝2の内面に沿って形成されると共に電荷トラップ膜4がトンネル絶縁膜3の上面に沿って積層されており、素子分離溝2内の全領域に埋込まれている。

(もっと読む)

半導体記憶素子、及び半導体記憶装置

【課題】 高効率に電荷を蓄積及び消去することができ、かつ蓄積した電荷を長時間保持することができる半導体記憶素子、及び半導体記憶装置を提供する

【解決手段】 半導体層19と、半導体層19上に設けられたトンネル絶縁膜18と、トンネル絶縁膜18上に設けられ、膜厚が0.9nm以上2.8nm以下であり、立方晶ハフニア粒子17を含む電荷蓄積膜16と、電荷蓄積膜16上に設けられたブロック絶縁膜15と、ブロック絶縁膜15上に設けられた制御電極13とを備えることを特徴とする半導体記憶素子。

(もっと読む)

不揮発性半導体メモリ、及び不揮発性半導体メモリへの書込み方法

【課題】不揮発性半導体メモリの周辺回路を小さくし、集積回路の縮小化に寄与する。

【解決手段】p型基板10に形成され、ソース線430と接続するn型拡散層50と、p型基板10上に設けられ、ワード線400と接続するワード電極200と、p型基板10とワード電極200の間に設けられたワード絶縁層と、n型拡散層50上、及びワード電極200の側壁に設けられたトンネル絶縁層と、トンネル絶縁層上に設けられた電荷蓄積層と、電荷蓄積層上に設けられたコントロール絶縁層と、コントロール絶縁層上に設けられ、コントロール線420と接続するコントロール電極300と、を備え、制御部は、メモリ素子600に書込みを行うときに、ソース線430に正電圧を印加し、ワード線400に負電圧を印加し、かつコントロール線420に正電圧を印加する不揮発性半導体メモリ。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図ることを目的の一つとする。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根(RMS)粗さが1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、および絶縁層表面の一部とドレイン電極表面との高低差は、5nm以上の半導体装置である。

(もっと読む)

不揮発性半導体記憶装置

【課題】電荷蓄積層をもち、電荷のトラップを利用する記憶素子の保持特性を向上させる技術を提供する。

【解決手段】電荷蓄積層(24)の上のメモリゲート(21)と、第1サイドゲート(22)と、第2サイドゲート(23)と、第1サイドゲート(22)側の第1不純物注入領域(31)と、第2サイドゲート(23)側の第2不純物注入領域(32)と、チャネル領域(33、34、35)とを具備する不揮発性半導体記憶装置を構成する。チャネル領域(33、34、35)は、電荷蓄積層(24)の下の第1領域(33)と、第1領域(33)と第1不純物注入領域(31)との間のセレクト側領域(34)と、第1領域(33)と第2不純物注入領域(32)との間のアシスト側領域(35)とを含むことが好ましい。そして、ゲート長方向におけるセレクト側領域(34)の長さ(L1)は、アシスト側領域(35)の長さ(L2)よりも長いものとする。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さ(RMS)が1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、または絶縁層表面の一部とドレイン電極表面との高低差は、5nm未満の半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】電荷を蓄積可能な電荷蓄積膜を有する不揮発性メモリセルを含む半導体装置において、データ保持特性劣化を改善し、その信頼性を向上させることにある。

【解決手段】半導体基板の主面に不揮発性メモリセルを含む半導体装置であって、不揮発性メモリセルは、半導体基板上に第1絶縁膜と、導電膜と、第2絶縁膜と、電荷を蓄積可能な電荷蓄積膜とを有する。また、電荷蓄積膜上に第3絶縁膜と、第1ゲート電極と、第1絶縁膜から前記第1ゲート電極までの一連の積層膜と接するように第4絶縁膜と、第1絶縁膜と並ぶように前記半導体基板上に第5絶縁膜とを有する。さらに、第5絶縁膜上に形成され、第4絶縁膜の側面に前記第1ゲート電極と隣り合うように第2ゲート電極と、第1ゲート電極と第2ゲート電極を挟むように半導体基板にソース領域およびドレイン領域とを有する。半導体装置は、導電膜と電荷蓄積膜が平面的に重なり合うように形成されている。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】メモリセルアレイの耐ストレス性を向上できるようにする。

【解決手段】局所選択ゲート電極CSGが、部分的にメモリセルトランジスタMTを選択(例えばメモリセルトランジスタMT0〜MT7)することで、その他のメモリセルトランジスタMT(例えばメモリセルトランジスタMT8〜MT63)を非選択状態にすることができ、当該非選択状態とされたメモリセルトランジスタMTに高電圧を与える必要がない。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。また、量産性の高い半導体装置を提供することを課題の一とする。また、量産性の高い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すれば良い。具体的には、酸化物半導体層にハロゲン元素を添加した後に加熱処理を施し、不純物を除去して使用すれば良い。ハロゲン元素としては、フッ素が好ましい。

(もっと読む)

不揮発性半導体記憶装置の製造方法、及び不揮発性半導体記憶装置

【課題】3次元的にトランジスタが配置された構成において、垂直方向に隣接するトランジスタの間隔を小さくした場合に、カップリング容量に起因したトランジスタの誤動作を低減できる不揮発性半導体記憶装置の製造方法、及び不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置の製造方法は、半導体基板の上に、第1の半導体膜と第2の半導体膜とが交互に複数回積層された積層膜における少なくとも複数の第2の半導体膜がゲート絶縁膜を介して半導体又は導電体の柱状部材によりそれぞれ保持された複数の構造を形成する形成工程と、前記形成工程で形成された前記複数の構造のそれぞれについて、前記複数の第2の半導体膜が前記柱状部材により保持された状態を維持しながら、前記積層膜から複数の前記第1の半導体膜を選択的に除去する除去工程と、前記除去工程を経た前記複数の構造のそれぞれにおける複数の前記第2の半導体膜の間に空洞を残すように、層間絶縁膜を埋め込む埋め込み工程とを備えている。

(もっと読む)

メモリセル電荷記憶素子あたりに二重のコントロールゲートを有するフラッシュメモリセルアレイ

【課題】フローティングゲートが少なくとも2つのコントロールゲートラインと容量的に結合するようになっているフラッシュNANDタイプのEEPROMシステムの提供。

【解決手段】コントロールゲートラインはフローティングゲートの側壁と結合するようにフローティングゲート間に位置し、メモリセルの結合比が望ましく高められる。フローティングゲートの選択された行の両側の両方のコントロールゲートラインは普通同じ電圧まで高められ、隣接するフローティングゲートの選択されていない行に結合された第2のコントロールゲートラインは低く保たれる。選択されたフローティングゲートの領域でその電圧を選択的に高めるために、コントロールゲートラインを基板と容量的に結合させる。フローティングゲートの長さとコントロールゲートラインの厚さとは、スペーサのエッチマスクを形成することによってプロセスの最小分解エレメントより小さくされ得る。

(もっと読む)

不揮発性半導体記憶装置

【課題】所定の動作の信頼性を向上する。

【解決手段】不揮発性半導体記憶装置は、第1ワード線WL0に接続された第1メモリセルと、前記第1ワード線に隣接する第2ワード線WL1に接続され、前記第1メモリセルと幅が異なる第2メモリセルと、を具備する。前記第1ワード線に第1電圧が印加され、前記第2ワード線に前記第1メモリセルの幅と前記第2メモリセルの幅との差に基づき補正された前記第1電圧と異なる第2電圧が印加される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの情報の書き込みは、書き込み用トランジスタをオン状態とすることにより、書き込み用トランジスタのソース電極(またはドレイン電極)と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタとして、しきい値電圧を正に制御したトランジスタを用いることで、読み出し電位を正の電位とする。

(もっと読む)

半導体装置の製造方法

【課題】良質な特性を有する半導体装置の製造方法を提供する。

【解決手段】制御ゲート電極202の表面に絶縁膜203を形成する工程と、絶縁膜203の表面に電荷蓄積層204を形成する工程と、電荷蓄積層204の表面にトンネル絶縁膜205を形成する工程と、トンネル絶縁膜205の表面にシリコン層206を形成する工程と、シリコン層206を形成した後、熱処理を行ってトンネル絶縁膜205及びシリコン層206の境界面近傍に存在する酸素とシリコンとを反応させる工程と、を備える。

(もっと読む)

201 - 220 / 529

[ Back to top ]