Fターム[5F101BG08]の内容

不揮発性半導体メモリ (42,765) | 応用 (153) | 製品情報記憶、シグニチャ (20)

Fターム[5F101BG08]に分類される特許

1 - 20 / 20

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】メモリ回路を含む半導体装置の低消費電力化を図ることを課題とする。

【解決手段】メモリ回路を含む半導体装置において、メモリ回路はワード線とビット線で規定される領域に設けられた半導体素子を有するメモリセルと半導体素子を有さないメモリセルを含み、該半導体素子には、酸化物半導体を用いて形成したオフ電流が極めて低いトランジスタを用いるため、読み出し精度が高まり、低電圧動作が可能となる。また、メモリセルは、ハイまたはローのいずれか一方のデータを記憶し、半導体素子を有するメモリセルは、前記データを構成するハイおよびローのうち、少ない方を記憶し、半導体素子を有さないメモリセルは、多い方を記憶する。

(もっと読む)

記憶装置、半導体装置

【課題】データの書き込み不良を抑えつつ、面積を小さく抑えることができる不揮発性の記憶装置、または当該不揮発性の記憶装置を用いた半導体装置の提供を目的の一とする。

【解決手段】不揮発性の記憶素子を有する第1の記憶部と、上記第1の記憶部へのデータの書き込みが正確に行われたかどうかを検証するベリファイ動作において、上記データを一時的に保存するための第2の記憶部(データバッファ)とを有する。そして、第2の記憶部が、記憶素子と、当該記憶素子における電荷の保持を制御するための、オフ電流またはリーク電流が極めて小さい絶縁ゲート電界効果型トランジスタとを有する。

(もっと読む)

半導体記憶装置

【課題】コストを増大させずとも、書き込みに高電圧を必要とせず、不良が発生しにくく、書き込み時間が短く、データの書換えができない半導体記憶装置を提供する。

【解決手段】ダイオード接続した第1のトランジスタと、ダイオード接続した第1のトランジスタのソース電極及びドレイン電極の一方の端子にゲートが接続する第2のトランジスタと、ダイオード接続した第1のトランジスタのソース電極及びドレイン電極の一方の端子及び第2のトランジスタのゲートに接続する容量素子を有するメモリ素子を含む半導体記憶装置である。

(もっと読む)

記憶装置

【課題】ロジック回路を増やすことなく、第三者がメモリセルにアクセスできずかつ必要な場合にはいつでもアクセス可能なメモリセルを有する記憶装置を提供する。

【解決手段】本実施形態は、第1のメモリセルと、第2のメモリセルと、を有し、第2のメモリセルに設けられた第2のトランジスタの第2のチャネルが酸化物半導体膜からなる記憶装置であって、第2のメモリセルからのデータの読み出しは第2のトランジスタに紫外線を照射している時に行われる記憶装置によって解決する。

(もっと読む)

不揮発性メモリを搭載する半導体装置および不揮発性半導体記憶装置の製造方法

【課題】工程数の増大を抑制しつつ、捕獲させた電荷を安定して保持させることが可能な不揮発性半導体記憶装置を提供する。

【解決手段】選択トランジスタTr1およびメモリトランジスタTr2を半導体基板1上に横方向に並べて形成することでFAMOSを構成し、メモリトランジスタTr2のフローティングゲート電極5cは、選択トランジスタTr1のサイドウォール5a、5bに使用されているのと同一のシリコン窒化膜から構成する。

(もっと読む)

不揮発性半導体記憶装置及びその作製方法

【課題】書き込みや消去を繰り返し行った場合であっても、読み出し不良を抑制することを目的の一とする。又は、メモリトランジスタの面積の増大を抑制しつつ、書き込み電圧、消去電圧を低減することを目的の一とする。

【解決手段】基板上に設けられた書き込み動作及び消去動作に用いる第1の半導体層及び読み出し動作に用いる第2の半導体層上に、絶縁膜を介してフローティングゲートとコントロールゲートを設け、第1の半導体層を用いてフローティングゲートへの電子の注入・放出を行い、第2の半導体層を用いて読み出しを行う。

(もっと読む)

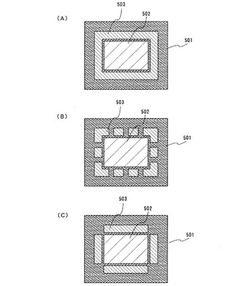

ICパッケージおよび通信機器

【課題】不揮発性メモリ等の書き込み状態を外観だけで認識できるICパッケージおよび通信機器を提供する。

【解決手段】ICパッケージ10に、データの書き換えが可能な記憶部11と、記憶部11の状態を検出する検出部12と、検出部12の検出結果に応じた報知を行う表示部14とを設ける。

(もっと読む)

半導体装置およびその作製方法

【課題】不揮発性メモリトランジスタの電荷保持特性を向上させる。

【解決手段】半導体基板と導電膜の間には、第1絶縁膜、電荷トラップ膜、第2絶縁膜が形成されている。電荷トラップ膜は水素濃度が低い上部領域と、水素濃度が高い下部領域を有する窒化シリコン膜でなる。このような窒化シリコン膜は、化学気相成長法により、水素を15atomic%以上含む窒化シリコン膜を形成し、その上部を窒化することで形成される。この窒化処理は、窒素ガスのプラズマ中に生成された窒素ラジカルで窒化シリコン膜を窒化することで行われる。

(もっと読む)

不揮発性記憶トランジスタおよびその製造方法

【課題】標準CMOSプロセスを用いて効率的なキャリア注入が可能な不揮発性記憶トランジスタを提供する。

【解決手段】サイドスペーサに電荷を注入してしきい値電圧を変化させることにより、データを記憶するN型の不揮発性記憶トランジスタを、ゲート絶縁膜の膜厚がI/Oトランジスタのゲート絶縁膜の膜厚と同じであり、チャンネル領域の不純物濃度がコアトランジスタと同じまたはそれよりも濃く、ドレイン側のLDD領域にチャンネル領域よりも濃度の濃いP型領域が形成され、且つ、ゲート電極用ポリシリコンがP型ポリシリコンであるトランジスタで構成した。

(もっと読む)

半導体装置及び半導体メモリテスト装置

【課題】動作用の電圧を供給するポンプ回路を各メモリチップから取り去り、ポンプチップとして別チップにしてMCPチップ内に同梱するようにして、メモリチップの出荷前試験を可能にする半導体装置を提供する。

【解決手段】本発明の一実施の形態に係る半導体装置は、複数の不揮発性半導体記憶装置と、前記複数の不揮発性半導体記憶装置を動作させる昇圧電圧を生成する昇圧回路と、前記複数の不揮発性半導体記憶装置の動作シーケンスに基づいて、前記昇圧回路における前記昇圧電圧の生成動作を制御する昇圧回路制御部と、を備える。

(もっと読む)

半導体装置及びその制御方法

【課題】データの読み出しまたは書き込み動作の安定性を向上させる。

【解決手段】メモリセル領域101内に設けられた複数のビットラインBLと、前記複数のビットラインBLに交差して設けられた複数のワードラインWLと、前記複数のワードラインWLに沿って設けられた複数の拡散ソースラインVSLと、前記複数のビットラインBL及び前記複数のワードラインWLが交差する交差部に設けられ、前記複数のビットラインBL、前記複数のワードラインWL、及び前記複数の拡散ソースラインVSLに接続された、データを格納する不揮発性の複数のアクティブセルACと、前記複数のアクティブセルACのうち、少なくとも2以上のアクティブセルACに対し、同時にデータの書き込みまたは読み出しを行う制御部と、を具備し、前記複数のアクティブセルACの数は、前記交差部の数よりも少ないことを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリのデータ保持特性を向上させる。

【解決手段】半導体基板1Sの主面には、主回路領域Nと、フラッシュメモリのメモリセルアレイMRとが配置されている。メモリセルアレイMRには情報電荷蓄積用の浮遊ゲート電極FGが配置され、主回路領域Nには主回路を構成するMIS・FETのゲート電極Gが配置されている。主回路領域Nには窒化シリコン膜からなる絶縁膜2aがゲート電極Gを覆うように形成されている。これにより、主回路領域Nにおける素子の微細化を維持できる。一方、メモリセルアレイMRには上記絶縁膜2aが形成されていない。すなわち、浮遊ゲート電極FGの上面は絶縁膜2aに接触することなく層間絶縁膜2bにより直接覆われている。これにより、メモリセルアレイMRにおける浮遊ゲート電極FGの電荷eのリークを抑制または防止できフラッシュメモリのデータ保持特性を向上させることができる。

(もっと読む)

半導体装置

【課題】半導体装置に設けられた不揮発性メモリ回路部の面積を小さくする。

【解決手段】フラッシュメモリの形成領域の半導体基板1Sのn型の埋込ウエルDNW内にp型のウエルHPW1〜HPW3を互いに分離した状態で設け、そのウエルHPW1〜HPW3にそれぞれ容量部C、データ書き込み・消去用の電荷注入放出部CWEおよびデータ読み出し用のMIS・FETQRを配置した。容量部Cは、データ書き込み・消去用の電荷注入放出部CWEとデータ読み出し用のMIS・FETQRとの間に配置した。データ書き込み・消去用の電荷注入放出部CWEでは、チャネル全面のFNトンネル電流によりデータの書き込みおよび消去を行う。

(もっと読む)

メモリデバイス分散型制御器システム

メモリデバイス分散型制御器回路は、メモリ制御機能を複数のメモリ制御器に分散する。マスター制御器は、解釈されたコマンドを受け取り、適切なスレーブ制御器をそのコマンドに応じて活性化する。スレーブ制御器は、データキャッシュ制御器とアナログ制御器を含んでもよく、データキャッシュ制御器は、データキャッシュに接続され、データキャッシュを制御し、また、アナログ制御器は、アナログ電圧生成回路に接続され、アナログ電圧生成回路を制御する。それぞれの制御器は、適切なソフトウェア/ファームウェア命令を有し、この命令は、受け取ったコマンドに応じてそれぞれの制御器がとる応答を決定する。 (もっと読む)

半導体装置およびその作製方法

【課題】コントロールゲート電極を形成する際の位置ずれの問題を起こさず自己整合的に形成し、さらにコントロールゲート電極とフローティングゲート電極間でリークを発生させない半導体装置及びその作製方法を提供する。

【解決手段】半導体膜と、前記半導体膜上の第1のゲート絶縁膜と、前記第1のゲート絶縁膜上のフローティングゲート電極と、前記フローティングゲート電極を覆った第2のゲート絶縁膜と、前記第2のゲート絶縁膜上のコントロールゲート電極と、を有し、前記コントロールゲート電極は、前記第2のゲート絶縁膜を介して前記フローティングゲート電極を覆うように形成され、前記コントロールゲート電極にはサイドウォールが形成され、前記サイドウォールは前記フローティングゲート電極によって生じた前記コントロールゲート電極の段差部分に形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】先端標準CMOSプロセスのLSIに混載可能な不揮発性半導体記憶装置に関し、消去速度の高速化を実現する。

【解決手段】フローティングゲート32に電荷を蓄積してデータを記憶する不揮発性半導体記憶装置であって、フローティングゲート32を共有する複数のMOSトランジスタ24,25,26を有し、書き込み時のカップリングにPMOS24を用い、消去時のカップリングにN型のデプレッションMOS(DMOS)25を用いることを特徴とし、書き込みにはPMOS24によるチャネル反転容量のカップリングを用い、消去にはN型DMOS25による空乏容量のカップリングを用いることで、従来の3トランジスタ型不揮発性メモリ素子に対して面積増加無く、消去速度を高速化する。

(もっと読む)

二重層フローティングゲートを備えているEPROMセル

EPROMセル(70)は、ソース領域(76)及びドレイン領域(74)を有する半導体基板(52)と、第1の金属層(60)と電気的に相互接続されている半導体ポリシリコン層(56)を含むフローティングゲート(72)と、第2の金属層を含むコントロールゲート(64)とを備えている。フローティングゲート(72)は、ソース領域(76)及びドレイン領域(74)に隣接して配置され、第1の誘電体層(54)によって半導体基板(52)から分離され、コントロールゲートの第2の金属層(64)は、第1の金属層(60)との間にある第2の誘電体層(62)を介して、第1の金属層(60)と容量結合されている。 (もっと読む)

集積回路装置及び電子機器

【課題】 耐圧確保のために、リード及び消去モードとプログラム時とで、メモリセルに接続されたトランスファーゲートを構成するP型及びN型MOSトランジスタの制御を変更でき、かつ、小面積化を達成できるサブワード線デコーダを搭載した集積回路装置及び電子機器を提供すること。

【解決手段】 メモリセルMCとビット線BLとの間に設けられた第1のトランスファーゲート240は、サブワード線デコーダSWDecに接続されたP型及びN型MOSトランジスタXfer(P,N)を有する。サブワード線デコーダは、第2及び第3のトランスファーゲート610,630と2つのトランジスタ600,620とを有する計6個のトランジスタから構成され、第2及び第3のトランスファーゲートの一方610のソースにカラムドライバCLDrvの出力線が接続され、第2及び第3のトランスファーゲートの他方630のソースに反転プログラム線XPGMを接続した。

(もっと読む)

埋め込みFeRAM基盤のRFIDを有する集積回路

集積回路(IC)100は、予め定められた動作を行うように構成された高静電容量固体回路領域、データを格納するFeRAMブロック104、及びICを無線で識別する外部的に提供された固有IDをRFIDブロックに伝達するように構成されたインタフェースユニットを備え、固有IDは、FeRAMブロックに格納される。ICは、ICの予め定められた領域を通して延長される導電性トレースを更に備え、導電性トレースは、RFIDブロックに対するアンテナとして構成され、ここで、RFIDブロックは、情報を受信し、アンテナを介して外部ソースに情報を伝達するように構成される。  (もっと読む)

(もっと読む)

1 - 20 / 20

[ Back to top ]