Fターム[5F102FA09]の内容

接合型電界効果トランジスタ (42,929) | 目的、効果 (2,241) | 試験、測定(製造中を含む) (43)

Fターム[5F102FA09]に分類される特許

1 - 20 / 43

評価方法

化合物半導体装置の製造方法、基板評価装置及び基板評価方法

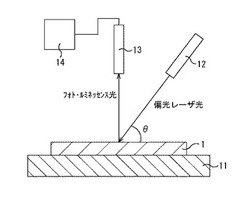

【課題】化合物半導体層を形成する前の基板の状態で非接触のスクリーニングを行うことで、事前に化合物半導体層の不良発生を認識してこれを防止することができ、歩留まりの向上及び製造コストの削減を可能とする信頼性の高い化合物半導体装置を得る。

【解決手段】偏光レーザ12によりSiC基板1の基板面に偏光レーザ光を照射し、検出部13によりSiC基板1からの発光を検出し、表示部14によりSiC基板1の発光強度の面内分布を得て、SiC基板1の窒素混入量を評価した後、SiC基板1の上方に化合物半導体積層構造2を形成する。

(もっと読む)

半導体装置の製造方法

【課題】チャージアップに起因するリーク電流及び閾値電圧の変動を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体層内に、活性領域30を含むFET34、活性領域30からなるスクライブライン36、FET34とスクライブライン36との間に位置する不活性領域32、及び不活性領域32を横断してFET34とスクライブライン36とを電気的に接続する接続領域38を設ける工程と、半導体層上に絶縁膜20を形成する工程と、ドライエッチング法により絶縁膜20に選択的に開口部21を形成する工程と、を有する半導体装置である。

(もっと読む)

半導体装置

【課題】裏面電極と導通したパッドを破ることなく、複数のバイアホールの検査を短時間で実施できる半導体装置を提供する。

【解決手段】半導体装置は、基板と、該基板の裏面に形成された裏面電極と、該基板を貫通するN個(Nは2以上の整数)のバイアホール16のそれぞれを経由して該裏面電極と電気的に接続されるように該基板の表面に形成されたN個のパッドと、該N個のパッドのそれぞれに電気的に接続されたN個のエピ抵抗30とを有する。そして、該N個のエピ抵抗を介して該N個のパッドと接続された配線34と、該配線と接続された検査用パッド36と、該N個のパッド、及び該N個のバイアホールを経由して該裏面電極に電流を流すように該基板の表面に形成された電流印加用パターンと、を備える。

(もっと読む)

半導体装置、半導体装置の製造方法、および試験装置

【課題】ゲートリーク電流が少なく、かつ電流コラプスが抑えられた半導体装置の提供。

【解決手段】第1の態様においては、窒化物系半導体で形成された半導体層110と、半導体層上に開口を有して設けられ、タンタル酸窒化物を含む第1絶縁膜120と、第1絶縁膜の開口において半導体層上に積層された第2絶縁膜130と、第2絶縁膜上に設けられたゲート電極140と、を備える半導体装置を提供する。ここで、第2絶縁膜は、第1絶縁膜より絶縁性が高い絶縁膜により構成される。

(もっと読む)

スイッチング素子及びこれを用いた電源装置

【課題】ソース電極とドレイン電極間の容量を低減し、スイッチングロスを減らすことができるスイッチング素子、及び該スイッチング素子を搭載した効率が向上した電源装置の提供。

【解決手段】Si基板1と、該Si基板1上に形成されたソース電極8及びドレイン電極9を有してなり、ソース電極8及びドレイン電極9の配置方向と直交する方向の層中であって、ソース電極8及びドレイン電極9のいずれか一方のみと接している領域に、p型領域とn型領域が接している部分24であるpn接合を少なくとも1つ有するスイッチング素子である。

(もっと読む)

半導体素子の検査方法及び半導体検査装置

【課題】電界効果トランジスタにおける電流コラプスの発生の有無を迅速に判定する。

【解決手段】電界効果トランジスタ101をオン状態にするとともに、電界効果トランジスタ101のドレインに第1電圧を印加した状態において、電界効果トランジスタ101の第1オン抵抗を算出する第1の工程と、電界効果トランジスタ101をオフ状態にし、前記第1電圧よりも大きい第2電圧を、電界効果トランジスタ101のドレインに印加する第2の工程と、電界効果トランジスタ101をオン状態にするとともに、電界効果トランジスタ101のドレインに前記第2電圧を印加した状態において、電界効果トランジスタ101の第2オン抵抗を算出する。

(もっと読む)

半導体装置、試験装置、および製造方法

【課題】電流電圧のパルス特性を向上させて電流電圧のDC特性に近づける。

【解決手段】半導体層と、半導体層上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、ゲート絶縁膜上に設けられ、ゲート絶縁膜上におけるゲート電極の端部の少なくとも一部においてゲート電極と接するゲート境界膜と、を備え、ゲート境界膜およびゲート絶縁膜は、同種の絶縁材料を含む半導体装置を提供する。ゲート電極およびゲート境界膜上に設けられた絶縁性の保護膜を更に備え、保護膜は、ゲート境界膜およびゲート絶縁膜とは別種の絶縁材料を含んでよい。

(もっと読む)

III−V族化合物半導体エピタキシャルウェハ及びその製造方法

【課題】オン抵抗やリーク電流を低減したIII−V族化合物半導体エピタキシャルウェハを提供する。

【解決手段】単結晶基板上に、少なくとも、GaAs層、AlGaAs層からなるバッファ層、InGaAs層からなるチャネル層、n型不純物を含有するAlGaAs層又はInGaP層若しくはSiプレナードープ層からなる電子供給層、ノンドープ又は低濃度n型不純物を含有するAlGaAs層からなるショットキー層、Se又はTeをドーパントとしたn型不純物を含有するInxGa(1-x)As層(但し0<x<1)からなるコンタクト層を積層したHEMT構造を有するIII−V族化合物半導体エピタキシャルウェハにおいて、その表面清浄度検査におけるHaze値が500ppm以下であるものである。

(もっと読む)

半導体装置及びこれを用いた電気回路、電気回路の制御方法

【課題】消費電力を増大させずにオンチップでHEMTの動作状況をモニターする。

【解決手段】

この半導体装置10においては、第1の半導体層である電子走行層11上に、第2の半導体層である電子供給層12が形成されている。これらの界面(ヘテロ接合界面)における電子走行層側に、2次元電子ガス(2DEG)層13が形成される。この半導体装置10において、電子は、電子供給層12の表面に形成された第1の主電極であるソース電極14と、同様にこの表面に形成された第2の主電極であるドレイン電極15との間を、この2DEG層13を通って流れる。ゲート電極16とソース電極14との間の電子供給層12上に電位検出電極17が設置される。この電位検出電極17には、動作時にこの電位検出電極17に流れる電流がドレイン電流と比べて無視できる程度となるような、充分に高い抵抗値をもつ抵抗18が接続される。

(もっと読む)

スイッチ装置

【課題】トランジスタのチャネル部の異常を簡易且つ正確に検出できるスイッチ装置を提供する。

【解決手段】複数の半導体層で形成されて、ゲート電極にゲート電圧を印加されることによってドレイン電極−ソース電極間が導通し、ゲート電圧によって半導体層内で正孔と電子とが結合して発光する電界効果トランジスタ11,12と、ゲート電圧を制御する駆動部21と、トランジスタ11,12の発光量を検出する光検出部231,232とを備え、駆動部21は、光検出部231,232の検出結果に基づいて、トランジスタ11,12の異常を判定し、この判定結果に基づいてゲート電圧を制御する。

(もっと読む)

段間プローブ用パターン構造、段間測定方法、およびマルチチップモジュール高周波回路

【課題】複数段のトランジスタで構成されるモジュールの段間のSパラメータが測定可能な段間プローブ用パターン構造、段間測定方法、およびマルチチップモジュール高周波回路を提供する。

【解決手段】誘電体基板と、誘電体基板の第1表面上に配置された第1信号伝送線路と、誘電体基板の第1表面上に前記第1信号伝送線路に隣接して配置された一対の第1接地端子電極と、第1接地端子電極の下部に配置された第1VIAホールと、誘電体基板の第1表面と反対側の第2表面に配置され、第1接地端子電極に対して第1VIAホールを介して接続された裏面接地電極とを備える。第1信号伝送線路には高周波プローブの信号端子が接続可能であり、一対の第1接地端子電極には、高周波プローブの一対の接地端子が接続可能である。

(もっと読む)

半導体装置の製造方法

【課題】電気的特性の測定を精度高く行うことが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、基板10の裏面10bに、絶縁体からなり、厚さが1μm以下の保護膜22を形成する工程と、保護膜22を設ける工程の後に、基板10の表面10aに、MOCVD法を用いて、GaN系半導体層を成長させる工程と、GaN系半導体層を成長させる工程の後に、GaN系半導体層の電気的特性を測定する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置

【課題】破壊耐量が高い、2DEGを用いた半導体装置を提供する。

【解決手段】ソース・ドレイン間の耐圧よりも耐圧が低いSBDダイオード18のカソード電極がドレイン電極16に接続され、アノード電極がポリシリコンダイオード20を介してゲート電極14に接続されている。これにより、L負荷耐量試験回路によるL負荷耐量試験において、ゲート信号がターンオフされると、ドレイン電圧が印加され、SBDダイオード18にアバランシェ電流が流れ始め、電圧降下が発生し、ゲート電圧Vgが印加される。ゲートに閾値電圧Vthよりやや高い電圧(ゲートがオンする程度の電圧)が印加されると、ソース・ドレイン間が導通状態となる。これにより、ドレイン電圧がソース電極12とドレイン電極16との間の耐圧よりも低いSBDダイオード18の耐圧にクランプされた状態で、ドレイン電流が徐々に減少していく。

(もっと読む)

半導体装置の製造方法

【課題】エッチング速度に基づいて所望のエッチング量が得られるエッチング終了時期の判別方法の提供。

【解決手段】SiC半導体基板10(基板)上に窒素化合物層12−26を形成する。そして、窒素化合物層16−26をエッチングする。ここで、窒素化合物層12−26は、等間隔に配置され、窒素同位体N15を含む複数のマーカー層16,20,24を有する。また、窒素化合物層16−26をエッチングする際に、エッチング雰囲気中の窒素同位体N15の含有量のピークを検出することでエッチング速度を求める。

(もっと読む)

電界効果トランジスタ、及び電界効果トランジスタの製造方法

【課題】電界効果トランジスタの局所的な温度を測定することが可能な電界効果トランジスタを提供することである。

【解決手段】本発明にかかる電界効果トランジスタは、半導体層5と、半導体層5とオーミック接合したソース電極1と、半導体層5とオーミック接合したドレイン電極2と、半導体層5とショットキ接合したゲート電極3と、ソース電極1の一部に形成された空隙に設けられた、半導体層5とショットキ接合したショットキ電極4と、を有する。また、本発明にかかる他の態様の電界効果トランジスタは、半導体層5と、半導体層5とオーミック接合したソース電極1と、半導体層5とオーミック接合したドレイン電極2と、半導体層5とショットキ接合したゲート電極1と、ドレイン電極2の一部に形成された空隙に設けられた、半導体層5とショットキ接合したショットキ電極4と、を有する。

(もっと読む)

半導体基板、半導体基板の製造方法、半導体基板の判定方法、および電子デバイス

【課題】電圧対電流特性の線形性が改善された高性能の化合物半導体エピタキシャル基板、その製造方法およびその判定方法を提供する。

【解決手段】2次元キャリアガスを生成する化合物半導体114と、当該化合物半導体114にキャリアを供給するキャリア供給半導体120と、当該化合物半導体114と当該キャリア供給半導体120との間に配置され、キャリアの移動度を当該化合物半導体におけるキャリアの移動度よりも小さくする移動度低減因子を有する移動度低減半導体116とを備える半導体基板。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプスを抑制することができる電界効果トランジスタを提供する。

【解決手段】ソース電極105、ドレイン電極107およびゲート電極106を備えるHEMT100であって、第1の窒化物半導体からなる第1の半導体層103と、第1の半導体層103上に設けられた、第1の窒化物半導体よりもバンドギャップの大きな第2の窒化物半導体からなる第2の半導体層104とを備え、第1の半導体層103および第2の半導体層104のヘテロ接合によりチャネルが形成され、第1の半導体層103における、ドレイン電極107とゲート電極106との間の下方で、かつ、ヘテロ接合界面から所定の距離おいた領域には、低移動度領域108が設けられ、低移動度領域108は、第1の半導体層103における該低移動度領域108の周囲の領域よりも電子移動度の小さな領域である。

(もっと読む)

半導体装置の検査方法及び検査装置

【課題】層厚の厚い窒化物半導体層を有している窒化物半導体装置、及びHEMTが作り込まれている窒化物半導体装置を検査する場合においても、欠陥を確実に励起させ、かつ欠陥に由来するイエロールミネッセンスを精度良く検出する。

【解決手段】サファイア基板15の表面に形成されたGaN(窒化物半導体層)17に対して、表面と対向する裏面側から、第1励起光47を、サファイア基板を透過させて照射する。そして、第1励起光47によって窒化物半導体層17に発生し、かつサファイア基板15の裏面から出射される、欠陥に基づくイエロールミネッセンス49の第1強度を検出することによって、第1強度から窒化物半導体層17の評価を行う。

(もっと読む)

テラヘルツ光検出装置とその検出方法

【課題】極低温を必要することなく、小規模の装置で、非常に微弱なテラヘルツ光の強度を明確に検出でき、かつその周波数を正確に測定することができるテラヘルツ光検出装置とその検出方法を提供する。

【解決手段】表面から一定の位置に2次元電子ガス13が形成された半導体チップ12と、半導体チップの表面に密着して設けられたカーボンナノチューブ14、導電性のソース電極15、ドレイン電極16及びゲート電極17とを備える。カーボンナノチューブ14は、半導体チップの表面に沿って延び、かつその両端部がソース電極とドレイン電極に接続され、ゲート電極17は、カーボンナノチューブの側面から一定の間隔を隔てて位置する。さらに、ソース電極とドレイン電極の間に所定の電圧を印加しその間のSD電流を検出するSD電流検出回路18と、ソース電極とゲート電極の間に可変電圧を印加しその間のゲート電圧を検出するゲート電圧印加回路19と、半導体チップに可変磁場を印加する磁場発生装置20とを備える。

(もっと読む)

1 - 20 / 43

[ Back to top ]