Fターム[5F102GD05]の内容

接合型電界効果トランジスタ (42,929) | ゲート接合のタイプ (3,160) | pn接合型 (421) | ヘテロゲート (33)

Fターム[5F102GD05]に分類される特許

1 - 20 / 33

窒化物半導体電子デバイス、窒化物半導体電子デバイスを作製する方法

【課題】チャネルリークを低減可能な窒化物半導体電子デバイスが提供される。

【解決手段】

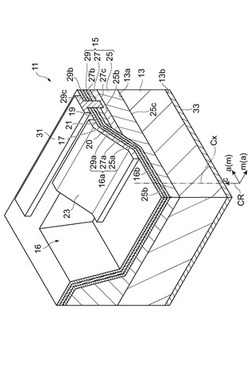

【0097】ヘテロ接合トランジスタ11によれば、電流ブロック層27はp導電性を有する。ドープ半導体層17が開口部16の側面16aに設けられると共にドープ半導体層17が電流ブロック層27とチャネル層19との間に設けられるので、チャネル層19が、エッチングの際に開口部16の側面16aに形成されている可能性があるドナー性欠陥を含む半導体に直接に接触することがない。また、ドープ半導体層17は、電流ブロック層27とチャネル層19との間に設けられると共にチャネル層19はキャリア供給層21とドープ半導体層17との間に設けられるので、ドープ半導体層17の追加により、チャネル層19及びキャリア供給層21の配列は変更されることがない。

(もっと読む)

スイッチ装置

【課題】GaNトランジスタを理想的な還流ダイオードとして動作させ、低損失のスイッチ装置を実現できるようにする。

【解決手段】スイッチ装置は、窒化物半導体素子301と、窒化物半導体素子301を駆動する駆動部302とを備えている。窒化物半導体素子301は、第1のオーミック電極、第2のオーミック電極及び第1のゲート電極を有している。駆動部302は、第1のゲート電極にバイアス電圧を印加するゲート回路311と、第1のゲート電極と第1のオーミック電極との間に接続され、双方向に電流を流すスイッチ素子312とを有している。駆動部302は、第1のオーミック電極から第2のオーミック電極への電流を通電し且つ第2のオーミック電極から第1のオーミック電極への電流を遮断する動作を行う場合には、スイッチ素子312をオン状態とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

半導体装置

【課題】オフ時のリーク電流を低減し、パワースイッチング素子に適用可能なノーマリーオフ型の半導体装置を提供する。

【解決手段】基板101と、基板101の上に形成されたアンドープGaN層103と、アンドープGaN層103の上に形成されたアンドープAlGaN層104と、アンドープGaN層103又はアンドープAlGaN層104の上に形成されたソース電極107及びドレイン電極108と、アンドープAlGaN層104の上に形成され、ソース電極107とドレイン電極108との間に配置されたp型GaN層105と、p型GaN層105の上に形成されたゲート電極106とを備え、アンドープGaN層103は、チャネルを含む活性領域113と、チャネルを含まない不活性領域112とを有し、p型GaN層105は、ソース電極107を囲むように配置されている。

(もっと読む)

双方向スイッチ、2線式交流スイッチ、スイッチング電源回路および双方向スイッチの駆動方法

【課題】部品点数増加を抑制する双方向スイッチを提供する。

【解決手段】双方向スイッチにおいて半導体装置101は、第1の電極109A、第2の電極109B、第1のゲート電極112Aおよび第2のゲート電極112Bとを備え、過渡期間において、前記第1の電極109Aの電位が前記第2の電極109Bの電位よりも高い場合、第1の閾値電圧よりも低い電圧を第1のゲート電極112Aに印加し、かつ、第2の閾値電圧よりも高い電圧を前記第2のゲート電極112Bに印加し、逆の場合、第1の閾値電圧よりも高い電圧を前記第1のゲート電極に印加し、かつ、第2の閾値電圧よりも低い電圧を前記第2のゲート電極に印加する。

(もっと読む)

窒化物半導体トランジスタ

【課題】電力損失を低減した窒化物半導体トランジスタを実現できるようにする。

【解決手段】窒化物半導体トランジスタは、分極が互いに異なる複数の窒化物半導体層が積層されたヘテロ接合層124と、ヘテロ接合層124の上に形成されたゲート電極113とを備えている。ヘテロ接合層とゲート電極との間には、p型の導電性を有し、正孔電流を流し且つ電子電流を抑制する電子電流抑制層125が形成されている。

(もっと読む)

双方向スイッチ素子及びそれを用いた双方向スイッチ回路

【課題】安定に動作する双方向スイッチ素子を実現できるようにする。

【解決手段】双方向スイッチ素子は、窒化物半導体からなる半導体層積層体203と、半導体層積層体203の上に形成された第1のオーミック電極211及び第2のオーミック電極212と、第1のゲート電極217及び第2のゲート電極218とを備えている。第1のゲート電極217は、第1のオーミック電極211と電位が実質的に等しい第1のシールド電極221に覆われている。第2のゲート電極218は、第2のオーミック電極212と電位が実質的に等しい第2のシールド電極222に覆われている。第1のシールド電極221の端部は、第1のゲート電極217よりも第2のゲート電極218側に位置し、第2のシールド電極222の端部は、第2のゲート電極218よりも第1のゲート電極217側に位置している。

(もっと読む)

半導体素子の駆動回路、および駆動回路を有する半導体装置

【課題】本発明は、ゲート−ソース間において所定電圧を超えると急峻な電流が流れるダイオード特性を示す半導体素子の高負荷時の消費電力低減および駆動回路の低負荷時の損失低減を図るだけでなく、過電圧、過電流、過消費電力を防止する保護機能と、当該半導体素子の損失を低減する機能を有する駆動回路の提供を目的とする。

【解決手段】駆動回路におけるゲート制御手段(2,12,22,32)は、ゲート−ソース間において所定電圧を超えると急峻な電流が流れるダイオード特性を示す半導体素子(1)の動作状態を検出する動作状態検出手段(4,5,6)から入力された半導体素子の動作状態を示す信号に応じて、半導体素子のゲートに供給する電圧または電流を制御するよう構成されている。

(もっと読む)

電界効果トランジスタ及びその評価方法

【課題】連続動作の際に生じるオン抵抗の増大を抑制した電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、窒化物半導体からなり、τc/τe>exp{−46.5+45.7exp(logx/21.6)+0.2exp(logx/0.27)}の関係を満たす。但し、xはR∞/R0−1であり、R∞はオフ状態において所定の時間保持した後、オン状態へとスイッチした直後のオン抵抗であり、R0はオフ状態の保持時間が所定の時間以内の場合にオフ状態からオン状態へとスイッチした直後のオン抵抗であり、τcはコラプスを引き起こす電子がトラップされる捕獲時定数であり、τeはコラプスを引き起こすトラップされた電子の放出の時定数である。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】薄膜トランジスタ用半導体層の材料として、高い正孔移動度を示すp形半導体多結晶薄膜を、かつ、低い成膜温度でのプラスチック基板上への成膜をも行うことのできるp形半導体多結晶薄膜を、提供する。

【解決手段】ガラスまたはプラスチックまたはステンレス基板のような非結晶質または多結晶基板1上に、該基板の温度を300℃以下とし、成長膜へのガリウム(Ga)、アンチモン(Sb)、及びヒ素(As)原子のそれぞれの供給量JGa,JSb,及びJAsを、JSb<JGa<JAs+JSbを満たすような値として、Ga,Sb,及びAs原子を同時供給して真空蒸着により成膜してなる、Sb組成yが0.5<y<1を満たすp形GaSbyAs1-y多結晶薄膜6を形成する製造方法による。

(もっと読む)

窒化物半導体装置

【課題】シリコン基板の上に形成され、優れた高周波特性を有する窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、シリコン基板101と、シリコン基板101の上に形成された窒化物半導体からなるバッファ層102と、バッファ層102の上に形成された窒化物半導体からなる能動層103とを備えている。バッファ層は、シリコン基板101と接して形成された第1の層121と、第1の層121及び能動層103と接して形成された第2の層122とを含む。第1の層121と第2の層122との界面における炭素濃度は、1×1019原子/cm3以上且つ1×1021原子/cm3以下であり、第2の層122は、炭素濃度が第1の層121と接する部分において最も高く、能動層103と接する部分において最も低い。

(もっと読む)

窒化物半導体装置

【課題】パワートランジスタに適用可能なノーマリオフ型の窒化物半導体装置に生じる電流コラプスを抑制できるようにする。

【解決手段】窒化物半導体装置は、サファイアからなる基板11と、該基板11の上に形成されたGaNからなるチャネル層13と、該チャネル層13の上に形成され、該チャネル層13よりもバンドギャップエネルギーが大きいAlGaNからなるバリア層14と、該バリア層14の上に形成され、p型AlGaN層15及びp型GaN層16を含むp型窒化物半導体層と、該p型窒化物半導体層の上に形成されたゲート電極19と、該ゲート電極19の両側方の領域にそれぞれ形成されたソース電極17及びドレイン電極18とを有している。p型窒化物半導体層は、ゲート電極19の下側部分の厚さが該ゲート電極19の側方部分の厚さよりも大きい。

(もっと読む)

電力変換モジュール及びそれを用いた電力変換装置あるいはモータ駆動装置あるいは空気調和機

【課題】インバータ等に適用される半導体デバイスは、寄生ダイオードにより誘導負荷からの還流電流を通流する場合、ダイオードの順方向電圧による損失が大きくなることが懸念され、また双方向デバイスを適用した場合には、2つのゲート端子を駆動する必要があり、制御の複雑化、かつ高コストになるという課題があった。

【解決手段】第一ゲート端子2、第二ゲート端子3、第一ソース端子4、第二ソース端子5を備え、第一ゲート端子2、第二ゲート端子3を各オンオフすることで4つの動作モードを有する双方向スイッチ1に適用する駆動方法であり、第一ゲート端子2あるいは第二ゲート端子3の何れか一方を常時オン状態となるように制御し、還流電流を流す経路を確保しつつ、ダイオード損失を低減し、かつ2つのゲート信号数を減らし、簡易な回路構成、かつ低コストに電源変換回路を実現することができる。

(もっと読む)

半導体装置

【課題】オフ特性が優れ、ゲート順方向電圧の範囲が広く、かつ、逆方向ブレークダウン電圧を高くすることができる構造の接合型FETを有する半導体装置を提供する。

【解決手段】第一のアンドープ層3上に、第一のアンドープ層3と接して、第一のアンドープ層3のバンドギャップより小さいバンドギャップを有するバンドギャップの小さい半導体層4が設けられ、その両端部と電気的に接続して一対の第一導電型コンタクト層6が設けられ、第一のアンドープ層3の下側に第二導電型コンタクト層2が設けられている。そして、一対の第一導電型コンタクト層6のそれぞれにオーミックコンタクトしてソース電極/ドレイン電極7が、また、第二導電型コンタクト層2にオーミックコンタクトしてゲート電極8がそれぞれ設けられることにより、接合型FETが構成されている。

(もっと読む)

電力変換装置

【課題】電流コラプスを十分に緩和し、GaNトランジスタが本来有している低いオン抵抗を利用した高効率の電力変換装置を実現できるようにする。

【解決手段】電力変換装置は、電源が接続される入力端Vin1と、電源から供給された電力をスイッチングする第1のスイッチング素子10とを備えている。第1のスイッチング素子10は、基板11の上に形成された窒化物半導体からなる半導体層積層体13と、半導体層積層体13の上に形成されたゲート電極18、第1のオーミック電極16及び第2のオーミック電極17と、基板11の裏面に形成された裏面電極20とを有している。裏面電極20には第2のオーミック電極17との間の電位差が小さくなるように入力端Vin1に接続された電源から電位が供給される。第1のスイッチング素子10がオン状態の場合には、裏面電極20に正電圧のバイアスが印加される。

(もっと読む)

ゲート駆動回路およびそれを用いたインバータ回路

【課題】双方向スイッチは、オン抵抗を下げるためにゲートの閾値電圧が低くする必要がある。閾値電圧を下げた場合、外来ノイズやスイッチング時のノイズ等によりゲート電位が振られ、誤動作が発生し、短絡故障などを起こす可能性があるため、そのような場合でも、冗長な動作が得られるよう基準電位を負電圧として電圧偏差を確保するような回路構成とし、誤動作などによる短絡故障を未然に防止することを目的とする。

【解決手段】第一ゲート端子2、第二ゲート端子3を各オンオフすることで4つの動作モードを有する双方向スイッチ1を直列接続したハーフブリッジ回路に適用するゲート駆動回路であり、第一ゲート端子2あるいは第二ゲート端子3のオン電圧とオフ電圧との偏差を確保する最適電圧生成部を備え、ゲート閾値電圧を下げてオン抵抗を下げ、ノイズが重畳した際であっても、不要なターンオンあるいはターンオフを回避することができる。

(もっと読む)

窒化物半導体装置

【課題】 ノーマリオフ特性を備えている窒化物半導体装置2を提供する。

【解決手段】 窒化物半導体装置2では、アンドープのGaNを材料とする窒化物半導体下層8の表面に、アンドープのAlGaNを材料とする窒化物半導体層10が積層されている。窒化物半導体層10は、窒化物半導体下層8よりも大きなバンドギャップを備えており、窒化物半導体下層8に対してヘテロ接合している。窒化物半導体層10の表面にはゲート絶縁膜16が形成されている。ゲート絶縁膜16は、窒化アルミニウム膜15で形成されている部分と、酸素又はシリコンを含む絶縁物質14で形成されている部分を含んでいる。窒化アルミニウム膜15が形成されている範囲W2はゲート電極18が形成されている範囲W1に含まれる関係にある。

(もっと読む)

トランジスタ

【課題】 ノーマリーオフ型であるとともに、ゲート閾値電圧のばらつきが小さいHEMT型のトランジスタを提供する。

【解決手段】 このトランジスタは、p型領域と、チャネル領域と、バリア領域と、絶縁膜と、ゲート電極を備えている。チャネル領域は、n型またはi型であり、p型領域の表面に接しており、第1チャネル領域と第2チャネル領域を有している。バリア領域は、第1チャネル領域の表面とヘテロ接合している。絶縁膜は、第2チャネル領域の表面、及び、バリア領域の表面に接している。ゲート電極は、絶縁膜を介して第2チャネル領域及びバリア領域に対向している。第1チャネル領域と第2チャネル領域は、電流経路において直列に配置されている。

(もっと読む)

高性能ヘテロ構造FETデバイス及び方法

【課題】

【解決手段】積層ヘテロ構造電界効果トランジスタ(HFET)は、基板と、基板上に成長する第1の酸化物半導体層と、第1の半導体層上に成長し、第1の半導体層とエネルギー・バンドギャップが異なる第2の酸化物半導体層と、を備え、また、前記第2の層は、ゲート領域と、ドレイン領域と、ソース領域と、を有し、ゲート領域、ドレイン領域、及びソース領域に対しては、HFETを形成するのに十分な電気的接触がもたらされる。基板は、単結晶材料を含む材料とすることができ、また、第1の半導体層がその上に成長するバッファ層材料を含有することができる。第1及び第2の半導体層の導電型ならびに各酸化物半導体層の組成は、HFETの所望の動作性能特性が改善されるように選択することができる。この積層構造は、半導体HFETデバイスの機能ならびに高周波及び高電力性能の改善に応用することができる。

(もっと読む)

III族窒化物半導体の選択成長方法

【課題】III 族窒化物半導体の選択成長方法において、選択成長層のキャリア濃度を精度よく制御すること。

【解決手段】まず、n−GaN基板10上にn- −GaN層11、p−GaN層12を積層し、p−GaN層12表面をNiを堆積した基板とともに塩素系プラズマに曝し、プラズマ損傷層13を形成する(図1a)。次に、エッチングマスク14を形成し、p−GaN層12の一部をドライエッチングし(図1b)、SC1、SC2洗浄を行った後エッチングマスク14を除去する(図1c)。次に、プラズマ損傷層13を選択成長マスクとしてn- −GaN層17を選択成長させる(図1d)。プラズマ損傷層13を選択成長マスクとして用いるため、n- −GaN層17の成長中にSiがドープされることがなく、n- −GaN層17のキャリア濃度の制御を正確に行うことができる。

(もっと読む)

1 - 20 / 33

[ Back to top ]