Fターム[5F102GL03]の内容

接合型電界効果トランジスタ (42,929) | チャネル層(主電流が流れる半導体層) (3,041) | 単一半導体層 (2,547) | 4族 (280) | Si (112)

Fターム[5F102GL03]に分類される特許

1 - 20 / 112

半導体装置及びその製造方法

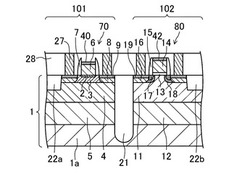

【課題】低周波雑音が低減されるとともに、素子面積の小さい半導体装置及びその製造方法を製造コストを増大させずに提供する。

【解決手段】半導体装置は、第1導電型の下部ゲート領域4と、第2導電型のチャネル領域3と、第1導電型の上部ゲート領域2と、チャネル領域3の両側に位置する第2導電型のソース及びドレイン領域8と、上部ゲート領域2上に形成されたゲート電極6と、ゲート電極6の両側面上に形成されたサイドウォールスペーサ7とを有するJFET70を備える。上部ゲート領域2とソース及びドレイン領域8とは、チャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間しており、ソース及びドレイン領域8は、ゲート長方向におけるゲート電極6の両側方であってサイドウォールスペーサ7の外側を含む領域に形成されている。

(もっと読む)

高速回復整流器構造体の装置および方法

【課題】高速回復整流器構造体の装置および方法を提供する。

【解決手段】具体的には構造体は第1のドーパントの基板(120)を含む。第1のドーパントが低濃度ドープされた第1のエピタキシャル層(140)が基板に結合されている。第1の金属層(190)が第1のエピタキシャル層に結合されている。複数のトレンチ(175)が第1のエピタキシャル層内に窪んでおり、その各々が金属層と結合している。装置は各々第2のドーパント型がドープされた複数のウェルも含み、各ウェルは対応するトレンチの下に且つ隣接して形成されている。複数の酸化物層(170)が対応するトレンチの壁および底部上に形成されている。第1のドーパントがドープされた複数のチャネル領域が、2つの対応するウェル間の第1のエピタキシャル層内に形成されている。複数のチャネル領域(150)の各々は第1のエピタキシャル層より高濃度に第1のドーパントがドープされている。

(もっと読む)

半導体装置及びその製造方法

【課題】電極端部への電界集中を抑えるとともに、ゲート電極の変形や、ゲート−フィールドプレート間に生じる容量による特性劣化を抑える。

【解決手段】半導体装置において、第1の基板と、第1の基板表面に形成された素子領域と、素子領域と接続され、第1の基板上に形成されたゲート電極、ソース電極及びドレイン電極と、第1の基板と、第1の面で積層される第2の基板と、第2の基板を貫通し、電極上に配置されるビアホールと、ビアホール内に形成され、電極と接続される金属層と、第2の基板に設けられ、ゲート電極、ソース電極及びドレイン電極のいずれかと接続されるフィールドプレート電極と、を備える。

(もっと読む)

半導体装置

【課題】高耐圧を確保でき、かつ大電流を流すことができるMOSトランジスタを備えた半導体装置を提供する。

【解決手段】P型拡散層15に起因してN型拡散層13に第1空乏層23が形成される。ゲート電極19にゲート電圧が印加されていない状態では、P型ポリシリコンからなるゲート電極19及びN型拡散層13の仕事関数差に起因してN型拡散層13に第2空乏層25が形成される。空乏層23,25によってソースコンタクト用拡散層9とドレインコンタクト用拡散層11が電気的に遮断される。ゲート電極19にゲート電圧が印加された状態では、第2空乏層25が消滅又は縮小することによってソースコンタクト用拡散層9とドレインコンタクト用拡散層11がN型拡散層13を介して電気的に導通する。

(もっと読む)

半導体装置及びその駆動方法

【課題】順方向電圧降下の平均値を低減し、整流素子の低損失化を実現する半導体装置とその駆動方法を提供する。

【解決手段】アノード電極9とカソード電極3との間に、p型層7と、i層1と、n型層2とを順に形成したダイオード構造の半導体装置において、アノード電極9側に、p型層7と並列に第2n型層8を形成し、順方向バイアス中に、アノード電極9側をp型層7と第2n型層8のいずれかに切り替えるゲート駆動回路10を備えた半導体装置。ゲート電極5は、p型層7と第2p型層6と第2n型層8に接するトレンチ構造4とし、トレンチ内部に絶縁膜4aと電極とを備えたものとすることができる。このゲート電極5は、ゲート駆動回路10から印加するゲート電圧に応じてp型及びn型のチャネルをトレンチ表面に形成する。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 JFET等のような低ノイズ特性が要求される半導体装置において、発生するノイズを低減すると共に、半導体装置を小さい寸法で製造する。

【解決手段】 半導体装置は、半導体層(101)に形成された素子分離(102)、第1導電型の不純物層(104)、第1導電型のソース領域(106)、第1導電型のドレイン領域(107)、第2導電型のゲート領域(105)、絶縁膜(108)を介して形成された制御電極(109)を備える。制御電極(109)に電圧を印加すると、半導体装置の動作中に制御電極(109)の下の不純物層(104)に空乏層を発生させることができ、キャリアは絶縁膜(108)と不純物層(104)の界面から離れて流れる。

(もっと読む)

薄膜半導体デバイスおよび薄膜半導体デバイスの製法

【課題】安価に、デバイスの効率および長期間安定性が改善された薄膜半導体デバイスを提供する。

【解決手段】薄膜半導体デバイスは、セルロースを含む材料、より具体的には、紙シート材料の基材および基材上の層に蒸着された無機材料の多数の薄膜層を含み、無機材料の多数の薄膜層のうち少なくとも一つは、該基材または基礎をなす無機材料の薄膜層の一方に印刷され、無機材料の多数の薄膜層のうちの少なくとも一つはナノ結晶シリコン粉末を含む活性半導体層およびポリマーを含む担体を含む。

(もっと読む)

超高速リカバリダイオード

【課題】ソフトリカバリ特性を維持する逆回復電荷を低減した高速リカバリダイオードを提供する。

【解決手段】整流装置100は、第1の極性の基板と、基板に結合された第1の極性の低濃度ドープ層180と、低濃度ドープ層と共に配置された金属層140とを備える。超高速リカバリダイオードは、互いに離間され、低濃度ドープ層内に形成され、第2の極性のドーピングを備える複数のウェル150を含む。複数のウェルは金属層130に接続する。超高速リカバリダイオードは、複数のウェルのウェル間に位置し、低濃度ドープ層より高濃度に第1の極性がドープされた複数の領域160をさらに含む。

(もっと読む)

増幅回路装置

【課題】意図しない低周波信号の入力を防止することにより、規格値を超過するドレイン電流を発生することを回避できる接合形電界効果トランジスタを用いた増幅回路装置を提供する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FET1のゲート−ソース間に接続される抵抗2とによってハイパスフィルタ5を構成する。ハイパスフィルタ5の遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。チップを構成する基板の裏面にイオン注入によりn型不純物層を設け、p+型半導体基板とpn接合を形成して接合容量をハイパスフィルタ5の容量4とする。

(もっと読む)

増幅回路装置

【課題】J−FETを増幅回路装置として採用する場合に、意図しない低周波信号の入力を防止し、規格値を超過するドレイン電流が発することを回避する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FETのゲート−ソース間に接続される抵抗とによってハイパスフィルタ5を構成する。ハイパスフィルタ5の遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。n型半導体基板上にバックゲート領域となるp型半導体層を設けてpn接合を形成し、この接合容量をハイパスフィルタ5の容量とする。

(もっと読む)

増幅回路装置

【課題】意図しない低周波信号の入力を防止し規格値を超過するドレイン電流が発生することを回避できる増幅回路装置を提供する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量4を付加し、当該容量4とJ−FET1のゲート−ソース間に接続される抵抗2とによってハイパスフィルタを構成する。ハイパスフィルタの遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。チップを構成する基板の裏面に絶縁層を設けてこれを誘電体とし、導電部材と基板とで平行平板型の容量4を接続する。

(もっと読む)

半導体素子および半導体デバイス

【課題】オン抵抗が比較的低く大電流にも対応可能という特性を持ちながら、光照射強度に応じて電流を変化させることができる半導体素子および半導体デバイスを提供する。

【解決手段】電子走行層14における電子供給層15との界面には動作時にチャネルとなる2次元電子ガス領域16が形成される。2次元電子ガス領域16におけるドレイン電極11とソース電極12との間の一部には、空乏化部18により空乏化された空乏領域17が形成されている。半導体素子1は、空乏領域17に光を照射しない状態で、2次元電子ガス領域16の空乏領域17が空乏化しているため、ドレイン電極11・ソース電極12間が非導通となる。一方、半導体素子1は、電子走行層14のバンドギャップよりも大きなエネルギを持つ光を空乏領域17に受けた状態で、空乏領域17に電子20と正孔とが生成されることでドレイン電極11・ソース電極12間が導通する。

(もっと読む)

接合型電界効果トランジスタ

【課題】 従来のJ−FETでは、動作領域内のゲート領域(トップゲート領域)は、動作領域外周に設けられた深いゲート領域を介してのみ、半導体基板(バックゲート領域)と接続していた。このため動作領域の中央と外周ではゲート抵抗にばらつきが生じ、ゲート抵抗の増加によるノイズ電圧の増加や、不均一動作によるゲインの低下が問題であった。

【解決手段】 格子状のゲート領域(トップゲート領域)を有するJ−FETにおいて、行列状にソース領域と交互に配置されていたドレイン領域の一部を深いゲート領域に置き換え、動作領域内にも深いゲート領域を設ける。ドレイン領域を一部省くことで生じるドレイン電流の流れない無効領域をできる限り減らすため、ソース領域が配置されるセルについてドレイン電流が流れない方向のゲート領域を短くする。

(もっと読む)

接合型電界効果トランジスタ、その製造方法及びアナログ回路

【課題】外部ノイズの影響を低減できるJFETを提供する。

【解決手段】本発明に係るJFET50は、p型半導体基板1と、p型半導体基板1の表面に形成されているn型チャネル領域3と、n型チャネル領域3内に形成されており、n型チャネル領域3よりも不純物濃度の高いn型埋め込み領域4と、n型チャネル領域3の表面に形成されているp型ゲート領域6と、n型チャネル領域3の表面に、p型ゲート領域6を挟むように形成されているn型ドレイン/ソース領域7及びn型ドレイン/ソース領域8とを備え、n型埋め込み領域4は、n型ドレイン/ソース領域7及びn型ドレイン/ソース領域8の一方の下方に形成されており、他方の下方に形成されていない。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法、および半導体装置の動作方法

【課題】電界集中を緩和し、高い耐圧を得ることが可能な半導体装置を提供する。

【解決手段】

半導体層上において、第1フィールドプレートFAは、第1絶縁膜上に、第1電極102と第2電極103との間に相互に間隔を置いて配置され、第2フィールドプレートFBは、第2絶縁膜上に、第1電極102上方から第2電極103上方までの間に相互に間隔を置いて配置され、

第1電極および第2電極側末端のFBは、第1電極または第2電極およびそれに隣り合うFAに重なり、

前記第1電極および第2電極側末端FB以外の一方のFAまたはFBは、第1電極から第2電極への方向と垂直方向に隣り合う複数の他方のFAまたはFBに重なり合い、前記第1電極および第2電極側末端FB以外の他方のFAまたはFBは、第1電極から第2電極への方向に隣り合う2つの前記一方のFAまたはFBに重なり合う半導体装置。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】エピタキシャル成長を行わなくても素子形成が行え、かつ、バンチングが発生することを防止できるようにする。

【解決手段】エピタキシャル成長を行わず、素子を構成する各領域をイオン注入のみによって形成すると共に、SiC基板1としてオフ角を有しないオン基板を用いる。これにより、イオン注入領域を活性化するための熱処理によってバンチングが発生しないようにできる。したがって、エピタキシャル成長を行わなくても素子形成が行え、かつ、バンチングが発生することを防止できるSiC半導体装置とすることができる。

(もっと読む)

半導体装置

【課題】低電圧時の電流が適度に大きく、高電圧時の電流が小さい半導体装置を提供する。

【解決手段】半導体装置100は、整流素子D1と、抵抗R1と、nチャネルディプリーショントランジスタDTと、アノード電極パッド7bとが直列接続された構成を有する半導体装置100であって、nチャネルディプリーショントランジスタDTのゲート電位を抵抗R1の両端の電位差により生成し、かつゲート電位によってnチャネルディプリーショントランジスタDTのチャネル91に空乏層Dを生じさせるよう構成されている。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】高耐圧および高電流のスイッチング動作が可能で、かつ製造が容易なFETを提供する。

【解決手段】半導体薄体の一の主表面に設けられた、第1導電型のソース領域(1)と、第1導電型のチャネル領域(10)と、チャネル領域を限定する第2導電型の限定領域(5)と、他の主表面に設けられた第1導電型のドレイン領域(3)と、厚さ方向に連続する第1導電型のドリフト領域(4)とを備え、ドリフト領域(4)およびチャネル領域(10)の不純物濃度は、ソース領域(1)、ドレイン領域(3)および限定領域(5)の不純物濃度よりも低く、チャネル領域(10)の不純物濃度はドリフト領域(4)の不純物濃度よりも低い。

(もっと読む)

接合型電界効果トランジスタおよびその製造方法

本願は、ドレイン(140)と、ゲート(160)と、ソース(130)と、を有し、ドレイン(140)およびソース(130)が、第1の型の半導体領域によって形成される、電界効果トランジスタに関する。一局面では、電界効果トランジスタはまた、ゲート(160)とドレイン(140)の中間のさらなるN+領域(410)等のさらにドープされた領域を含む。さらにドープされた領域は、電界効果トランジスタの中間ドレインとして見なすことができる。いくつかの実装では、さらにドープされた領域は、高濃度にドープすることができる。さらにドープされた領域によって、ドレイン(140)周囲の電界勾配を減少させることができる。  (もっと読む)

(もっと読む)

1 - 20 / 112

[ Back to top ]