Fターム[5F102HC30]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | メッキ (48)

Fターム[5F102HC30]に分類される特許

1 - 20 / 48

半導体装置の製造方法

【課題】エピ抵抗や抵抗チップを用いることなく、奇モードのループ発振を抑えること。

【解決手段】本発明は、金属層60を形成する工程と、複数のFETそれぞれのゲートフィンガー14を共通に接続するゲートバスライン26のパターンのうち一部分を除いたパターンを有するめっき層64と、一部分の領域を被覆する第2マスク層66と、をマスクにして金属層60をパターニングすることで、ゲートバスライン26を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

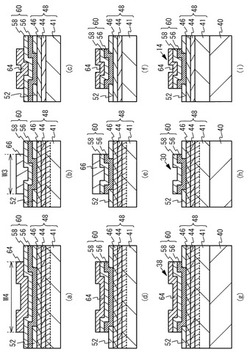

半導体装置及びその製造方法

【課題】高周波特性の悪化を防ぎ、耐湿性を向上させる。

【解決手段】半導体基板1の主表面上の素子領域内に、ドレイン電極2が設けられている。一端がドレイン電極2に接続されたドレイン配線5が主表面上に設けられている。主表面上の素子領域外に、ドレイン配線5とは離間したドレイン電極パッド12が設けられている。Auメッキ層9が主表面上に設けられ、主表面との間に空隙10が形成されている。空隙10はドレイン配線5の一端とドレイン電極2を内包する。硬化されたポリイミド膜14が空隙10の開口部11を閉塞し、ドレイン電極パッド12を覆うことなく、ドレイン配線5の他端を覆っている。空隙10の内面に撥液膜15が設けられている。硬化されたポリイミド膜14に設けられた開口16を介してAuメッキ層18により、ドレイン配線5の他端とドレイン電極パッド12が接続されている。ドレイン配線5の他端はポリイミド膜14から出ていない。

(もっと読む)

電力増幅装置及び連結電力増幅装置

【課題】ソース電極からビアホールまでの距離をさらに短くし、インダクタンスの影響をできる限り低下させる増幅装置を提供する。

【解決手段】電力増幅装置は、接地のためのビアホールと接続する接地部と、接地部を接続するソース電極接地導体と、ソース電極接地導体に連結したソース電極と、ソース電極接地導体に接触しない内側ソース電極と、ドレイン電極と、ゲート電極と、内側ソース電極と接地部とを直接接続する接地ブリッジと、を備える。

(もっと読む)

半導体装置及び製造方法

【課題】 ビアホール上にオーミック電極が形成された半導体装置において、装置の小型化を図ること。

【解決手段】 本半導体装置は、基板10と、基板10上に形成された半導体層12と、半導体層上12に形成されたソースまたはドレイン電極を構成するオーミック電極20と、を備え、基板10及び半導体層12には、基板10及び半導体層12を貫通するビアホール30が形成され、ビアホール30は、少なくとも半導体層を貫通する第1ビアホール32と、第1ビアホール32下の基板10に形成された、第1ビアホール32より開口断面積が大きい第2ビアホール34と、を含み、オーミック電極20は、第1ビアホール32の上に設けられている。

(もっと読む)

化合物半導体基板の製造方法

【課題】結晶欠陥の少ない化合物半導体層を種基板上にエピタキシャル成長できる化合物半導体基板の製造方法を提供する。

【解決手段】電解めっきにおいて種基板10を膜厚方向に貫通する貫通転位101〜105をそれぞれ通して種基板10の厚さ方向に電流を流すことにより、種基板10の第1の主面11上の貫通転位101〜105が存在する位置に金属膜201〜205を選択的に形成するステップと、金属膜201〜205の融点より低いエピタキシャル成長温度で、金属膜201〜205を覆うように種基板10の第1の主面11上に化合物半導体層30をエピタキシャル成長させるステップとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系HEMT及びMIMキャパシタを同一基板上に設ける場合でも小型化することができる半導体装置及びその製造方法を提供する。

【解決手段】基板1の表面上に下部電極11を形成し、下部電極11上に誘電体膜12を形成し、誘電体膜12上に基板1の表面に接する上部電極14aを形成する。また、基板1の裏面から基板1をエッチングすることにより、上部電極14aの基板1の表面に接する部分に達するビアホール1aを基板1に形成し、基板1の裏面上にビアホール1aを介して上部電極14aに接するビア配線36を形成する。

(もっと読む)

ヘテロ接合型電界効果トランジスタ

【課題】HFETの種々の特性を改善する。

【解決手段】ヘテロ接合型電界効果トランジスタでは、サファイア基板の上面上において第1の金属層(2)とヘテロ接合を含む窒化物半導体層(5、6)とがこの順に形成されており、窒化物半導体層上にはソース電極(7)、ゲート電極(8)およびドレイン電極(9)が配置されており、第1の金属層は開口部(4)を含むようにパターン化されており、窒化物半導体層は第1の金属層の開口部で露出されたサファイア基板の上面から結晶成長しており、第1の金属層はソース電極へ電気的に接続されていることを特徴としている。

(もっと読む)

半導体装置およびその製造方法

【課題】簡便に半導体集積回路を小領域に電気的に分離する。

【解決手段】厚さが150〜600μm程度のInP基板、GaAs基板等の化合物半導体基板1の表面に半導体集積回路2を形成し、化合物半導体基板1の裏面(半導体集積回路2が形成された表面とは反対側の面)に、直角に交わっている複数の切込溝3を設け、半導体集積回路2の表面から切込溝3の底面までの距離を50〜150μmとし、切込溝3内にAu等の金属4を埋め込み、金属4を化合物半導体基板1の裏面全面にも設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、製造歩留まりの向上を図ることができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】

半導体装置は、基板1の上方に設けられた化合物半導体層2,3,4と、化合物半導体層2,3,4の上方に設けられた複数のソース電極7及び複数のドレイン電極9と、化合物半導体層2,3,4を貫通し、複数のソース電極7のそれぞれに接続される複数のビア配線22と、化合物半導体層2,3,4を貫通し、複数のドレイン電極9のそれぞれに接続される複数のビア配線23と、複数のビア配線22に接続され、基板1に埋め込まれたソース共通配線18と、複数のビア配線23に接続され、基板1に埋め込まれたドレイン共通配線20とを有する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置のビアホールにおける残渣物の残留を抑制することができ、かつ、半導体装置のデバイス特性不良、信頼性不良等を抑制することができる、半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、GaN系半導体層(11)が設けられたSiC基板(10)の第1主面の反対側の第2主面上にCuあるいはCu合金からなり部分的に開口を有するエッチングマスク(50)を形成する工程と、エッチングマスク(50)を利用したドライエッチングを実施し、底部の厚さ方向にGaN系半導体層(11)が残存したビアホールを形成する第1エッチング工程と、第1エッチング工程の後にエッチングマスク(50)を除去する除去工程と、除去工程の後に残存したGaN系半導体層(11)に対してドライエッチングを実施する第2エッチング工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、高周波高出力で使用可能な、化合物半導体高電子移動度トランジスタを提供する。

【解決手段】支持基板20の第1の主表面20a上に、チャネル層40及びバリア層50が積層されて構成される、化合物半導体高電子移動度トランジスタであって、ソース電極62が形成された領域を含む、支持基板の領域部分が金属部22であり、ドレイン電極64が形成された領域を含む、支持基板の他の領域部分がシリコン部24で構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、Au配線との密着性が強く、より高い熱的安定性を有するバリアメタル層を実現し、更なる特性向上、歩留まり向上を実現する。

【解決手段】半導体装置を、Al層8を含む電極9,10と、Au配線12と、Al層8とAu配線12との間に設けられ、Al層8の側から順に第1Ta層14、第1TaN層15、第1Pt層16を積層した構造を有するバリアメタル層11とを備えるものとする。

(もっと読む)

化合物半導体装置の製造方法

【課題】基板の付け替えに際して基板を適切に分離することができる化合物半導体装置の製造方法を提供する。

【解決手段】基板の上方に、第1のバンドギャップのAlxGa1-xN(0≦x<1)を含む第1の化合物半導体層を形成する。前記第1の化合物半導体層上に、前記第1のバンドギャップよりも広い第2のバンドギャップのAlyInzGa1-y-zN(0<y<1、0<y+z≦1)を含む第2の化合物半導体層を形成する。前記第2の化合物半導体層の上方に、化合物半導体積層構造を形成する。前記第1のバンドギャップと前記第2のバンドギャップとの間のエネルギを有する光を前記第1の化合物半導体層に照射しながら前記第1の化合物半導体層を除去して、前記基板を前記化合物半導体積層構造から分離する。

(もっと読む)

半導体装置の製造方法

【課題】窒化物半導体層を有する半導体装置を低コストで製造する。

【解決手段】基板上に第1の窒化物半導体の犠牲層を形成する犠牲層形成工程と、前記犠牲層上に第2の窒化物半導体層を形成し、前記第2の窒化物半導体層上に窒化物半導体層を積層した積層窒化物半導体層を形成する積層半導体形成工程と、前記犠牲層の表面が露出するまで、前記第2の窒化物半導体層及び前記積層窒化物半導体層をエッチングすることによりトレンチを形成し、前記トレンチ及び前記積層窒化物半導体層表面に接続電極を形成する接続電極形成工程と、前記接続電極の形成された前記基板を電解液に浸漬させ、前記電解液に対し前記接続電極に電位を印加し、前記犠牲層を除去し前記基板を剥離する犠牲層除去工程とを有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体層の一方の面に基板が形成された半導体素子について、特性の劣化を避けながら容易に形成することを実現する。

【解決手段】半導体素子1は、半導体材料からなる半導体層5と、半導体層5の一方の面に接合された金属層18とを備え、金属層18は、磁性体層16を有し、磁性体層16は、少なくともFe及びNiを含む合金からなる層を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧に優れ、強度の高いIII−V族窒化物半導体からなる半導体装置を実現する。

【解決手段】本発明の構造では、第1のソース電極106がバイアホール112を介して導電性基板101に接続されており、また、第2のソース電極110が形成されている。これにより、ゲート電極108とドレイン電極107との間に高い逆方向電圧が印加されても、ゲート電極108のうちドレイン電極107に近い側の端部に起こりやすい電界集中を効果的に分散または緩和することができるため、耐圧が向上する。また、素子形成層を形成する基板として導電性基板101を用いているため、導電性基板101には裏面まで貫通するバイアホールを設ける必要がない。したがって、導電性基板101に必要な強度を保持したまま、第1のソース電極106と裏面電極115とを電気的に接続することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】エレクトロマイグレイション耐性の高いエアブリッジ配線を具備した半導体装置及びその製造方法を提供すること。

【解決手段】第1の配線と、第1の配線から空間によって隔てられた状態で、前記第1の配線の上を横切る第2の配線と、前記第1及び第2の配線に接続された半導体素子を具備し、前記第2の配線は、下から順に、タンタル層、タンタルナイトライド層、及び金層が積層されて形成されていること。

(もっと読む)

電界効果トランジスタ

【課題】電流容量および耐電圧を大きくしたノーマリオフの縦型構成の電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ1は、半導体基板10と、半導体基板10に積層された窒化物系III−V族化合物半導体層20と、窒化物系III−V族化合物半導体層20から積層方向に交差する横方向へ成長した横方向成長領域22と、半導体基板10の裏面に形成されオーミック性を有する第1電極31(ドレイン電極)と、窒化物系III−V族化合物半導体層20の表面に形成されオーミック性を有する第2電極32(ソース電極)と、窒化物系III−V族化合物半導体層20の積層方向で第1電極31と第2電極32との間での電流路となる通電領域21と、横方向成長領域22に接触させて形成され通電領域21での通電状態を制御する第3電極33(ゲート電極)とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】VIAホール側壁の金属層が半導体層に拡散することを防止する。

【解決手段】半絶縁性基板11の第1表面に配置されたゲートフィンガー電極2、ソースフィンガー電極3およびドレインフィンガー電極4と、第1表面と反対側の第2表面に配置された接地導体26と、ゲートフィンガー電極2、ソースフィンガー電極3およびドレインフィンガー電極4ごとに複数のフィンガーをそれぞれ束ねて形成したゲート端子電極14、ソース端子電極18およびドレイン端子電極12と、ゲートフィンガー電極2、ソースフィンガー電極3およびドレインフィンガー電極4の下部の半絶縁性基板11上に形成された動作層と、動作層近傍のVIAホール30の内壁面上に配置された絶縁膜44と、絶縁膜44および半絶縁性基板11の第2表面に形成され、ソース端子電極18に対して第2表面側から接続された接地電極46とを備える半導体装置およびその製造方法。

(もっと読む)

半導体装置

【課題】ワイヤボンドを行っても、断線、抵抗増加および信頼性低下を防ぐことができると共に、歩留まりを向上できる半導体装置を提供する。

【解決手段】基板101の上面には半導体層102が形成されている。基板101および半導体層102を貫通するバイアホール110が形成され、半導体層102上にはソース電極104およびドレイン電極105が形成されている。ソース電極104はソース配線107に電気的に接続されている。バイアホール110およびソース配線107上に絶縁膜103が形成されている。絶縁膜103上には、ドレイン電極105に電気的に接続されたドレイン配線108が形成されている。ドレイン配線108は、バイアホール110と重なる領域以外の領域に形成されている。つまり、バイアホール110の上方においてドレイン配線108が形成されていない。

(もっと読む)

1 - 20 / 48

[ Back to top ]