Fターム[5F110BB06]の内容

Fターム[5F110BB06]に分類される特許

141 - 160 / 395

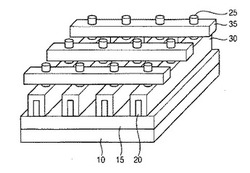

埋立ビットラインを有する半導体装置及び半導体装置の製造方法

【課題】埋立ビットラインを有する半導体装置及び半導体装置の製造方法を提供すること。

【解決手段】埋立ビットラインを備えて低抵抗を有する垂直ピラートランジスタを含む半導体装置及びその製造方法が開示される。垂直ピラートランジスタは、基板上に形成され、下部と上部を有する本体、本体の上部に配置されるソース/ドレインノード、そして、本体の下部に配置されるドレイン/ソースノードを含む。半導体装置は、少なくとも本体の下部の上部表面に形成され、金属シリサイドを含む前記埋立ビットライン及び前記本体の上部を部分的に包むワードラインを備える。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体を用いて構成された半導体装置であって、ビット線の電位と等しい電位またはビット線の電位と異なる電位をソース線に選択的に与える機能を有する電位切り替え回路を備えた半導体装置とする。これにより、半導体装置の消費電力を十分に押さえることができる。

(もっと読む)

SeOIの連想メモリでデータを比較するデバイス

【課題】連想メモリの比較デバイス、比較デバイスを制御する方法、および連想メモリを提供する。

【解決手段】データビットを格納する第1のトランジスタT1およびデータビットの補数を格納する第2のトランジスタT2によって形成されたメモリセルであって、各トランジスタは、セミコンダクタ・オン・インシュレータ基板上に作られ、各々は、フロント制御ゲート、およびトランジスタを遮断するように制御するバック制御ゲートBG1、BG2を有する、メモリセルと、各々のフロント制御ゲートに公称読出し電圧を加えることによって読出しモードで動作させ、一方、バック制御ゲートBG1、BG2を、一方をビット(DATA)、他方をビットの補数(DATAb)で制御し、ビット(DATA)と格納されたビットが一致する場合には各々のうちの通過トランジスタを遮断し、各々のソースに連結されたソース線SLの電流の有無を検出する比較回路を備える。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】専有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】書き込み用トランジスタと読み出し用トランジスタで、共通のビット線を使用することで、単位メモリセル当たりの配線数を削減する。情報の書き込みは、書き込み用トランジスタをオン状態とすることにより、書き込み用トランジスタのソース電極またはドレイン電極の一方と、読み出し用トランジスタのゲート電極が電気的に接続されたノードに、ビット線の電位を供給し、その後、書き込み用トランジスタをオフ状態とすることにより、ノードに所定量の電荷を保持させる。情報の読み出しは、容量素子に接続された信号線を読み出し信号線とするか、もしくは、読み出し用のトランジスタのソース電極またはドレイン電極の一方と接続された信号線を読み出し信号線として、読み出し信号線に読み出し用の電位を供給し、その後、ビット線の電位を検知することで行う。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

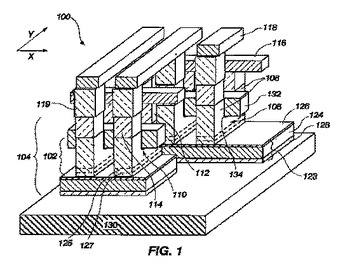

浮遊ボディセル、浮遊ボディセルを含むデバイス、ならびに浮遊ボディセルの形成方法。

バックゲート上に配置される浮遊ボディセルのアレイと、バックゲートから間隔の開いた浮遊ボディセルのソース領域およびドレイン領域と、を含む浮遊ボディセル構造。浮遊ボディセルは、ピラーの間に伸長するチャネル領域を有する大量の半導電性材料を各々含み、ピラーは、U形状トレンチなどの間隙によって分離されうる。アレイの浮遊ボディセルは、別のゲートに電気的に結合され、別のゲートは、大量の半導電性材料の側壁上に配置されてもよいし、大量の半導電性材料の間隙内に配置されてもよい。浮遊ボディセルデバイスを形成する方法も開示される。  (もっと読む)

(もっと読む)

チャネルが埋込み誘電体層を通り抜けているメモリセル

【課題】浮動チャネルまたは浮動ゲートを持つFET(Field Effect Transistor(電界効果トランジスタ))により形成されたメモリセル、複数のメモリセルから成るメモリアレイの提供。

【解決手段】絶縁層BOXによってベース基板から隔てられた半導体材料の薄層を含むセミコンダクタ・オン・インシュレータ基板と、少なくとも基本的にセミコンダクタ・オン・インシュレータ基板の薄層中に配列されたソース領域S、ドレイン領域D、トレンチがその中に作られているチャネルC、トレンチ中のゲート領域Gを含むFETトランジスタを備え、トレンチが、絶縁層BOXを越えベース基板の深さの中に延びていること、チャネルが、絶縁層の下でソース領域とドレイン領域の間に延びていることを特徴とするメモリセル。複数のメモリセルを備えるメモリアレイ、およびメモリセルを製作するプロセス。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のトランジスタ160と、第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成され、第1のトランジスタ160のゲート電極と、第2のトランジスタ162のソース・ドレイン電極とは、電気的に接続され、第1の配線と、第1のトランジスタ160のソース電極とは、電気的に接続され、第2の配線と、第1のトランジスタ160のドレイン電極とは、電気的に接続され、第3の配線と、第2のトランジスタ162のソース・ドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のトランジスタ162のゲート電極とは、電気的に接続される。

(もっと読む)

半導体装置

【課題】機能回路の電源配線及び接地配線に要する接地面積を少なくし、同時に消費電流による電源電圧降下及び接地電圧上昇を抑えることで、薄型・軽量・高機能・低価格の半導体装置を提供する。

【解決手段】機能回路に電源電圧を供給する電源配線1009及び接地電圧を供給する接地配線1010が格子状に配置されている半導体装置である。格子状にすることで、電源電圧降下及び接地電圧上昇は大幅に低減できる。また、配線幅を細くしても、格子状にしない場合と同程度の電源電圧降下及び接地電圧上昇に抑えられるので、電源配線及び接地配線の配置面積を大幅に低減できる。

(もっと読む)

埋め込み絶縁層を貫いて半導体層間に接触を有するデバイス、およびこのデバイスの製造プロセス

【課題】簡潔な方法で、SeOI基板上の半導体デバイスの半導体領域に接続するラインを提供すること。

【解決手段】第1の側面によると、本発明は埋め込み絶縁層(3、BOX)によってベース基板(2)から隔離された半導体材料の薄い層(1)を含むSeOI(Semiconductor−On−Insulator)基板上に作製された半導体デバイスに関し、デバイスは、薄い層内に第1の伝導領域(1、D1、S、E)と、ベース基板内に第2の伝導領域(5、BL、SL、IL)とを含み、接触(I1、I2、IN、IP)は絶縁層を貫通して第1の領域と第2の領域を接続する。第2の側面によると、本発明は第1の側面に関する半導体デバイスの製作プロセスに関する。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体以外の半導体材料が用いられた第1のチャネル形成領域を有する第1のトランジスタ160と、第1のトランジスタ160の上方の、酸化物半導体材料が用いられた第2のチャネル形成領域を有する第2のトランジスタ162と、容量素子164と、を有し、第2のトランジスタ162の第2のソース電極または第2のドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続される。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のソース電極および第1のドレイン電極と、第1のソース電極および第1のドレイン電極と電気的に接続され、酸化物半導体材料が用いられている第1のチャネル形成領域と、第1のチャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、を有する第1のトランジスタと、容量素子と、を有し、第1のトランジスタの第1のソース電極または第1のドレイン電極の一方と、容量素子の電極の一方とは、電気的に接続された半導体装置である。

(もっと読む)

表示装置、及び当該表示装置を具備する電子機器

【課題】消費電力が抑制された表示装置を提供する。

【解決手段】第1のトランジスタ、第2のトランジスタ、及び一対の電極を有する発光素子を含む画素が複数設けられた画素部を有し、前記第1のトランジスタは、ゲートが走査線に電気的に接続され、ソースまたはドレインの一方が信号線に電気的に接続され、ソースまたはドレインの他方が前記第2のトランジスタのゲートに電気的に接続され、前記第2のトランジスタは、ソースまたはドレインの一方が電源線に電気的に接続され、ソースまたはドレインの他方が前記一対の電極の一方に電気的に接続され、前記第1のトランジスタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有する。そして、前記表示装置が静止画像を表示する期間の間に、前記画素部に含まれる全ての走査線に供給される信号の出力が停止される期間を有する。

(もっと読む)

半導体装置

【課題】様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供する。

【解決手段】強磁性材料からなるシートを支持体とし、前記強磁性材料からなるシートに接する接着材と、該接着材に接する絶縁膜上に素子とを備える。上記構成において、前記素子は、薄膜トランジスタ、有機化合物を含む層を有する発光素子、液晶を有する素子、メモリー素子、薄膜ダイオード、シリコンのPIN接合からなる光電変換素子、またはシリコン抵抗素子であってもよい。また、上記各構成において、前記強磁性材料からなるシートは、軟質磁性粉体と合成樹脂とを混合して形成され、着磁されたものであってもよい。

(もっと読む)

半導体素子、半導体装置及びそれらの作製方法

【課題】チャネル長Lが短く微細化が可能な、酸化物半導体を用いたトップゲート型の半導体素子を提供することを課題とする。また、該半導体素子の作製方法を提供することを課題とする。

【解決手段】絶縁表面上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、酸化物半導体層、前記ソース電極層、及び前記ドレイン電極層上にゲート絶縁層と、ゲート絶縁層上にゲート電極層とを有し、ソース電極層及びドレイン電極層は側壁を有し、側壁は前記酸化物半導体層の上面と接する半導体素子である。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトランジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトランジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタ160と、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

141 - 160 / 395

[ Back to top ]