Fターム[5F110BB06]の内容

Fターム[5F110BB06]に分類される特許

381 - 395 / 395

キャパシタを含んだ集積回路構造およびその製造方法

特に、トランジスタ(122)(好ましくはFinFET)、および、キャパシタ(124)を備えた集積回路構造(120)を開示する。キャパシタ(124)の下部電極は、SOI基板ないに、トランジスタ(122)のチャネル部に沿って配置されている。これにより、本発明の回路構造(120)は、簡単に製造され、優れた電子特性を有している。  (もっと読む)

(もっと読む)

SOIおよびバルク・シリコン領域を含む半導体デバイス内のSTI形成

【課題】シリコン・オン・インシュレータ(SOI)領域およびバルク・シリコン領域内にシリコン・トレンチ分離部(STI)を形成する方法、および該方法により形成した半導体デバイスを開示する。

【解決手段】STIは、STIマスクを使用し、バルク・シリコン領域内の所望の深さまでエッチングし且つSOI領域の埋め込み絶縁体で停止する時限エッチングを実行し、SOI領域の埋め込み絶縁体を貫通してエッチングすることにより、SOI領域およびバルク・シリコン領域内で同時にSTIをエッチングすることができる。このプロセスの埋め込み絶縁体のエッチングは、ハードマスク除去ステップの一部として、それほど複雑でなく実行することができる。さらに、バルク領域とSOI領域の両方に同じ深さを選択することにより、その後のCMPプロセスでの問題が回避される。本発明は、窒化シリコンの残留物が存在することがあるSOI領域とバルク領域との境界において不要なものを取り除く。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ、半導体装置の製造方法および表示装置

【課題】 トランジスタ特性のバラツキを減少させた薄膜トランジスタの製造方法、薄膜トランジスタ、半導体装置の製造方法および表示装置を得ること。

【解決手段】 基板1上に少なくともソース領域14とチャネル領域16およびドレイン領域15を有する多結晶もしくは結晶化された結晶化半導体薄膜5が設けられ、この結晶化半導体薄膜5上にゲート絶縁膜11を介してゲート電極13が設けられた薄膜トランジスタの製造方法であって、ゲート絶縁膜11は、結晶化半導体薄膜5と略同一平面を形成するように基板1上に樹脂層10を形成したのち、この樹脂層10上および結晶化半導体薄膜5上に形成した膜である。

(もっと読む)

キャパシタと好ましくはプレーナ型のトランジスタとを有する集積回路構造およびその製造方法

プレーナ型であることが好ましいトランジスタ(142)とキャパシタ(144)とを有する集積回路構造(140)が開示されている。キャパシタ(44)の下部電極は、トランジスタ(142)のチャネル領域と共に、1つのSOI基板に配置されている。回路構造(140)は、簡単に製造でき、優れた電子特性を有している。  (もっと読む)

(もっと読む)

トランジスタ構造及びその製作方法

トランジスタ構造の少なくとも一部分が実質的に透明であるエンハンスメント・モード電界効果トランジスタである。該トランジスタの一変形形態は、ZnO、SnO2及びIn2O3から選択された実質的に絶縁性で実質的に透明な材料から構成されるチャネル層を含む。実質的に透明な材料から構成されるゲート絶縁体層は、チャネル層/ゲート絶縁体層境界面を形成するようにチャネル層に隣接して配置される。該トランジスタの第2の変形形態は、アニーリングにより生成される実質的に絶縁性のZnO、SnO2及びIn2O3から選択される実質的に透明な材料から構成されるチャネル層を含む。該トランジスタを含む装置、及び該トランジスタを作る方法も開示されている。  (もっと読む)

(もっと読む)

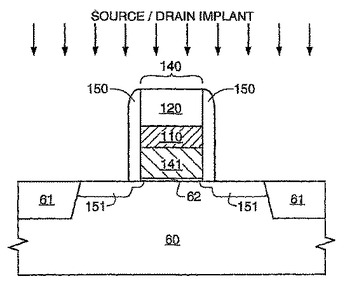

薄膜トランジスタの製造方法、半導体装置、電気光学装置及び電子機器

【課題】 1度の不純物注入工程によってLDD構造を形成することができる薄膜トランジスタの製造方法等を提供する。

【解決手段】 本発明は、ゲート絶縁膜上に、チャネル長方向において端部から中央部に向けて徐々に膜厚が厚くなる傾斜部を有するゲート電極20を形成する工程を含む薄膜トランジスタうの製造方法を提供する。該ゲート電極20をマスクとしてリンなどの不純物元素のイオン打ち込みを行うことで、最終的には図3(B)に示すようなソース/ドレイン領域としての高濃度のN+型不純物拡散領域22a、低濃度のN-型不純物拡散領域22b、及びチャネル領域24が形成される。

(もっと読む)

メモリ・ゲイン・セル、メモリ回路、およびゲイン・セルのための構造を形成する方法(水平メモリ・ゲイン・セル)

【課題】メモリ回路用のゲイン・セル、複数のゲイン・セルから形成されたメモリ回路、およびこのようなゲイン・セルおよびメモリ回路を製造する方法を提供する。

【解決手段】メモリ・ゲイン・セル64は、ストレージ・キャパシタ38と、ストレージ・キャパシタに電気的に結合された、ストレージ・キャパシタを充放電するための書込みデバイスと、読取りデバイスとを含む。読取りデバイスは、それぞれがソースおよびドレインの間に電気的に結合された1つまたは複数の半導電性カーボン・ナノチューブ50を含む。読取りゲート60およびストレージ・キャパシタによってそれぞれの半導電性カーボン・ナノチューブの一部がゲートされ、それによって、それぞれの半導電性カーボン・ナノチューブの中をソースからドレインへ流れる電流が調整される。この電流は、ストレージ・キャパシタによって蓄積されている電荷に比例する。

(もっと読む)

半導体記憶装置

【課題】 データの破壊を効果的に防止する。

【解決手段】 一対のメモリセルMCL、MCRのドレイン拡散領域14、ソース拡散領域15にシリサイド層18が埋め込まれ、シリサイド層18の底面はシリコン酸化膜11まで達している。

(もっと読む)

半導体記憶装置

SRAMメモリセルをFD-SOIトランジスタで構成し、駆動トランジスタを構成するSOIトランジスタの埋め込み酸化膜の下の層の電位を制御して、メモリセルの性能を向上させる。

【課題】

低電源電圧状態でのSRAM回路の性能を向上させる。

【解決手段】

FD-SOIトランジスタを用いて構成されたSRAMメモリセルにおいて、駆動トランジスタのBOX層下のウエル電位を制御することでVthを制御して電流を増加させて、メモリセルの安定動作を可能とする。

(もっと読む)

ゲート型電界効果デバイス及びその製法

本発明はゲート型電界効果デバイスに関し、その製法にも関する。一例では、ゲート型電界効果デバイスはソース/ドレーン領域ペアを含み、チャンネル領域をそれらの間に有している。ゲートはソース/ドレーン領域間でチャンネル領域に近接して受領される。ゲートはソース/ドレーン領域間にゲート幅部を有している。ゲート誘電体はチャンネル領域とゲートに近接して受領される。ゲート誘電体は少なくとも2つの異なる領域をゲートの幅部に沿って有している。これら異なる領域はそれぞれ異なる誘電率kを有する2つの異質領域を提供するように異なる材料で提供される。 (もっと読む)

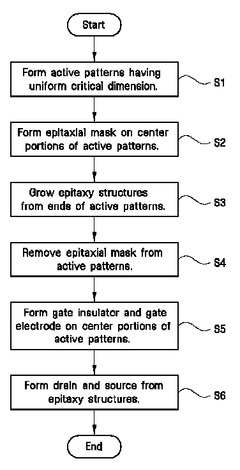

均一な臨界寸法のアクティブパターンで形成されたマルチゲートトランジスタ及びその製造方法

本発明は、均一な臨界寸法のアクティブパターンで構成されたマルチゲートトランジスタの製造方法を提供する。本発明はまた、均一な臨界寸法のアクティブパターンを具備するマルチゲートトランジスタを提供する。マルチゲートトランジスタの製造方法は先に少なくとも一つのアクティブパターンを形成する。以後、前記アクティブパターンの露出した領域から少なくとも一つのエピタキシ構造を成長させる。続いて、前記アクティブパターンの少なくとも2個の面にチャネル領域を形成する。  (もっと読む)

(もっと読む)

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

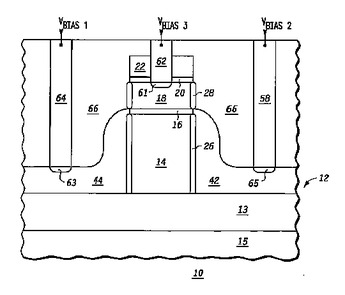

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

集積化金属珪化物ゲート電極を有するトランジスタの形成方法

集積化した金属珪化物トランジスタゲート電極を有するトランジスタを半導体アセンブリ内に形成する方法を提供する。トランジスタゲートは部分的に、金属を溝内に存在させた状態でエピタキシャルシリコンと反応させることにより製造する。前記溝内で前記金属珪化物上にトランジスタゲート分離キャップ層を形成する。任意ではあるが溝スペーサを設けて所定の製造処理の臨界的な寸法上の制約を低減させ、従って、形状寸法が臨界的な寸法よりも小さいトランジスタを形成しうるようにすることができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 より優れたソフトエラー耐性を有するSOI基板を用いた高信頼性のCMOS・SRAMセルを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 SOI基板の表面半導体層上にゲート絶縁膜を介して形成されたゲート電極と、該ゲート電極の両側の表面半導体層に形成された第1導電型ソース/ドレイン領域とから構成される半導体装置であって、前記第1導電型ソース/ドレイン領域の双方又は一方に接して第2導電型引出拡散層が形成され、少なくとも前記第1導電型ソース/ドレイン領域上から第2導電型引出拡散層上にわたってシリサイド層が形成されており、シリサイド層に接地電位が与えられてなる半導体装置。

(もっと読む)

381 - 395 / 395

[ Back to top ]