Fターム[5F110BB10]の内容

Fターム[5F110BB10]に分類される特許

121 - 140 / 451

光電変換装置及びその動作方法

【課題】応答特性を改善することによって異常値の出力を低減した光電変換装置を提供する。

【解決手段】フォトダイオードとカレントミラー回路を含む光電変換装置において、フォトダイオードに対して並列にダイオード接続されたトランジスタが設けられる。該トランジスタは、カレントミラー回路のゲート容量の蓄積電荷を急速に排出するためのリークパスとして作用し、光電変換装置の応答速度を改善するとともに異常値の出力を低減する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】現在、良質な膜を得るために、下地膜から非晶質シリコン膜までの形成プロセスは、各々の成膜室にて行われている。これらの成膜条件をそのまま用いて同一成膜室にて下地膜から非晶質シリコン膜までを連続形成すると、結晶化工程で十分に結晶化されない。

【解決手段】水素希釈したシランガスを用いて非晶質シリコン膜を形成することにより、下地膜から非晶質シリコン膜までを同一成膜室内で連続形成しても、結晶化工程で十分に結晶化可能となる。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置を提案することを課題とする。

【解決手段】基板上に形成されたゲート電極と、ゲート電極上に形成された酸素過剰のSiOX膜と、SiOX膜上に形成された酸化物半導体膜と、を有する半導体装置。

(もっと読む)

装置

【課題】軽量、薄型、小型であり、かつ読み込んだ画像に明るさのむらが生じないエリアセンサ及びエリアセンサを備えた表示装置を提供する。

【解決手段】エリアセンサが有する画素は、光源としてのEL(エレクトロルミネッセンス)素子と、光電変換素子としてのフォトダイオードと複数のTFTをそれぞれ有しており、EL素子とフォトダイオードの動作をTFTで制御していることを特徴とするエリアセンサ及びエリアセンサを備えた表示装置。

(もっと読む)

薄膜トランジスタおよびその製造方法、並びにその薄膜トランジスタを備えた装置

【課題】低温で作製可能であり、高い電界効果移動度を示す薄膜トランジスタを提供する。

【解決手段】酸化物半導体層からなる活性層を備えた薄膜トランジスタにおいて、活性層が、ゲート電極側から膜厚方向に第1の電子親和力χ1を有する第1の領域A1、第1の電子親和力χ1よりも小さい第2の電子親和力χ2を有する第2の領域A2とを含み、第1の領域A1を井戸層、第2の領域A2とゲート絶縁膜とを障壁層とする井戸型ポテンシャルを構成するものとする。ここで、活性層を、a(In2O3)・b(Ga2O3)・c(ZnO)から成る酸化物半導体層からなるものとし、第2の領域A2のb/(a+b)を第1の領域A1のb/(a+b)よりも大きくする。

(もっと読む)

半導体装置

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加

する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有す

るICチップをボンディング等により実装することが困難となり、製造コストが増大する

という問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少

なくとも一部の回路を、上下をゲート電極で挟んだ酸化物半導体を用いた薄膜トランジス

タで構成する。同一基板上に画素部及び駆動回路を設けることによって製造コストを低減

する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】信号書き込み時間が長くなることを防ぎながら、信号振幅値が大きく、かつ、入出力関係が線形で動作する範囲を大きくすることが出来る半導体装置およびその駆動方法を提供する。

【解決手段】増幅用トランジスタ101及びバイアス用トランジスタ102を有する半導体装置において、放電用トランジスタ108を設けて、プリ放電を行う。または、増幅用トランジスタ101及びバイアス用トランジスタ102を有する半導体装置において、バイアス用トランジスタ102に接続されたバイアス側電源線104の電位を、増幅用トランジスタに接続された増幅側電源線103の電位に近づけることにより、プリ放電を行う。

(もっと読む)

非単結晶トランジスタ集積回路

【課題】更に多機能化した非単結晶トランジスタ集積回路を提供する。

【解決手段】非単結晶トランジスタ集積回路は、第1の高分子フィルム11と、高分子フィルム11に設けられた共通電極12と、共通電極12に設けられた誘電体13と、誘電体13に設けられた第2の高分子フィルム14と、第2の高分子フィルム14に設けられ、圧力が加えられた際に、誘電体13の厚さの変化量を容量の変化として読み出す圧力センサ15と、第2の高分子フィルム14に設けられ、圧力センサ15を読み出すための非単結晶トランジスタ16とを具えることを特徴とする。

(もっと読む)

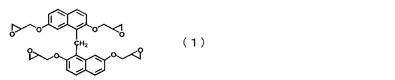

電子デバイス及びその製造方法、並びに、半導体装置及びその製造方法

【課題】従来よりも低い温度での形成が可能である絶縁層を備えた電子デバイスを提供する。

【解決手段】電子デバイスは、(A)制御電極12、(B)第1電極14及び第2電極14、並びに、(C)第1電極14と第2電極14との間であって、絶縁層13を介して制御電極12と対向して設けられた、有機半導体材料層15から成る能動層16を備えて成り、少なくとも能動層12と接触する絶縁層13の部分は、下記の式(1)にて示される材料を硬化して成る層から構成されている。 (もっと読む)

(もっと読む)

酸化物半導体薄膜およびその製造方法、並びに薄膜トランジスタ、薄膜トランジスタを備えた装置

【課題】生産性、組成均一性を向上させることができ、かつ低温アニール時に低抵抗化が起こらず、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適した酸化物半導体薄膜を得る。

【解決手段】In、GaおよびOを主たる構成元素とする酸化物半導体薄膜であって、In,Gaの組成比が3/4≦Ga/(In+Ga)≦9/10であり、かつ、抵抗率が1Ωcm以上、1×106Ωcm以下を満たすものとする。

(もっと読む)

酸化物半導体薄膜、薄膜トランジスタおよび薄膜トランジスタを備えた装置

【課題】IGZO系酸化物半導体薄膜において、膜中水分量を低減可能な組成を明らかにし、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適した酸化物半導体薄膜を得る。

【解決手段】In、Ga、ZnおよびOを主たる構成元素とする酸化物半導体薄膜において、In,Ga,Znの組成比をZn/(In+Ga+Zn)≦1/3、Ga/(In+Ga+Zn)≦9/11、4/5≦Ga/(In+Ga)≦1、且つIn/(In+Zn)≦1/2を満たすものとする。

(もっと読む)

酸化物半導体薄膜の製造方法および酸化物半導体薄膜、薄膜トランジスタの製造方法および薄膜トランジスタ、並びに薄膜トランジスタを備えた装置

【課題】300℃以上の高温での熱処理することなく、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適したIGZO系酸化物薄膜を製造する。

【解決手段】In,Ga,Zn,Oを主たる構成元素とし、組成比が11/20≦Ga/(In+Ga+Zn)≦9/10、且つ3/4≦Ga/(In+Ga)≦9/10、且つZn/(In+Ga+Zn)≦1/3を満たす酸化物半導体薄膜をスパッタリング法により、アルアゴンガス雰囲気下で酸素ガスを導入することなく成膜し、成膜された酸化物半導体薄膜に対して、酸化性雰囲気中で100℃以上、300℃未満の熱処理を施す。

(もっと読む)

酸化物半導体薄膜の製造方法および該製造方法により作製された酸化物半導体薄膜、薄膜トランジスタ、並びに薄膜トランジスタを備えた装置

【課題】低温アニールによる低抵抗化が起こらず、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適したIGZO系酸化物薄膜を製造する。

【解決手段】In,Ga,Zn,Oを主たる構成元素とし、組成比が11/20≦Ga/(In+Ga+Zn)≦9/10、且つ3/4≦Ga/(In+Ga)≦1、且つZn/(In+Ga+Zn)≦1/3を満たす酸化物半導体薄膜を成膜する成膜工程と、成膜された酸化物半導体薄膜に対して、酸化性雰囲気中で100℃以上、300℃以下の熱処理を施す熱処理工程とを含み、熱処理工程後の酸化物半導体薄膜の抵抗率が1Ωcm以上、1×106Ωcm以下となるように、成膜工程における成膜条件および熱処理工程における熱処理条件を設定する。

(もっと読む)

固体撮像装置、半導体表示装置

【課題】撮像された画像の品質を向上させる固体撮像装置、或いは半導体表示装置を提供する。

【解決手段】グローバルシャッタ方式で駆動を行うことで、電荷の蓄積動作を制御するための電位を全画素で共有することができる。さらに、出力信号が与えられる一の配線に接続されている複数のフォトセンサを第1のフォトセンサ群とし、出力信号が与えられる他の配線に接続されている複数のフォトセンサを第2のフォトセンサ群とすると、電荷の蓄積動作を制御するための電位または信号を第1のフォトセンサ群に与える配線と、上記電位または信号を第2のフォトセンサ群に与える配線とを、接続する。

(もっと読む)

薄膜トランジスタの製造方法

【課題】

転写型に形成された絶縁膜を基板上に形成された接着膜に転写する際、接着膜の膜厚の不均一を低減する薄膜トランジスタの製造方法を提供する。

【解決手段】

凹凸パターンが形成された転写型に半導体膜を形成する半導体膜形成ステップS11と、半導体膜が形成された転写型に絶縁膜を形成する絶縁膜形成ステップS12と、基板上に予め形成された電極上に接着膜を形成する接着膜形成ステップS02と、接着膜を硬化させる硬化ステップS03と、硬化した接着膜を介して電極上に絶縁膜および半導体膜を転写する転写ステップS21とを備える。

(もっと読む)

光電変換素子、光電変換素子の作製方法、表示装置及び電子機器

【課題】耐久性の高い光電変換素子を作製する。

【解決手段】基板上の第1の導電層と、第1の導電層を覆う第1の絶縁層と、第1の絶縁層上の第1の半導体層と、第1の半導体層上に設けられた第2の半導体層と、第2の半導体層上の不純物半導体層と、不純物半導体層上の第2の導電層と、第1の半導体層と第2の導電層を覆う第2の絶縁層と、第2の絶縁層上の透光性を有する第3の導電層と、を有し、第2の絶縁層は、第1の開口部と第2の開口部を有し、第1の開口部では、第1の半導体層と第3の導電層が接続され、第2の開口部では、第1の導電層と第3の導電層が接続され、第1の開口部に、第2の導電層により構成された電極に囲まれた受光部を有する光電変換素子とする。

(もっと読む)

電界効果トランジスタ

【課題】インジウムを主要成分とし、金属半導体接合を用いた電界効果トランジスタのオフ電流を低減せしめる構造を提供する。

【解決手段】インジウムを主要成分とする、厚さ0.1〜100nmの第1の酸化物半導体(例えば、酸化インジウム)よりなる第1の半導体層1の一方の面に絶縁膜4を設け、他の面に接して、I型の第2の酸化物半導体(例えば、酸化ガリウム)よりなる第2の半導体層2を設ける。第2の酸化物半導体の真空準位からフェルミレベルまでのエネルギー差は第1の酸化物半導体のものよりも大きい。上記の条件を満たす第2の酸化物半導体との接触面近傍においては、極めてキャリア濃度の低い領域(準I型領域)となるので、その部分をチャネルとすることにより、オフ電流が低減できる。また、FETのドレイン電流は移動度の高い第1の酸化物半導体を流れるので、大電流を取り出せる。

(もっと読む)

撮像装置、表示撮像装置および電子機器

【課題】製造工程を複雑化させることなく、光検出素子および駆動素子において高い特性を示すことが可能な撮像装置、表示撮像装置および電子機器を提供する。

【解決手段】光検出素子3におけるI層32I(チャネル領域,半導体層)と、TFT素子2におけるI層22I(チャネル領域,半導体層)とにおいて、それらの厚みおよび不純物濃度がそれぞれ互いに略等しくなっている。I層22I,32Iにおける平均トラップ順位密度がそれぞれ、2.0×1017(cm-3)以下となっている。2種類の半導体層(I層22I,32I)を、同一の工程で簡易に形成することができる。また、光検出素子3およびTFT素子2における特性をそれぞれ、高い値で両立させることができる。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】柱状結晶構造を有する金属を用いた場合でも、簡便な方法で、再現性良く階段構造状のテーパーを有する電極を形成する。

【解決手段】真空状態を保ったままの状態において、同一種類の金属を用いて、スパッタリング法で少なくとも2層の金属膜を成膜する成膜工程と、該成膜工程によって成膜された複数の金属膜にエッチング処理を施すことにより、階段構造状のテーパー形状を端部に有する、ゲート電極、ソース電極およびドレイン電極のうちの少なくとも1つを形成するエッチング工程とによって薄膜トランジスタを製造する。

(もっと読む)

121 - 140 / 451

[ Back to top ]