Fターム[5F110CC03]の内容

Fターム[5F110CC03]の下位に属するFターム

逆コプレナドープ (81)

Fターム[5F110CC03]に分類される特許

161 - 180 / 2,536

有機薄膜、その製造方法、及びそれを有する有機トランジスタ

【課題】高い配向性及び高い硬膜度の有機薄膜、及びその製造方法の提供。

【解決手段】少なくとも1種の重合性液晶化合物を含有する組成物の配向を、プラズマ照射による重合により固定してなる有機薄膜である。また、少なくとも1種の重合性液晶化合物を含有する組成物を配向させること、前記組成物を配向させるとともに、又は配向させた後に、前記組成物にプラズマを照射して重合を進行させて、配向を固定すること、

を含む有機薄膜の製造方法である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

薄膜デバイスの製造方法、薄膜デバイス基材、及び、薄膜デバイス

【課題】従来公知のデバイス素子の形成手法を広く一般的に使用でき、かつ、品質にも優れた薄膜デバイスの製造方法を提供する。

【解決手段】一例として、強磁性体層11の表面側に絶縁層12を積層して、可撓性の薄膜デバイス基材を得る積層工程と、薄膜デバイス基材を支持するために、前記強磁性体層の裏面側に、強磁性体層と引き合う磁性平板21を磁力で密着させる支持板密着工程と、薄膜デバイス基材の前記絶縁層上にデバイス素子13を形成する素子形成工程と、強磁性体層の裏面側から磁性平板21を取り外す支持板離脱工程と、を備える薄膜デバイスの製造方法である。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

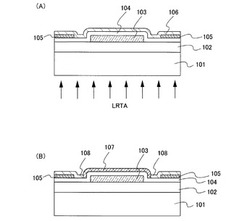

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】酸化物半導体膜を有するボトムゲート構造のトランジスタの作製工程において、熱処理による脱水化または脱水素化処理、及び酸素ドープ処理を行う。熱処理による脱水化または脱水素化処理を行った酸化物半導体膜を含み、且つ、作製工程において酸素ドープ処理されたトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジスタのしきい値電圧の変化量が低減できており、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置、表示モジュール、及び電子機器

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

酸化物半導体素子、酸化物半導体素子の製造方法、酸化物半導体素子を含む表示装置、及び酸化物半導体素子を含む表示装置の製造方法

【課題】酸化物半導体素子、酸化物半導体素子の製造方法、酸化物半導体素子を含む表示装置、及び酸化物半導体素子を含む表示装置の製造方法を提供すること。

【解決手段】酸化物半導体素子は、基板上に配置されるゲート電極と、リセス構造を含むゲート絶縁層と、ゲート絶縁層の一側上に配置されるソース電極と、ゲート絶縁層の他側上に配置されるドレーン電極と、ゲート絶縁層、ソース電極、及びドレーン電極上に配置されるアクティブパターンとを含むようにすることができる。リセス構造はゲート電極の上部に位置するようにすることができ、アクティブパターンはリセス構造を埋め立てるようにすることができる。酸化物半導体素子がリセス構造を有するゲート絶縁層を具備することによって、電荷移動度、閾値電圧分布、動作電流などの多様な電気的特性を向上させることができる。

(もっと読む)

アクティブマトリックス基板及びアクティブマトリックス基板の製造方法、液晶表示装置

【課題】画素電極の電圧が保持され、画質が悪化することがないアクティブマトリックス基板を提供する。

【解決手段】本発明のアクティブマトリクス基板は、基材110上で半導体層150と接触するように設けられ、互いに対向しチャネル領域を形成するソース電極120及びドレイン電極130と、前記チャネル領域を制御するゲート電極140と、前記ドレイン電極130と接続され液晶材料を駆動する画素電極190と、を複数有するアクティブマトリクス基板において、複数の前記画素電極190の間の空間に配された無機絶縁膜195と、前記画素電極190とは接触せずに、前記無機絶縁膜195と接触するようにして配された遮光膜200と、を有することを特徴とする。

(もっと読む)

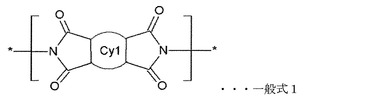

有機保護膜組成物およびこれから製造される有機保護膜を含む薄膜トランジスタ、並びに電子素子

【課題】有機薄膜トランジスタの長期的な信頼性を向上させることのできる有機保護膜組成物を提供する。

【解決手段】下記の一般式1および一般式2の構造単位を含むオリゴマーまたはポリマーと、架橋剤と、を含む。

(もっと読む)

(もっと読む)

有機薄膜トランジスタ及び有機薄膜トランジスタの製造方法

【課題】有機半導体層の形成位置について、別途精密な制御を必要とすることなく、高精細なパターニングが行われた有機半導体層を有する有機薄膜トランジスタ及びその製造方法を提供することにある。

【解決手段】ソース電極1、ドレイン電極2、ゲート電極3、有機半導体層4及びゲート絶縁膜5を備え前記ソース電極1及び前記ドレイン電極2の表面エネルギーが、いずれも30mN/m以下であることを特徴とする。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート

電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第

2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジ

スタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトラ

ンジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

薄膜素子組立体

【課題】巻き取りを行っても傷や損傷が発生し難い構成、構造を有する薄膜素子組立体を提供する。

【解決手段】薄膜素子組立体にあっては、可撓性を有する基材20の第1面21上に複数の薄膜素子10が備えられており、基材20において、複数の薄膜素子10が備えられた第1領域の外側に、薄膜素子を備えていない第2領域が設けられており、基材20の第1面21の第2領域、又は、第2面22の第2領域、又は、第1面21及び第2面22の第2領域に凸部31が形成されている。

(もっと読む)

半導体装置

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置を提供することを目的

の一とする。

【解決手段】13族元素および酸素を含む第1の絶縁膜と、第1の絶縁膜と一部が接する

酸化物半導体膜と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と

、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜とゲート電極の間の、酸化物

半導体膜と一部が接する第2の絶縁膜と、を有する半導体装置である。また、13族元素

および酸素を含む第1の絶縁膜には、化学量論的組成比より酸素が多い領域が含まれる構

成とする。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】溝部および該溝部を挟んで形成された一対の低抵抗領域を有する半導体基板と、半導体基板上の第1のゲート絶縁膜と、第1のゲート絶縁膜を介し、溝部と重畳するゲート電極と、ゲート電極を覆って設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜上の、溝部を挟んで設けられた一対の電極と、一対の電極と接する半導体膜と、を有し、一対の低抵抗領域の一方と、一対の電極の一方が電気的に接続されている積層されたトランジスタを形成し、一方はn型半導体からなるトランジスタであり、他方はp型半導体からなるトランジスタにより形成させることによって、相補型MOS回路を形成する。

(もっと読む)

半導体装置及びその駆動方法

【課題】2つの電位の誤差を増幅して出力する半導体装置におけるスタンバイ状態からの復帰に際して生じる動作遅延を抑制する。

【解決手段】チャネルが酸化物半導体層に形成されるトランジスタによって、トランスコンダクタンスアンプの出力端子とキャパシタの一方の電極の電気的な接続を制御する。よって、トランスコンダクタンスアンプがスタンバイ状態となる場合であっても、当該トランジスタをオフ状態とすることでキャパシタの一方の電極において長期に渡って電荷の保持を行うことが可能となる。また、トランスコンダクタンスアンプをスタンバイ状態から復帰する際には、当該トランジスタをオン状態とすることで、キャパシタの充放電を早期に収束させることができる。これにより、早期に当該半導体装置の動作を定常状態とすることが可能となる。

(もっと読む)

薄膜トランジスタ基板の製造方法およびトップゲート構造薄膜トランジスタ基板

【課題】本発明は、簡便な工程で製造可能な、電荷注入効率に優れた薄膜トランジスタ基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、基板上に金属電極層を形成する金属電極層形成工程と、上記金属電極層の上面に、電子吸引性または電子供与性の官能基を有する表面処理剤で表面処理を行うことにより、表面処理層積層体を形成する表面処理工程と、上記表面処理層積層体をパターニングし、ソース電極およびドレイン電極を形成するパターニング工程と、上記ソース電極および上記ドレイン電極上に有機半導体層を形成する有機半導体層形成工程と、上記有機半導体層上にゲート絶縁層を形成するゲート絶縁層形成工程と、上記ゲート絶縁層上にゲート電極を形成するゲート電極形成工程と、を有することを特徴とする薄膜トランジスタ基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

半導体装置

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】13族元素および酸素を含む第1の絶縁膜と、第1の絶縁膜と一部が接する酸化物半導体膜と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜とゲート電極の間の、酸化物半導体膜と一部が接する第2の絶縁膜と、を有する半導体装置である。また、13族元素および酸素を含む第1の絶縁膜には、化学量論的組成比より酸素が多い領域が含まれる構成とする。

(もっと読む)

アクティブマトリックス基板及びアクティブマトリックス基板の製造方法、液晶表示装置

【課題】電極からの反射がなく、表示画像が悪化することがないアクティブマトリックス基板を提供する。

【解決手段】本発明のアクティブマトリクス基板は、基板110側と反対側に反射防止層130が形成された反射防止層130が形成された電極(図14のAに相当するソースドレイン電極層)と、基板110側と反対側に反射防止膜が形成されていない反射防止膜除去電極(図14のBに相当するソースドレイン電極層)と、基板110上に設けられた親液性領域Rと、反射防止膜除去電極とに接するように形成された半導体層150と、を有している。

(もっと読む)

酸化物半導体膜、及び半導体装置

【課題】電気伝導度の安定した酸化物半導体膜を提供する。また、当該酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】インジウム(In)、ガリウム(Ga)、及び亜鉛(Zn)を含む酸化物半導体膜において、酸化物半導体膜は、酸化物半導体膜の被形成面の法線ベクトルに平行な方向に揃うc軸配向した結晶領域を有し、c軸配向した結晶領域の組成が、In1+δGa1−δO3(ZnO)m(ただし、0<δ<1、m=1〜3)で表され、c軸配向した結晶領域を含む全体の酸化物半導体膜の組成が、InxGayO3(ZnO)m(ただし、0<x<2、0<y<2、m=1〜3)である。

(もっと読む)

表示装置

【課題】簡便な構成及び動作によって表示装置の消費電力を低減すること。

【解決手段】表示装置が入力デバイスを備え、該入力デバイスから出力される画像操作信号に応じて、駆動回路に対する画像信号の入力を制御する。具体的には、入力デバイスが操作されない際の画像信号の入力頻度を、入力デバイスが操作される際の画像信号の入力頻度よりも低くする。これにより、当該表示装置が使用される際の表示の劣化(表示品質の低下)を抑制することが可能となり、且つ使用されない際の消費電力を低減することが可能になる。

(もっと読む)

161 - 180 / 2,536

[ Back to top ]