Fターム[5F110CC03]の内容

Fターム[5F110CC03]の下位に属するFターム

逆コプレナドープ (81)

Fターム[5F110CC03]に分類される特許

141 - 160 / 2,536

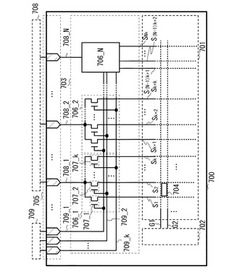

表示装置及び電子機器

【課題】信号線駆動回路が有するスイッチ回路を画素部と同じ基板上に配置する構成において、スイッチ回路を構成するトランジスタサイズを縮小し、データを供給することによる信号線の充放電を行う際の回路内の負荷を削減する

【解決手段】映像信号が入力される画素部と、映像信号の画素部への出力を制御するためのスイッチ回路部を有する信号線駆動回路を有し、スイッチ回路部は、絶縁基板上において、電界効果移動度が少なくとも80cm2/Vs以上であるトランジスタを有し、トランジスタは、酸化物半導体層を有する。

(もっと読む)

固体撮像装置、半導体表示装置

【課題】非接触にて、被写体の位置情報の取得を容易に行うことができる固体撮像装置、または半導体表示装置の提供。

【解決手段】第1入射方向から第1入射角を有する光が入射する複数の第1フォトセンサと、第1入射方向とは異なる第2入射方向から第2入射角を有する光が入射する複数の第2フォトセンサとを有し、複数の第1フォトセンサのうち、第1入射方向の上流側の一つの第1フォトセンサの方が、第1入射方向の下流側の他の一つの第1フォトセンサよりも、第1入射角が大きく、複数の第2フォトセンサのうち、第2入射方向の上流側の一つの第2フォトセンサの方が、第2入射方向の下流側の他の一つの第2フォトセンサよりも、第2入射角が大きい。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、非晶質酸化物半導体膜を形成し、該非晶質酸化物半導体膜に酸素を導入して酸素を過剰に含む非晶質酸化物半導体膜を形成する。該非晶質酸化物半導体膜上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体膜の少なくとも一部を結晶化させて、結晶性酸化物半導体膜を形成する。

(もっと読む)

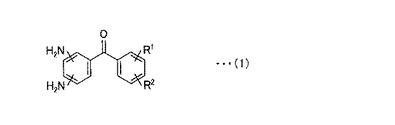

積層構造体及びその製造方法

【課題】紫外線照射による表面自由エネルギーの変化が大きい積層構造体並びに該積層構造体を有する電子素子アレイ、画像表示媒体及び画像表示装置を提供する。

【解決手段】積層構造体10は、基板11上に、ポリイミドを含む濡れ性変化層12及び導電体層13が順次積層されており、ポリイミドは、ポリアミド酸を脱水閉環させて得られ、ポリアミド酸は、ジアミンとテトラカルボン酸二無水物を開環重付加させて得られ、ジアミンは、一般式(1)で表される化合物を含む。 (もっと読む)

(もっと読む)

記憶装置

【課題】回路面積を小さくする。

【解決手段】記憶データとしてデータを記憶するメモリセルと、出力信号線と、電圧が与えられる配線と、を具備し、メモリセルは、記憶データと検索データの比較演算を行い、演算結果に応じて導通状態又は非導通状態になる比較回路と、記憶データの書き込み及び保持を制御する電界効果トランジスタと、を備え、比較回路が導通状態のときに、出力信号線の電圧値が配線の電圧と同等の値になる記憶装置。

(もっと読む)

記憶装置

【課題】記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

【解決手段】基板に設けられた駆動回路と、駆動回路上に設けられ、駆動回路によって駆動される複数のメモリセルアレイと、を有し、複数のメモリセルアレイはそれぞれ複数のメモリセルを有し、複数のメモリセルはそれぞれ、酸化物半導体層と重畳する第1のゲート電極と、を有する第1のトランジスタと、ソース電極又はドレイン電極と、第1のゲート絶縁層と、導電層と、を有する容量素子と、を有し、複数のメモリセルアレイは重ねて配置される。こうして、記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

(もっと読む)

フォトセンサの駆動方法、半導体装置の駆動方法、半導体装置、及び電子機器

【課題】小型でコントラストの高い画像データを取得することができるフォトセンサを提供する。該フォトセンサを用いた半導体装置を提供する。

【解決手段】受光素子と、スイッチング素子であるトランジスタと、トランジスタを介して受光素子と電気的に接続する電荷保持ノードとを有するフォトセンサにおいて、導通状態から非導通状態とするためにトランジスタへ供給する駆動パルスの入力波形の立ち下がり時間を遅延させ、電荷保持ノードが保持する電荷の減少を抑制する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】フォトセンサを有する半導体装置において、外光のノイズを軽減し、且つトランジスタのオフ電流によるリークが原因となるノイズも低減する。

【解決手段】マトリクス状に配置された複数のフォトセンサを有する。複数のフォトセンサはそれぞれ、光電変換素子と増幅回路とを有する。バックライトを点灯して被検出物に光を照射して第p行目のフォトセンサでリセット動作及び蓄積動作を行った後、バックライトを非点灯として第(p+1)行目のフォトセンサでリセット動作及び蓄積動作を行い、その後全行のフォトセンサの選択動作を順次行う。隣接する行のフォトセンサで得られた出力信号の差分を取得し、差分を用いて被検出物の撮像画像の生成や被検出物の存在する領域の検出を行う。増幅回路は蓄積された電荷を保持するトランジスタを有し、当該トランジスタはチャネルが酸化物半導体層に形成される。

(もっと読む)

半導体集積回路

【課題】半導体集積回路における消費電力を低減すること。また、半導体集積回路における動作の遅延を低減すること。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

EL表示装置および電子機器

【課題】画素部と同じ絶縁基板上において、大きな電流供給能力が得られるトランジスタで構成される電源線駆動回路を備えたEL表示装置を提供する。

【解決手段】絶縁基板上に複数の画素と複数の信号線、複数の走査線、及び複数の電源線を有するアクティブマトリクス型表示装置において、前記絶縁基板上に電界効果移動度が少なくとも80cm2/Vs以上、好ましくは120cm2/Vs以上を有する酸化物半導体のトランジスタを有し、トランジスタを1つの構成要素とする電源線駆動回路を有するEL表示装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、更にソース線を削減することにより単位面積あたりの記憶容量を増加させる。

(もっと読む)

酸化物薄膜トランジスタ及びその製造方法

【課題】短チャネルを実現し、薄膜トランジスタの性能を向上させる酸化物薄膜トランジスタ及びその製造方法を提供する。

【解決手段】本発明による酸化物薄膜トランジスタの製造方法は、基板110上に第1導電膜からなるゲート電極121及びゲートライン116を形成する段階と、ゲート電極121及びゲートライン116が形成された基板110上にゲート絶縁膜115aを形成する段階と、ハーフトーン露光を用いて、ゲート絶縁膜115aが形成されたゲート電極121の上部に第2導電膜からなるソース電極122、第1ドレイン電極123、及び第1データライン117を形成し、かつ第1ドレイン電極123の延長部及び第1データライン117上に第3導電膜からなる第2ドレイン電極123’及び第2データライン117’を形成する段階と、ソース電極122及び第1ドレイン電極123上に酸化物半導体からなるアクティブ層124を形成する段階とを含む。

(もっと読む)

入出力装置

【課題】光電変換素子に対するトランジスタの数を低減する。

【解決手段】表示データ信号のデータに応じた表示状態になる表示回路と、それぞれ入射する光の照度に応じた光データを生成する複数の光検出回路と、を含み、光検出回路は、X個(Xは2以上の自然数)の光電変換素子131と、ソース及びドレインの一方がX個の光電変換素子のうちの一つの光電変換素子の第2の電流端子に電気的に接続され、ゲートに光検出回路制御部からX個の電荷蓄積制御信号うち一つの電荷蓄積制御信号が入力されるX個の電荷蓄積制御トランジスタTXと、ゲートがX個の電荷蓄積制御トランジスタのソース及びドレインの一方のそれぞれに電気的に接続される増幅トランジスタ132と、を備える。

(もっと読む)

有機半導体素子の製造方法および有機半導体素子

【課題】本発明は、有機半導体層の移動度を低下させることなく、容易に有機半導体層をパターニングした有機半導体素子を得ることができる有機半導体素子の製造方法を提供することを主目的とする。

【解決手段】本発明は、ソース電極およびドレイン電極を覆うように、低分子有機半導体材料を有する有機半導体層を形成する有機半導体層形成工程と、上記ソース電極および上記ドレイン電極間のチャネル領域を含むように、上記有機半導体層上に第一誘電体層を形成する第一誘電体層形成工程と、上記低分子有機半導体材料を溶解することができる溶媒で、上記有機半導体層の一部を洗浄することにより、第一誘電体層非形成領域の上記有機半導体層を除去する洗浄除去工程と、上記第一誘電体層を覆うように第二誘電体層を形成する第二誘電体層形成工程と、を有することを特徴とする有機半導体素子の製造方法を提供することにより、上記課題を解決する。

(もっと読む)

半導体装置

【課題】開示する発明の一態様は、安定して動作することが可能なパルス信号出力回路及

びそれを含むシフトレジスタを提供することを課題の一とする。

【解決手段】開示する発明の一態様のパルス信号出力回路は、第1乃至第10のトランジ

スタを有し、第1のトランジスタおよび第3のトランジスタのチャネル長Lに対するチャ

ネル幅Wの比W/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタ

のW/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは

、第7のトランジスタのW/Lと等しく、第3のトランジスタのW/Lは、第4のトラン

ジスタのW/Lよりも大きくする。これによって、安定して動作することが可能なパルス

信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

有機薄膜、その製造方法、及びそれを有する有機トランジスタ

【課題】高い配向性及び高い硬膜度の有機薄膜、及びその製造方法の提供。

【解決手段】少なくとも1種の重合性液晶化合物を含有する組成物の配向を、プラズマ照射による重合により固定してなる有機薄膜である。また、少なくとも1種の重合性液晶化合物を含有する組成物を配向させること、前記組成物を配向させるとともに、又は配向させた後に、前記組成物にプラズマを照射して重合を進行させて、配向を固定すること、

を含む有機薄膜の製造方法である。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、酸化物半導体層と電気的に

接続するソース電極層またはドレイン電極層との接触抵抗の低減を図ることを課題の一と

する。

【解決手段】ソース電極層またはドレイン電極層を2層以上の積層構造とし、その積層の

うち、酸化物半導体層と接する一層を酸化物半導体層の仕事関数より小さい仕事関数を有

する金属又はそのような金属の合金とする。二層目以降のソース電極層またはドレイン電

極層の材料は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述

した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。

(もっと読む)

薄膜トランジスタ及びアレイ基板の製造方法

【課題】従来のボトムゲートのトップコンタクト構造の薄膜トランジスタを製造する時、使用されるマスクの数が多いので、該薄膜トランジスタの製造コストが高くなる。

【解決手段】ソース・ドレイン電極及びパターニングされた活性層を製造するためのマスクに、チャンネル領域に対応する幅が露光装置の分解能より小さいスリットを形成し、露光量を大きくすることで、ソース・ドレイン電極を通常に形成でき、さらに該マスクを用い、露光量を小さくすることで、所望形状の活性層を形成できる。

(もっと読む)

141 - 160 / 2,536

[ Back to top ]