Fターム[5F110CC04]の内容

Fターム[5F110CC04]に分類される特許

1 - 20 / 81

三次元集積回路を作製する方法

【課題】集積回路を作製する新規なタイプの方法を提供する。

【解決手段】少なくとも第3の層がその間に配置された、少なくとも半導体の第1および第2の層を備える基板を作製するステップと、少なくとも第1のMOSデバイスを作製するステップであって、その活性領域が半導体の第1の層の少なくとも一部に形成される、ステップと、少なくとも第2のMOSデバイスを作製するステップであって、その活性領域が半導体の第2の層の少なくとも一部に形成され、第2のMOSデバイスの活性領域が第2のMOSデバイスのゲートと第1のMOSデバイスの活性領域との間に配置される、ステップとを少なくとも含む、集積電子回路を作製する方法。

(もっと読む)

半導体装置の作製方法

【課題】信頼性が高く、ソースとドレインの間にリーク電流が生じにくく、コンタクト抵抗が小さい半導体装置を提供する。

【解決手段】酸化物半導体膜により形成されるトランジスタの電極膜上に酸化物半導体膜に接して設けられた第1の絶縁膜、及び第2の絶縁膜を積層して形成し、第2の絶縁膜上にエッチングマスクを形成し、エッチングマスクの開口部と重畳する部分の第1の絶縁膜及び第2の絶縁膜をエッチングして電極膜を露出する開口部を形成し、第1の絶縁膜及び第2の絶縁膜の開口部をアルゴンプラズマに曝し、エッチングマスクを除去し、第1の絶縁膜及び第2の絶縁膜の開口部に導電膜を形成し、第1の絶縁膜は加熱により酸素の一部が脱離する絶縁膜であり、第2の絶縁膜は第1の絶縁膜よりもエッチングされにくく、第1の絶縁膜よりもガス透過性が低い。または逆スパッタリングを行ってもよい。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と該酸化物半導体膜と接する下地となる膜との界面の電子状態が良好なトランジスタ。

【解決手段】下地となる膜は酸化物半導体膜と同様の原子配列を有し、下地となる膜と酸化物半導体膜とが接している面において、面内の下地膜の最隣接原子間距離と酸化物半導体の格子定数の差を、下地となる膜の同面内における最隣接原子間距離で除した値は0.15以下、好ましくは0.12以下、さらに好ましくは0.10以下、さらに好ましくは0.08以下とする。例えば、立方晶系の結晶構造を有し(111)面に配向する安定化ジルコニアを含む下地となる膜上に酸化物半導体膜を成膜することで、下地となる膜の直上においても結晶化度の高い結晶領域を有する酸化物半導体膜が得られる。

(もっと読む)

電子素子用金属層、電子素子用金属層積層体、電子素子、トランジスタ素子

【課題】電流のリークを抑制する電子素子用金属層を提供する。

【解決手段】被形成面12に、金属インクを塗布し金属粒子層を形成しパターニングする。基板側からランプ照射し、金属粒子層の下層部分のみを溶融させ、下層部分の金属粒子どうしを融着させる。金属粒子の融着層14Aと金属粒子の非融着層14Bとをこの順で有する積層体で構成されたゲート電極14とする。

(もっと読む)

半導体装置

【課題】半導体装置におけるドレイン電極端での電界集中を緩和する。

【解決手段】第1の領域および第2の領域を有する酸化物半導体膜と、該酸化物半導体膜と一部が接する一対の電極と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を介し、一対の電極の一方の一部および第1の領域と重畳するゲート電極と、を有し、第1の領域の少なくとも一部および第2の領域の少なくとも一部は一対の電極間にあり、ゲート電極は、一対の電極の他方と重畳しない構成とする。

(もっと読む)

半導体装置

【課題】トランジスタ領域におけるゲート間距離などのレイアウトに依存することなく、半導体層のチャネル領域に有効に応力を作用させることができる半導体装置を実現する。

【解決手段】MOSトランジスタを備える半導体装置の構成として、素子分離層4で素子分離されたトランジスタ領域を有する半導体層3と、トランジスタ領域で半導体層3の第1の面上にゲート絶縁膜5を介して形成されたゲート電極6と、トランジスタ領域で半導体層3の第1の面と反対側の第2の面上に形成された応力膜31とを備え、応力膜31は、シリサイド膜を用いて形成されている。

【選択図】図13  (もっと読む)

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果による電気特性の変動が生じにくい、チャネル領域に酸化物半導体を含むトランジスタを用いた半導体装置を作製する。

【解決手段】窒素を含む一対の酸窒化物半導体領域、および該一対の酸窒化物半導体領域に挟まれる酸化物半導体領域を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体領域上に設けられるゲート電極とを有する半導体装置。ここで、一対の酸窒化物半導体領域はトランジスタのソース領域およびドレイン領域となり、酸化物半導体領域はトランジスタのチャネル領域となる。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】容易に薄膜トランジスタを作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、基板10と第1絶縁膜11の間に駆動トランジスタ6の第1ゲート電極6aを形成する工程と、第2絶縁膜5d上にスイッチトランジスタ5の第2ゲート電極5aを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、駆動トランジスタ6の第1ゲート電極6aと、スイッチトランジスタ5の第2ゲート電極5aを形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】電磁波又は光が照射されても広義のリーク電流が増大せず、書き込み状態及び消去状態の安定した判別を可能とする。

【解決手段】電磁波シールド性能及び遮光性能を持つ層30及び31のどちらにも半導体層60の領域面積よりも大きい領域面積を持たせ、且つこの層30及び31を、半導体層60の上下を挟み込むように設けることで、電磁波及び光が半導体層60に侵入することを防ぐことができる。この結果、広義のリーク電流が格段に低減され、書き込み状態及び消去状態の判別を安定して行うことができる。

(もっと読む)

薄膜トランジスタ基板及び薄膜トランジスタ基板の製造方法

【課題】薄膜トランジスタの導通不良などの欠陥の低減を図る。

【解決手段】基板10と、基板10上に形成されたゲート電極5aと、ゲート電極5a上において、ゲート電極5aを挟む配置にそれぞれ離間して設けられたソース電極5iとドレイン電極5hと、ソース電極5iの少なくとも一部、ドレイン電極5hの少なくとも一部及びソース電極5iとドレイン電極5hとの間の領域を覆うように一体に形成され結晶性シリコンを含む半導体層50とを備え、半導体層50は、一端側で前記ソース電極5iの少なくとも一部を覆う部分と他端側でドレイン電極5hの少なくとも一部を覆う部分とであってドーパントを含む一対の不純物半導体膜部5f、5gと、一対の不純物半導体膜部5f、5gの間に形成された半導体膜部5bとを有する薄膜トランジスタ基板を提供する。

(もっと読む)

半導体装置の製造方法

【課題】転写元基板上に形成された被転写層を転写先基板に転写して半導体装置を製造する際に、転写元基板を容易に剥離できる半導体装置の製造方法を提供すること。

【解決手段】転写元基板1の表面に剥離層2を形成する工程と、前記剥離層2上に被転写層5を形成する工程と、前記転写元基板1の裏面に引っ張り応力を有する剥離助長層6を形成する工程と、前記被転写層5上に転写先基板8を接着する工程と、前記剥離層2に光または熱を照射して前記被転写層5を剥離する工程と、を含むことを特徴とする。

(もっと読む)

半導体装置

【課題】様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供する。

【解決手段】強磁性材料からなるシートを支持体とし、前記強磁性材料からなるシートに接する接着材と、該接着材に接する絶縁膜上に素子とを備える。上記構成において、前記素子は、薄膜トランジスタ、有機化合物を含む層を有する発光素子、液晶を有する素子、メモリー素子、薄膜ダイオード、シリコンのPIN接合からなる光電変換素子、またはシリコン抵抗素子であってもよい。また、上記各構成において、前記強磁性材料からなるシートは、軟質磁性粉体と合成樹脂とを混合して形成され、着磁されたものであってもよい。

(もっと読む)

トランジスタ回路

【課題】 高耐圧の薄膜トランジスタと高電流駆動能力を持った薄膜トランジスタを同一基板上に形成する。

【解決手段】 絶縁性基板上に形成され、半導体層、ソース領域、ドレイン領域で構成される薄膜トランジスタを備えるトランジスタ回路において、半導体層の下側に第1の絶縁層を介してボトムゲート層があり、半導体層を挟んでボトムゲート層と対向する側に第2の絶縁層を介してトップゲート層を具備した少なくとも一つの第1の薄膜トランジスタと、半導体層の下側に第1の絶縁層を介してボトムゲート層のみを具備する少なくとも一つの第2の薄膜トランジスタと、を同一基板上に形成したことを特徴とする。

(もっと読む)

半導体装置用基板の製造方法

【課題】例えばガラス基板の反りの発生を抑制し、信頼性の高い半導体装置用基板を効率的に製造する。

【解決手段】半導体装置用基板の製造方法は、第1素子基板(200a)と第2素子基板(200b)とを、第1基板(20a)における第1半導体素子(30a)が形成された面と、第2基板(20b)における第2半導体素子(30b)が形成された面とが互いに対向するように配置し、接着材(500)を介して互いに貼り合わせる貼合工程と、貼合工程の後に、第1基板における第1半導体素子が形成されていない面、及び第2基板における第2半導体素子が形成されていない面に対して薄板化処理を施す薄板化工程とを含む。更に、第1及び第2基板の各々に支持基板(11)を貼り付ける支持基板貼付工程と、第1及び第2素子基板から接着材を剥離することにより、第1及び第2素子基板を互いに分離する分離工程とを含む。

(もっと読む)

半導体装置

【課題】配線抵抗の低い半導体装置を提供すること、透過率の高い半導体装置を提供すること、または開口率の高い半導体装置を提供することを課題とする。

【解決手段】ゲート電極、半導体層、ソース電極又はドレイン電極を透光性を有する材料を用いて形成し、ゲート配線又はソース配線等の配線を透光性を有する材料より抵抗率が低い材料で設ける。また、ソース配線及び/又はゲート配線を、透光性を有する材料と当該透光性を有する材料より抵抗率が低い材料を積層させて設ける。これにより、配線抵抗が低く、透過率の高い半導体装置を提供することができる。

(もっと読む)

半導体およびその製造方法

【課題】SOI構造を有するCMOSトランジスタにおいて、CMOSトランジスタのチャネル領域に応力を印加する構造の製造方法の提供。

【解決手段】単結晶のシリコン基板11の表面に素子分離領域13Iにより画成されたnチャネルMOSトランジスタ10Aが形成された第1の素子領域13AとpチャネルMOSトランジスタ10Bが形成された第2の素子領域13Bとを含む単結晶シリコンの活性層13を形成し、シリコン基板と活性層との間に形成されたシリコン酸化膜を有し、シリコン酸化膜は第1の素子領域の下および第2の素子領域の下に連続して延在し、nチャネルMOSトランジスタのチャネル領域のシリコン酸化膜は最大の膜厚を有し、ゲート長方向に向かって膜厚を減少させ、pチャネルMOSトランジスタのチャネル領域のシリコン酸化膜は最小またはゼロの膜厚を有し、チャネル領域から、ゲート長方向に向かって膜厚を増大させることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、裏面コンタクト電極と拡散層とのコンタクト抵抗が低減して、半導体装置の動作速度の向上を図ることを可能にする。

【解決手段】基板10の表面側に形成された拡散層25P、26P、25N、26Nと、前記拡散層25P、26P、25N、26Nの表面に形成されていて前記拡散層25P、26P、25N、26Nよりも抵抗が低い低抵抗部27P、28P、27N、28Nと、前記基板10の裏面側より前記基板10を貫通して前記拡散層25P、26P、25N、26Nを通して前記低抵抗部27P、28P、27N、28Nに接続された裏面コンタクト電極63P、64P、63N、64Nを有する。

(もっと読む)

固体撮像装置とその製造方法、並びに半導体装置とその製造方法

【課題】SOI基板を用いずに半導体基板の薄膜化を可能にし、コスト低減を図った、固体撮像素子とその製造方法、並びに半導体装置とその製造方法を提供する。

【解決手段】半導体基板21に、光電変換素子と複数のMOSトランジスタとからなる画素が配列された撮像領域と、周辺回路と、半導体基板21の表面から厚み方向に半導体基板21より硬度が大きく且つ厚み方向の底面に、より硬度の大きい材料膜66を形成した柱状の終端検出部63とを有し、半導体基板が裏面からの化学機械研磨により前記終端検出部63が露出する位置まで薄膜化され、半導体基板21の表面にMOSトランジスタTr1が形成され、半導体基板21の裏面から入射光を取り込むようにして成る。

(もっと読む)

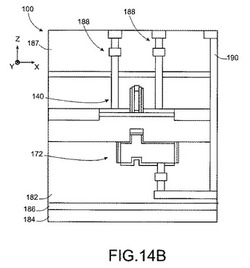

冷却機構を含む接合型半導体構造体とその形成方法

【課題】 冷却機構を有する接合型半導体基板を形成するための構造体、設計構造体、及びその形成方法を提供すること。

【解決手段】 2つの半導体基板を備える接合型基板が提供される。各々の半導体基板は、半導体デバイスを含む。少なくとも1つの基板貫通ビアが2つの半導体基板の間に設けられ、それらの間に単一の経路を提供する。2つの半導体基板の底側は、冷却機構を含む少なくとも1つの接合材料層によって接合される。1つの実施形態において、冷却機構は冷却チャネルであり、その中を通って冷却流体が流動し、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。別の実施形態において、冷却機構は、2つの端部とそれらの間の連続した経路を備えた導電性冷却フィンである。冷却フィンはヒートシンクに接続され、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。

(もっと読む)

固体撮像装置とその製造方法、並びに半導体装置とその製造方法

【課題】SOI基板を用いずに半導体基板の薄膜化を可能にし、コスト低減を図った、固体撮像素子とその製造方法、並びに半導体装置とその製造方法を提供する。

【解決手段】半導体基板21に、光電変換素子PDと複数のMOSトランジスタTr1とからなる画素が配列された撮像領域と、周辺回路と、撮像領域を挟む両外側に形成され、半導体基板の表面から厚み方向に半導体基板より硬度が大きい柱状の終端検出部63とを有し、半導体基板が裏面からの化学機械研磨により終端検出部63が露出する位置まで薄膜化され、半導体基板の表面にMOSトランジスタが形成され、半導体基板の裏面から入射光を取り込むようにして成る。

(もっと読む)

1 - 20 / 81

[ Back to top ]