Fターム[5F110DD25]の内容

Fターム[5F110DD25]に分類される特許

41 - 60 / 504

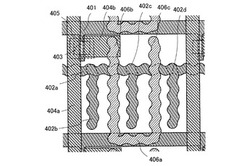

表示装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して得られた表示装置である。また配線等のパターンを所望の形状で制御性よく形成された導電膜を有する表示装置である。

【解決手段】トランジスタ上の第1の導電膜と、第2の導電膜とは、複数の屈曲点を有するコの字状に設けられる。本形状であっても、第1の導電膜と、第2の導電膜とはパターンを所望の形状で制御性よく形成される。なお、第1の導電膜と第2の導電膜は、共通電極層と、画素電極層となることができる。

(もっと読む)

酸化物半導体膜の成膜方法、半導体装置および半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタは、非晶質シリコンを用いたトランジスタと比較して信頼性が劣る場合があった。そこで、信頼性が高い酸化物半導体を用いたトランジスタを有する半導体装置を提供する。

【解決手段】酸化物半導体膜に含まれる水素、窒素および炭素などの不純物は酸化物半導体膜の半導体特性を低下させる要因となる。例えば、酸化物半導体膜に含まれる水素および窒素は、酸化物半導体膜を用いたトランジスタのしきい値電圧をマイナス方向へシフトさせてしまう要因となる。また、酸化物半導体膜に含まれる窒素、炭素および希ガスは、酸化物半導体膜中に結晶領域が生成されることを阻害する。そこで、酸化物半導体膜の不純物濃度を低減することで、高い信頼性を有するトランジスタを作製する。

(もっと読む)

半導体装置の作製方法

【課題】本発明の一態様は、酸化物半導体を用いたデバイスにおいて高い移動度を達成し

、信頼性の高い表示装置を提供する。

【解決手段】表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層を形

成し、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加熱処理を行うことによ

り、酸化物半導体層に酸素を供給し、酸化物絶縁層上に、水素を含む窒化物絶縁層を形成

し、第4の加熱処理を行うことにより、少なくとも酸化物半導体層と酸化物絶縁層の界面

に水素を供給する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と該酸化物半導体膜と接する下地となる膜との界面の電子状態が良好なトランジスタ。

【解決手段】下地となる膜は酸化物半導体膜と同様の原子配列を有し、下地となる膜と酸化物半導体膜とが接している面において、面内の下地膜の最隣接原子間距離と酸化物半導体の格子定数の差を、下地となる膜の同面内における最隣接原子間距離で除した値は0.15以下、好ましくは0.12以下、さらに好ましくは0.10以下、さらに好ましくは0.08以下とする。例えば、立方晶系の結晶構造を有し(111)面に配向する安定化ジルコニアを含む下地となる膜上に酸化物半導体膜を成膜することで、下地となる膜の直上においても結晶化度の高い結晶領域を有する酸化物半導体膜が得られる。

(もっと読む)

配線部材、および、電子素子の製造方法と、それを用いた配線部材、積層配線、電子素子、電子素子アレイ及び表示装置。

【課題】印刷法による少ない工程数のメリットを生かしつつ、より微細であり、絶縁性の低下がなく、導電部寸法精度の高い、配線部材および電子素子の製造方法を提供することを目的とする。また、配線部材、積層配線、電子素子、電子素子アレイ及び表示装置を提供することを目的とする

【解決手段】基板上にエネルギーの付与により臨界表面張力が変化する材料を含有する濡れ性変化層を形成する工程、紫外領域のレーザーを用いたレーザーアブレーション法により、濡れ性変化層に凹部を形成する工程、凹部に導電性インクを塗布して導電部を形成する工程、を含み、前記濡れ性変化層の凹部のパターン形成と同時に、前記臨界表面張力を変化させて高表面エネルギー領域のパターン形成が行われることを特徴とする配線部材の製造方法、電子素子の製造方法、及び、それにより得られた配線部材、電子素子を提供する。また、電子素子アレイ及び表示装置を提供する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタ及びその作製方法を提供する。または、該トランジスタを含む信頼性の高い半導体装置及びその作製方法を提供する。

【解決手段】チャネル形成領域と、該チャネル形成領域を挟むように設けられ、チャネル形成領域よりも低抵抗な領域であるソース領域及びドレイン領域と、を含み、チャネル形成領域、ソース領域及びドレイン領域はそれぞれ結晶性領域を含む酸化物半導体層を有する半導体装置を提供する。

(もっと読む)

液晶表示装置

【課題】非晶質半導体膜の結晶化工程において、非晶質半導体膜上に金属元素を導入して加熱処理を行なった、レーザアニールを行って得られた多結晶半導体膜を基に作製された薄膜トランジスタの電気的特性は非常に高いものとなるが、ばらつきが顕著になる場合がある。

【解決手段】非晶質半導体膜上に金属元素を導入して加熱処理を行なって連続的な結晶化領域の中に非晶質領域が点在する第1の多結晶半導体膜103bを得る。このとき、非晶質領域を所定の範囲に収めておく。そして、結晶化領域より非晶質領域にエネルギーを加えることができる波長域にあるレーザビームを第1の多結晶半導体膜103bに照射すると、結晶化領域を崩すことなく非晶質領域を結晶化させることができる。以上の結晶化工程を経て得られた第2の多結晶半導体膜を基にTFTを作製すると、その電気的特性は高く、しかもばらつきの少ないものが得られる。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板1aの活性領域1cが素子分離絶縁膜2で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極8a、ソース・ドレイン領域及び被覆応力膜を有するNTrを有し、ソース・ドレイン領域の両側部に位置する素子分離絶縁膜2aの表面は、ソース・ドレイン領域の表面より低い位置に形成されており、ゲート電極8a、活性領域1c、及び表面がソース・ドレイン領域の表面より低い位置に形成された素子分離絶縁膜2aを被覆して、チャネル形成領域に対し引張応力を印加する被覆応力膜が形成されている構成とする。

(もっと読む)

半導体装置

【課題】半導体集積回路における消費電力を低減する。また、半導体集積回路における動作の遅延を低減する。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

トリミング回路、トリミング回路の駆動方法

【課題】信頼性の高いトリミング回路を提供する。書き換え可能なトリミング回路を提供する。信頼性の高いトリミング回路の駆動方法を提供する。書き換え可能なトリミング回路の駆動方法を提供する。

【解決手段】オフリーク電流が極めて小さいトランジスタのソース電極またはドレイン電極に接続された記憶ノードと、該記憶ノードにゲート電極が接続されたトランジスタを用いてトリミング回路を構成する。また、該オフリーク電流が極めて小さいトランジスタを用いて、該記憶ノードにゲート電極が接続されたトランジスタのソース電極とドレイン電極に対して並列に接続された素子または回路のトリミング状態を制御する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜に酸素ドープ処理を行って、第1の絶

縁膜に酸素原子を供給し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに

、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半

導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された

酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳す

る領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置およびその作製方法

【課題】同一基板上に酸化物半導体を用いたオフセットトランジスタとオフセットでないトランジスタを形成する。

【解決手段】酸化物半導体層202とゲート絶縁物203とゲート配線となる第1層配線204a、第1層配線204bを形成する。その後、オフセットトランジスタをレジスト206で覆い、酸化物半導体層に不純物を導入し、N型酸化物半導体領域207を形成する。その後、第2層配線209a、第2層配線209b、第2層配線209cを形成する。以上の工程により、オフセットトランジスタとそうでないトランジスタ(アラインドトランジスタ等)を形成することができる。

(もっと読む)

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のトランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電位を保持させることで行う。メモリセルの読み出しは、ビット線にプリチャージ電位を供給した後ビット線への電位の供給を止め、ビット線の電位がプリチャージ電位に保たれるか、または電位が下がるか、により行う。

(もっと読む)

半導体装置

【課題】作製コストが低減され、かつ歩留まりが向上された半導体装置、および消費電力が低減された半導体装置を提供することである。

【解決手段】第1のトランジスタおよび第2のトランジスタと、第1のトランジスタ群および第2のトランジスタ群を具備し、第1のトランジスタ群は、第3のトランジスタ、第4のトランジスタおよび4の端子を有しており、第2のトランジスタ群は、第5乃至第8のトランジスタおよび4の端子を有しており、第1のトランジスタ、第3のトランジスタ、第6のトランジスタ、第8のトランジスタはnチャネル型トランジスタが用いられ、第2のトランジスタ、第4のトランジスタ、第5のトランジスタ、第7のトランジスタはpチャネル型トランジスタが用いられる半導体装置である。

(もっと読む)

半導体装置

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】第1のトランジスタ及び第2のトランジスタを有するメモリセルを有し、第1のトランジスタは第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタは酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される不揮発性メモリによって解決する。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板(1a,1b)の活性領域(1c,1d)が素子分離絶縁膜(2,6a)で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極(8a,8b)、ソース・ドレイン領域及び被覆応力膜を有するNTrとPTrを有し、活性領域におけるゲート長方向が<100>方向であり、素子分離絶縁膜としてNTrにおけるソース・ドレイン領域の両端部に第1の引張応力膜6aが形成され、ソース・ドレイン領域の両端部以外に第1の圧縮応力膜2が形成され、PTrの素子分離絶縁膜は第1の圧縮応力膜2が形成され、被覆応力膜としてNTrに第2の引張応力膜が形成され、PTrに第2の圧縮応力膜が形成されている構成とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

位相同期回路および位相同期回路を用いた半導体装置

【課題】スタンバイ状態からの復帰後、電圧制御発振器に入力される電圧信号が短時間で一定となる、消費電力の低減された位相同期回路を提供することを課題とする。

【解決手段】電圧制御発振器の入力端子とループフィルタを構成する容量素子の間に、酸化物半導体材料を用いて半導体層を形成したトランジスタを設け、通常動作状態の時には当該トランジスタをオン状態に、スタンバイ状態の時には当該トランジスタをオフ状態とする。

(もっと読む)

41 - 60 / 504

[ Back to top ]