Fターム[5F110DD25]の内容

Fターム[5F110DD25]に分類される特許

101 - 120 / 504

記憶回路、記憶装置、信号処理回路

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶回路の提供、消費電力の低減可能な信号処理回路を提供する。

【解決手段】記憶回路は、トランジスタと、容量素子と、第1の演算回路と、第2の演算回路と、第3の演算回路と、スイッチと、を有し、第1の演算回路の出力端子は、第2の演算回路の入力端子と電気的に接続され、第2の演算回路の入力端子は、スイッチを介して第3の演算回路の出力端子と電気的に接続され、第2の演算回路の出力端子は、第1の演算回路の入力端子と電気的に接続され、第1の演算回路の入力端子は、トランジスタのソース及びドレインの一方と電気的に接続され、トランジスタのソース及びドレインの他方は、容量素子の一対の電極のうちの一方、及び第3の演算回路の入力端子と電気的に接続され、トランジスタのチャネルは酸化物半導体層に形成される。

(もっと読む)

p型酸化物、p型酸化物製造用組成物、p型酸化物の製造方法、半導体素子、表示素子、画像表示装置、及びシステム

【課題】優れた特性、即ち、十分な導電性が得られ、比較的低温の実用的な条件で製造することができ、組成比の調整によって導電性を制御することが可能な特性を有する新規なp型酸化物などの提供。

【解決手段】組成式xAO・yCu2O(xとyはモル比率を表し、0≦x<100、かつx+y=100である。)で表されるアモルファス酸化物からなり、前記Aが、Mg、Ca、Sr、及びBaから選択される少なくともいずれかを含むp型酸化物である。

(もっと読む)

表示装置、液晶表示装置及びプロジェクター

【課題】高開口率な半導体装置を提供する。

【解決手段】絶縁表面上に第1配線と、第1配線上に第1絶縁膜と、第1絶縁膜上に半導体膜と、半導体膜上に第2絶縁膜と、第2絶縁膜上に第2配線と、第1配線と接続するゲート電極と、第2配線及びゲート電極上に第3絶縁膜と、第3絶縁膜上に半導体膜と接続する第3の配線とを有する半導体装置。

(もっと読む)

電子デバイス及びその製造方法

【課題】転写プロセスを用いずに、所期のグラフェンを制御性良く容易且つ確実に安定形成し、信頼性の高い高性能の微細な電子デバイスを実現する。

【解決手段】基板1上に絶縁層2を形成し、絶縁層2に空隙2Aを形成し、空隙2Aに触媒材料4を充填し、絶縁層2における触媒材料4の露出面4aにグラフェン5を形成し、絶縁層2上でグラフェン5の両端部に接続するように一対の電極5,6を形成し、グラフェン5を一部除去してグラフェンリボン8を形成し、グラフェンリボン8の除去された部位である間隙2A1,2A2を通じて触媒材料4を除去する。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

電気光学装置の製造方法

【課題】素子基板に絶縁膜を成膜した際にフッ素が混入しても、電界効果型トランジスターに特性異常が発生することを防止することのできる電気光学装置の製造方法を提供すること。

【解決手段】素子基板10にシリコン酸化膜からなる絶縁膜12を成膜する第1絶縁膜成膜工程の後、画素トランジスター30(電界効果型トランジスター)の半導体層1aを形成する半導体層形成工程を行う前に、絶縁膜12に水素を導入する第1絶縁膜水素導入工程を行う。また、シリコン酸化膜からなる層間絶縁膜41を形成する第2絶縁膜成膜工程の後、層間絶縁膜41に対して水素の導入を行う第2絶縁膜水素導入工程を行う。このため、絶縁膜12や層間絶縁膜41にフッ素が混入していた場合でも、かかるフッ素は、水素と結合してフッ化水素として放出される。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、酸化物半導体膜に酸素ドープ処理を行い、その後、酸化物半導体膜及び酸化物半導体膜上に設けられた酸化アルミニウム膜に対して熱処理を行うことで、化学量論的組成比を超える酸素を含む領域を有する酸化物半導体膜を形成する。該酸化物半導体膜を用いたトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジスタのしきい値電圧の変化量が低減されており、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

電界効果型トランジスタ、表示素子、画像表示装置、及びシステム

【課題】低コストで、後工程にて形成される上層の塗布性に優れ、かつ高信頼性を示す電界効果型トランジスタなどの提供。

【解決手段】絶縁性基板と、前記絶縁性基板上に形成されたゲート電極と、前記ゲート電極上に形成されたゲート絶縁層と、前記ゲート絶縁層上に形成されたソース電極及びドレイン電極と、前記ゲート絶縁層上に形成され、かつ、少なくとも前記ソース電極及び前記ドレイン電極との間に形成された酸化物半導体層と、前記酸化物半導体層を被覆するように形成された保護層とを有し、前記保護層が、フッ素樹脂を含有し、前記保護層形成後の前記保護層の水に対する接触角が、75°以上90°以下である電界効果型トランジスタである。

(もっと読む)

発光装置

【課題】駆動用トランジスタと、スイッチング用トランジスタを有する発光装置において、トランジスタのばらつきを低減する。

【解決手段】駆動用トランジスタと、スイッチング用トランジスタを有する発光装置において、駆動用トランジスタのチャネル幅をチャネル長よりも小さくする。その際、ゲート配線と平行にアノード側電源線を設けて、フルカラー表示を行う。

(もっと読む)

薄膜トランジスタ基板、表示装置、およびそれらの製造方法

【課題】本発明は、透過型液晶表示装置、ボトムエミッション型有機EL表示装置などの、TFT基板側が受光面または発光面となるフレキシブルディスプレイに用いることができるTFT基板を提供することを主目的とする。

【解決手段】本発明は、光透過性および絶縁性を有し、樹脂を含有する平坦化層と、上記平坦化層の一方の面にパターン状に形成され、フレキシブル性を有する金属層と、上記平坦化層の上記金属層側とは反対側の面に形成されたTFT素子および画素電極とを有し、上記画素電極が形成されている画素電極形成領域の少なくとも一部と、上記金属層が形成されていない金属層非形成領域の少なくとも一部とが重なるように配置されていることを特徴とするTFT基板を提供することにより、上記目的を達成する。

(もっと読む)

半導体装置の製造方法

【課題】高品質なIII族窒化物を結晶成長させ、高品質な半導体装置を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】窒化サファイア基板をアルカリエッチングし、窒化サファイア基板を清浄化する。その後、III族窒化物を結晶成長させることにより、極めて高品質なN極性結晶を得ることができる。

(もっと読む)

ホール形成方法、並びに該方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステム

【課題】プロセス再現性が高く、微細なホールを効率よく低コストで形成することができるホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムの提供。

【解決手段】基材上にピラー形成液を付与してピラーを形成するピラー形成工程と、前記ピラーが形成された基材上に絶縁膜形成材料を付与して絶縁膜を形成する絶縁膜形成工程と、前記ピラーを除去して前記絶縁膜に開口部を形成するピラー除去工程と、前記開口部が形成された絶縁膜を熱処理する熱処理工程とを含むホール形成方法である。

(もっと読む)

半導体装置

【課題】トランジスタ領域におけるゲート間距離などのレイアウトに依存することなく、半導体層のチャネル領域に有効に応力を作用させることができる半導体装置を実現する。

【解決手段】MOSトランジスタを備える半導体装置の構成として、素子分離層4で素子分離されたトランジスタ領域を有する半導体層3と、トランジスタ領域で半導体層3の第1の面上にゲート絶縁膜5を介して形成されたゲート電極6と、トランジスタ領域で半導体層3の第1の面と反対側の第2の面上に形成された応力膜31とを備え、応力膜31は、シリサイド膜を用いて形成されている。

【選択図】図13  (もっと読む)

(もっと読む)

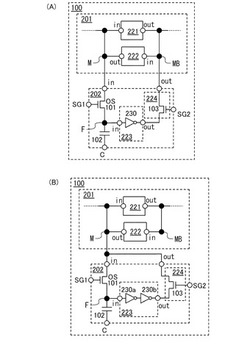

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いる半導体装置において、電気特性の良好な半導体装置を提供する。

【解決手段】基板上に酸化物半導体膜および絶縁膜を有し、酸化物半導体膜の側面は絶縁膜と接しており、酸化物半導体膜は、チャネル形成領域と、チャネル形成領域を挟んで形成されたドーパントを含む領域とを含み、酸化物半導体膜上に接して形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、サイドウォール絶縁膜を有するゲート電極と、酸化物半導体膜、および絶縁膜に接して形成されたソース電極およびドレイン電極とを有する半導体装置である。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

半導体装置及びその製造方法、並びにSOI基板及びその製造方法

【課題】コンタクトホールの形成領域が素子分離領域と重複しても、素子特性の劣化を抑制できるSOI基板とこのSOI基板を用いた半導体装置とを提供する。

【解決手段】半導体装置1は、半導体基材11と埋め込み絶縁膜12と半導体層16とを有するSOI基板と、このSOI基板上に形成された半導体素子構造とを備える。埋め込み絶縁膜12は、半導体基材11から半導体層16を電気的に絶縁分離する機能を有し、窒化膜14を有する。

(もっと読む)

記憶素子、記憶装置、信号処理回路、記憶素子の駆動方法

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶素子を提供する。消費電力の低減可能な信号処理回路を提供する。

【解決手段】クロック信号に同期してデータを保持する記憶素子において、酸化物半導体層にチャネルが形成されるトランジスタ及び容量素子を用いることより、電源電圧の供給が停止した間もデータ保持ができる。ここで、電源電圧の供給を停止する前に、クロック信号のレベルを一定に保った状態で当該トランジスタをオフ状態とすることにより、データを正確に容量素子に保持させることができる。また、このような記憶素子を、CPU、メモリ、及び周辺制御装置のそれぞれに用いることによって、CPUを用いたシステム全体で、電源電圧の供給停止を可能とし、当該システム全体の消費電力を削減することができる。

(もっと読む)

電気光学装置及び電子機器

【課題】電気光学装置において、積層構造の単純化を図り、しかも高品質な表示を可能とする。

【解決手段】電気光学装置は、基板(10)上に、互いに交差するデータ線(6)及び複数の走査線(11)と、データ線に電気的に接続された第1ソースドレイン領域、及び第2ソースドレイン領域を含んでなる半導体層(30a)と、複数の走査線のうち一の走査線に電気的に接続されたゲート電極とを有するトランジスター(30a)と、半導体層と基板との間に配置され、第2ソースドレイン領域に電気的に接続された第1容量電極(71)と、第1容量電極に対向するように設けられるとともに一の走査線に隣り合う走査線に電気的に接続された第2容量電極(73)とを有する蓄積容量(70)と、を備え、蓄積容量は、基板上に設けられた溝の内部の少なくとも一部に設けられている。

(もっと読む)

101 - 120 / 504

[ Back to top ]