半導体装置及びその製造方法、並びにSOI基板及びその製造方法

【課題】コンタクトホールの形成領域が素子分離領域と重複しても、素子特性の劣化を抑制できるSOI基板とこのSOI基板を用いた半導体装置とを提供する。

【解決手段】半導体装置1は、半導体基材11と埋め込み絶縁膜12と半導体層16とを有するSOI基板と、このSOI基板上に形成された半導体素子構造とを備える。埋め込み絶縁膜12は、半導体基材11から半導体層16を電気的に絶縁分離する機能を有し、窒化膜14を有する。

【解決手段】半導体装置1は、半導体基材11と埋め込み絶縁膜12と半導体層16とを有するSOI基板と、このSOI基板上に形成された半導体素子構造とを備える。埋め込み絶縁膜12は、半導体基材11から半導体層16を電気的に絶縁分離する機能を有し、窒化膜14を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、素子分離領域を有する半導体装置及びその製造技術に関する。

【背景技術】

【0002】

近年、モバイル機器やパーソナル音響機器などの高性能化や多機能化に伴い、このような機器に使用されるLSIの低消費電力化や高性能化が強く要求されている。バルク基板を用いて製造されたCMOSデバイスでは、プロセスの微細化に伴う高集積化や高速化により、消費電力が大きくなるという問題がある。それ故、低消費電力で動作し得る新たな素子構造を持つCMOSデバイスが待望されている。このような状況のなかで、埋め込み絶縁膜を有するSOI(Silicon On Insulator)基板を用いて製造された半導体デバイス(以下、SOIデバイスと呼ぶ。)は、LSIの低消費電力化と微細化とを実現し得るデバイスとして期待されている。SOIデバイスでは、埋め込み絶縁膜(BOX膜)の存在により、PMOSトランジスタやNMOSトランジスタなどの素子同士を電気的に完全に分離することができるので、ラッチアップ(Latch up)が生じず、高密度なレイアウトが可能になるという利点がある。

【0003】

SOIデバイスは、一般に、部分空乏型SOI(PD−SOI:Partially−Depleted SOI)デバイスと完全空乏型SOI(FD−SOI:Fully Depleted SOI)デバイスとに分類される。いずれのSOIデバイスも、ゲート電極の直下に、ゲート絶縁膜とソース拡散領域とドレイン拡散領域と埋め込み絶縁膜とで囲まれたボディ領域を有している。PD−SOIは、ボディ領域が部分的に空乏化された構造であるが、このPD−SOIには、基板浮遊効果(floating body effect)により、たとえば、デバイス動作時のサブスレショルド特性(Sファクタ)が悪化するという問題がある。一方、FD−SOIでは、ボディ領域が完全に空乏化されているので、基板浮遊効果が生じない。このため、低電圧且つ低消費電流での動作が得られやすいという利点がある。

【0004】

また、素子分離構造は、一般に、LOCOS(Local Oxidation Of Silicon)やSTI(Shallow Trench Isolation)を用いて形成される。LOCOSは、半導体基板の表面を選択的に酸化して素子分離用の絶縁膜を形成する方法であり、STIは、半導体基板に浅い溝を形成しこの溝に絶縁膜を埋め込む方法である。

【0005】

上記SOIデバイスや素子分離技術に関する先行技術文献としては、たとえば、特開2003−289144号公報(特許文献1)や特開平06−140427号公報(特許文献2)が挙げられる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2003−289144号公報

【特許文献2】特開平06−140427号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上記LOCOSやSTIといった素子分離法のほかに、半導体基板の表面を選択的にエッチングしてメサ形状の半導体層を形成しこれを活性領域(素子領域)として利用する素子分離法(以下、メサ分離法と呼ぶ。)を使用することもできる。このメサ形状の半導体層上にゲート構造(ゲート絶縁膜及びゲート電極)を形成し、ゲート構造の両側の当該半導体層に不純物を導入してソース/ドレイン拡散領域を形成することでトランジスタ構造を作製することが可能である。ソース/ドレイン拡散領域は、コンタクトプラグを介して上層配線と電気的に接続される。このコンタクトプラグは、たとえば、ソース/ドレイン拡散領域を被覆する層間絶縁膜を選択的にエッチングしてコンタクトホールを形成し、このコンタクトホールにタングステンなどの導電性材料を埋め込むことにより形成することができる。

【0008】

SOI基板にメサ分離法を適用してトランジスタ構造を作製する場合には、後に詳述するように、メサ形状の半導体層を形成する工程で、素子分離領域においてSOI基板内部の埋め込み絶縁膜の上面が露出するまでエッチングが行われる。メサ形状の半導体層を用いてトランジスタ構造が作製された後は、層間絶縁膜を全面に亘って堆積する工程と、この層間絶縁膜を選択的にエッチングしてソース/ドレイン拡散領域に達するコンタクトホールを形成する工程とが実行されるが、そのコンタクトホールの位置ズレによりコンタクホールの形成領域が素子分離領域で露出する埋め込み絶縁膜と重複(オーバーラップ)することがある。この場合、コンタクトホールの形成の際に層間絶縁膜とともに当該埋め込み絶縁膜が過剰にエッチングされることで素子特性が劣化するおそれがある。

【0009】

また、LOCOSやSTIを用いて形成された素子分離領域を有するトランジスタ構造においても、コンタクトホールの位置ズレによりコンタクトホールの形成領域が素子分離用絶縁膜と重複する場合がある。この場合にも、コンタクトホールの形成の際に、層間絶縁膜とともに素子分離用絶縁膜が過剰にエッチングされることで素子特性が劣化するおそれがある。

【0010】

上記に鑑みて本発明の目的は、基板上の層間絶縁膜に形成されたコンタクトホールの位置ズレが生じてコンタクトホールの形成領域が素子分離領域と重複しても、素子特性の劣化を抑制することができるSOI基板及びその製造方法、並びに半導体装置及びその製造方法を提供することである。

【課題を解決するための手段】

【0011】

本発明の第1の態様によるSOI基板は、半導体基材と、半導体層と、前記半導体基材と前記半導体層とに挟み込まれ、前記半導体基材から前記半導体層を電気的に絶縁分離する埋め込み絶縁膜とを備え、前記埋め込み絶縁膜は、窒化膜を含むことを特徴とする。

【0012】

本発明の第2の態様による半導体装置は、前記SOI基板と、前記SOI基板上に形成された半導体素子構造とを備えることを特徴とする。

【0013】

本発明の第3の態様による半導体装置の製造方法は、前記SOI基板を用意する工程と、前記SOI基板上に半導体素子構造を形成する工程とを備えることを特徴とする。

【0014】

本発明の第4の態様によるSOI基板の製造方法は、半導体層を含む第1の半導体基材を用意する工程と、第2の半導体基材の主面上に窒化膜を含む絶縁膜を形成する工程と、前記第2の半導体基材上の当該絶縁膜と前記第1の半導体基材の当該半導体層とを貼り合わせる工程とを備え、前記絶縁膜は、前記半導体層を前記第2の半導体基材から電気的に絶縁分離するように形成されることを特徴とする。

【発明の効果】

【0015】

本発明によれば、層間絶縁膜に形成されたコンタクトホールの位置ズレにより素子分離領域でSOI基板がエッチングされても、窒化膜がエッチングストッパとして機能するので、素子特性の劣化を抑制することができる。

【図面の簡単な説明】

【0016】

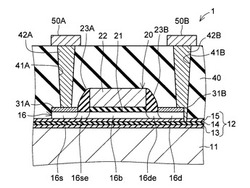

【図1】本発明に係る実施の形態の半導体装置の構造を概略的に示す断面図である。

【図2】本実施の形態の半導体装置の製造工程(第1工程)を概略的に示す断面図である。

【図3】本実施の形態の半導体装置の製造工程(第2工程)を概略的に示す断面図である。

【図4】本実施の形態の半導体装置の製造工程(第3工程)を概略的に示す断面図である。

【図5】本実施の形態の半導体装置の製造工程(第4工程)を概略的に示す断面図である。

【図6】本実施の形態の半導体装置の製造工程(第5工程)を概略的に示す断面図である。

【図7】本実施の形態の半導体装置の製造工程(第6工程)を概略的に示す断面図である。

【図8】本実施の形態の半導体装置の製造工程(第7工程)を概略的に示す断面図である。

【図9】本実施の形態の半導体装置の製造工程(第8工程)を概略的に示す断面図である。

【図10】本実施の形態の半導体装置の製造工程(第9工程)を概略的に示す断面図である。

【図11】本実施の形態の半導体装置の製造工程(第10工程)を概略的に示す断面図である。

【図12】本実施の形態のSOI基板の製造工程の一部を概略的に示す断面図である。

【図13】本実施の形態のSOI基板の製造工程の一部を概略的に示す断面図である。

【図14】本実施の形態のSOI基板の製造工程の一部を概略的に示す断面図である。

【図15】比較例の半導体装置の構造を概略的に示す断面図である。

【図16】本発明に係る他の実施の形態の半導体装置の構造を概略的に示す断面図である。

【発明を実施するための形態】

【0017】

以下、本発明に係る実施の形態について図面を参照しつつ説明する。

【0018】

図1は、本発明に係る実施の形態の半導体装置(SOIトランジスタ)1の構造を概略的に示す断面図である。この半導体装置1は、半導体基材(支持基板)11と、この半導体基材11上に配置された埋め込み絶縁膜12と、この埋め込み絶縁膜12上に配置された半導体層(SOI層)16とを備えている。半導体層16はメサ形状に加工された凸部であり、SOIトランジスタ1のゲート構造20は、この半導体層16上に形成されている。本実施の形態のSOIトランジスタ1は、このメサ形状の半導体層16を活性領域(素子領域)として利用し、半導体層16のメサ形状は、活性領域以外の素子分離領域を画定するものである。

【0019】

埋め込み絶縁膜12は、おもて面側の半導体層16を裏面側の半導体基材11から電気的に絶縁分離する機能を有し、図1に示されるように下部絶縁膜13、エッチングバリア膜14及び上部絶縁膜15を含む。下部絶縁膜13と上部絶縁膜15とは、たとえばシリコン酸化膜で構成され、エッチングバリア膜14は、上部絶縁膜15よりも緻密な絶縁材料(たとえば、窒化膜)で構成される。後述するように、このエッチングバリア膜14は、層間絶縁膜40にコンタクトホール41A,41Bを異方性エッチングにより形成する際のエッチングストッパとして機能する。

【0020】

ゲート構造20は、半導体層16上に成膜されたゲート絶縁膜21と、このゲート絶縁膜21上に形成されたゲート電極22と、ゲート電極22の両側壁に形成された一対のサイドウォールスペーサ23A,23Bとで構成されている。ゲート絶縁膜21は、1nm(ナノメートル)〜数十nm程度の範囲の膜厚を有することができる。ゲート絶縁膜21の構成材料としては、たとえば、シリコン酸化物、シリコン窒化物、あるいは、シリコン酸化物よりも誘電率が高い高誘電率材料(たとえば、窒素添加のハフニウムシリケートなどの酸化ハフニウム系材料)を使用することができる。また、ゲート電極22は、50nm〜500nm程度の範囲の膜厚を有し、不純物が高濃度でドープされた多結晶シリコンや、チタンなどの高融点金属材料を用いて形成されればよい。

【0021】

半導体層16は、数nm〜数百nm程度の厚みを有し、たとえば、単結晶シリコン材料で構成されている。半導体層16には、p型またはn型の導電型を有するソース拡散領域16s及びドレイン拡散領域16dと、これらソース拡散領域16s及びドレイン拡散領域16dに挟まれるボディ領域16bとが形成されている。また、ソース拡散領域16sからドレイン拡散領域16dの方向に突出するLDD(Lightly Doped Drain)領域またはエクステンション領域16seが形成され、ドレイン拡散領域16dからソース拡散領域16sの方向に突出するLDD領域またはエクステンション領域16deが形成されている。本実施の形態のボディ領域16bは、ほぼ完全に空乏化された領域である。

【0022】

また、ゲート構造20のゲート長方向両側には、半導体層16を下地とするエピタキシャル層31A,31Bが形成されている。これらエピタキシャル層31A,31Bは、主に寄生抵抗を低減させる目的で形成されたものである。

【0023】

そして、ゲート構造20と半導体層16と素子分離領域(メサ形状の半導体層16が形成されない領域)とを被覆するように層間絶縁膜40が形成されている。層間絶縁膜40は、たとえば、500nm〜1500nmの範囲内の膜厚を有し、SiO2、SiOC、SiCあるいはSiCNといった絶縁材料で構成されればよい。この層間絶縁膜40には、エピタキシャル層31A,31Bの上面にそれぞれ達するコンタクトホール41A,41Bが形成されており、これらコンタクトホール41A,41Bには、それぞれ、タングステンやタンタルなどの高融点金属材料からなるコンタクトプラグ42A,42Bが埋め込まれている。これらコンタクトホール41A,41Bの下端部は、エピタキシャル層31A,31Bを介してソース拡散領域16s及びドレイン拡散領域16dにそれぞれ電気的に接続されており、コンタクトホール41A,41Bの上端部はそれぞれ上層配線50A,50Bと電気的に接続されている。

【0024】

本実施の形態の半導体装置1では、フォトリソグラフィや紫外線リソグラフィといった半導体リソグラフィでのレチクルの位置ズレにより、コンタクトホール41Bの形成領域が正確な位置からずれて素子分離領域と重複している。このため、コンタクトホール41A,41Bをエッチングで形成する際に、上部絶縁膜15に達する深さまでSOI基板10がエッチングされているが、エッチングバリア膜14の存在により、コンタクトホール41Bが埋め込み絶縁膜12を貫通することが防止される。

【0025】

次に、図2〜図11を参照しつつ本実施の形態の半導体装置1の製造方法の一例を以下に説明する。図2〜図11は、本実施の形態の半導体装置1の製造工程を概略的に示す断面図である。

【0026】

まず、図2に示すように、半導体基材11と埋め込み絶縁膜12と半導体層16Pとが積層されたSOI基板10を用意する。半導体基材11と半導体層16Pとは、シリコン単結晶材料からなる。このSOI基板10の製造方法については後述する。次に、半導体層16Pをメサ形状にエッチング加工するために、フォトリソグラフィやEUV(Extreme Ultra Violet)リソグラフィなどの半導体リソグラフィにより半導体層16P上にレジストパターン19を形成する(図3)。そして、このレジストパターン19をマスクとする異方性エッチングを実行して半導体層16Pを加工する。この結果、図4に示されるように、活性領域をなすメサ形状の凸部を有する半導体層16が形成される。

【0027】

その後、たとえばCVD(Chemical Vapor Deposition)法により、図5に示されるように、図4の構造上に、ハフニウムシリケートなどの高誘電率材料からなる数nm程度の厚みの絶縁膜21Pと、100nm程度の厚みの導電層22Pとを順次成膜する。導電層22Pは、多結晶シリコンや窒化チタンを用いて形成されればよい。次いで、半導体リソグラフィにより図5の構造上にレジストパターン(図示せず)を形成し、このレジストパターンをマスクとするエッチングを実行して図6のゲート絶縁膜21とゲート電極22とを形成する。そして、これらゲート絶縁膜21とゲート電極22とをマスクとして、ゲート電極22の両側の半導体層16内部に不純物60をイオン注入し活性化することで、LDD領域またはエクステンション領域用の不純物拡散領域16se,16deを形成する。

【0028】

その後、たとえばCVD法により、図7の構造上に、シリコン酸化物などの絶縁材料からなる10nm〜300nm程度の厚みの絶縁膜(図示せず)を堆積し、この絶縁膜を異方性エッチングによりエッチバックする。この結果、図8に示されるように、ゲート電極22の両側壁にサイドウォールスペーサ23A,23Bが形成される。これらサイドウォールスペーサ23A,23Bとゲート絶縁膜21とゲート電極22とでゲート構造20が構成される。

【0029】

次に、選択エピタキシャル成長(SEG:Selective Epitaxial Growth)法により、図9に示されるように、半導体層16の露出面を下地とするエピタキシャル層31A,31Bを成膜する。選択エピタキシャル成長法としては、シラン系ガス(たとえば、シランガス、ジシランガスあるいはジクロロシランガス)と塩素系ガスとを含む原料ガスを用いたCVD法が挙げられる。次に、ゲート構造20をマスクとして、エピタキシャル層31A,31Bを介して半導体層16内部に不純物をイオン注入し活性化することにより、ゲート構造20の両側にソース拡散領域16sとドレイン拡散領域16dとが形成される。なお、ソース拡散領域16sとドレイン拡散領域16dとが互いに入れ替わってもよい。

【0030】

次に、たとえばプラズマCVD法により、図9の構造上に、SiO2系材料からなる500nm〜1500nm程度の厚みの層間絶縁膜40を形成する。この層間絶縁膜40の上面は、必要に応じて、たとえばCMP(Chemical Mechanical Polish)を用いて平坦化される。次いで、フォトリソグラフィやEUVリソグラフィなどの半導体リソグラフィにより層間絶縁膜40上にレジストパターン(図示せず)を形成し、このレジストパターンをマスクとする異方性エッチングを実行して層間絶縁膜40をパターニングする。この結果、図11に示されるように、エピタキシャル層31A,31Bを介してソース拡散領域16s及びドレイン拡散領域16dと電気的に接続されたコンタクトホール41A,41Bが形成される。

【0031】

たとえばCVD法により、コンタクトホール41A,41Bの内壁に窒化膜などのバリア膜を形成し、さらに、コンタクトホール41A,41B内部にタングステンなどの高融点材料を埋め込むことで、図1のコンタクトプラグ42A,42Bが形成される。その後は、銅やアルミニウムなどの配線材料からなる上層配線50A,50Bが形成される。

【0032】

本実施の形態の半導体装置1では、図3及び図4に示したように、メサ形状の半導体層16を形成する際に、SOI基板10内部の埋め込み絶縁膜12の上面が露出するまでエッチングが行われる。また、図11に示したように、半導体リソグラフィで使用されたレチクルの位置ズレにより、コンタクトホール41Bの形成領域が素子分離領域と重複(オーバラップ)している。それ故、層間絶縁膜40だけでなく上部絶縁膜15がエッチングされているが、エッチングバリア膜14がエッチングストッパとして機能するので、コンタクトホール41Bが埋め込み絶縁膜12を貫通することが確実に防止される。したがって、半導体基材11と半導体層(SOI層)16との間でショート(電気的短絡)が発生することが確実に防止されるので、歩留まりの向上が可能となる。

【0033】

たとえば、シリコン窒化膜からなるエッチングバリア膜14の膜厚が数nm〜50nm程度(好ましくは5nm〜10nm程度)の範囲内のとき、エッチングバリア膜14のエッチングレート(=R1)に対する上部絶縁膜15のエッチングレート(=R2)の比率(=R2/R1)すなわち選択比を5〜40程度、より好ましくは10〜20程度にすれば、コンタクトホール41Bがエッチングバリア膜14を貫通することを防止することができる。実際の実験において、基板温度を50℃とし、C4F8ガス(流量:26sccm)とArガス(流量:500sccm)とO2ガス(流量:10sccm)とを含むエッチングガスを用いて層間絶縁膜(シリコン酸化膜)40に対する異方性エッチングを実行したとき、コンタクトホール41Bがエッチングバリア膜14を貫通することが防止された。

【0034】

また、埋め込み絶縁膜12の膜厚が十分に薄いとき、半導体基材11をバックゲートとして利用することができる。具体的には、半導体基材(支持基板)11へのバイアス電圧の印加により、SOIトランジスタ1のしきい値電流の制御や、素子特性の劣化またはバラツキの改善が可能となる。たとえば、上部絶縁膜15と下部絶縁膜13とが誘電率3.9のシリコン酸化膜であり、エッチングバリア膜14が誘電率7.5のシリコン窒化膜である場合、シリコン酸化膜の誘電率に比べてシリコン窒化膜の誘電率は約2倍であるため、エッチングバリア膜14の厚みを、上部絶縁膜15と下部絶縁膜13との合計厚みの倍程度の厚みにしても、バックゲート効果を得ることができると考えられる。このような観点から、バックゲート効果を得るために、埋め込み絶縁膜12の全体の膜厚の上限を、たとえば10nm〜20nm程度にすることが望ましい。

【0035】

なお、エッチングバリア膜14の構成材料としてシリコン窒化物に代用する材料を用いてもよい。この場合、エッチングバリア膜14の厚みを、その材質の誘電率のシリコン酸化膜の誘電率に対する比率に相当する膜厚にすることが可能である。

【0036】

次に、図12〜図14を参照しつつ、本実施の形態の半導体装置1の製造に使用されるSOI基板10の製造方法を説明する。図12〜図14は、SOI基板10の製造工程を概略的に示す断面図である。

【0037】

まず、図12(A)に示されるように、単結晶シリコンウエハである半導体基材11の主面を熱酸化して下部絶縁膜(熱酸化膜)13を形成する。次いで、たとえばCVD法により、この下部絶縁膜13上に窒化膜からなるエッチングバリア膜14を成膜する。他方、図12(B)に示されるように、単結晶シリコン材料からなる他の半導体基材17の主面を熱酸化して上部絶縁膜(熱酸化膜)15を形成する。そして、上部絶縁膜15を介して半導体基材17に水素イオン18を打ち込むことにより、一定の深さ(たとえば、表面から0.1μm〜数μmの深さ)に分布する欠陥層17dを形成する。

【0038】

次に、図13に示されるように、半導体基材11上のエッチングバリア膜14と半導体基材17上の上部絶縁膜15とを貼り合わせる。そして、熱処理により、欠陥層17dを境にして半導体基材11から半導体層16Pを剥離することにより、図14のSOI基板10が作製される。半導体層16Pの表面は、必要に応じて研磨される。

【0039】

なお、図14のSOI基板10では、エッチングバリア膜14が下部絶縁膜13と上部絶縁膜15とで挟み込まれている。その理由は、窒化膜とシリコンとの界面準位が素子特性に影響を与えることを抑制するためである。窒化膜とシリコンとの界面準位が素子特性にほとんど影響を与えない場合には、下部絶縁膜13,15の一方または双方を形成しなくてもよい。

【0040】

以上に説明したように実施の形態の半導体装置1は、埋め込み絶縁膜12に窒化膜を有するSOI基板10を使用して作製されるので、コンタクトホール41Bの形成領域が素子分離領域と重複する場合でも、コンタクトホール41Bが埋め込み絶縁膜12を貫通することが防止される。図15は、比較例の半導体装置100の構造を概略的に示す断面図である。図15の構造は、埋め込み絶縁膜12Pがシリコン酸化膜のみからなる点を除いて、実施の形態の半導体装置1の構造と同じである。図15に示されるように、半導体装置100はエッチングバリア膜を有していないので、コンタクトホール41Bが埋め込み絶縁膜12Pを貫通し、半導体基材11の上部領域PAまで到達している。このため、半導体基材11と半導体層16とがショートして不良品が発生するという問題がある。

【0041】

本実施の形態の半導体装置1では、バックゲート効果の実現のために極薄の埋め込み絶縁膜12を有するSOI基板10を使用する場合でも、コンタクトホール41Bが埋め込み絶縁膜12を貫通することを防止することができる。したがって、半導体基材11と半導体層16との間のショート不良を防止することができ、歩留まり向上を実現することができる。

【0042】

以上、図面を参照して本発明の実施の形態について述べたが、これは本発明の例示であり、上記以外の様々な形態を採用することもできる。たとえば、上記実施の形態は、メサ分離法に基づいたSOIトランジスタ構造を有しているが、メサ分離法に代えて、STIやLOCOSを用いて形成された素子分離用絶縁膜を有するSOIトランジスタ構造でも、上記実施の形態の場合と同様に、コンタクトホールがSOI基板内部の埋め込み絶縁膜を貫通することが防止される。

【0043】

図16は、素子分離領域を形成するSTI構造33,34を有する半導体装置2の構造の一例を概略的に示す断面図である。この半導体装置2では、STI構造33,36が、半導体層16Pの表面から埋め込み絶縁膜12に至るまで深さ方向に延在している。一方のSTI構造33は、溝(トレンチ)34と、この溝34内に埋め込まれたSiO2系材料からなる素子分離用絶縁膜35を有しており、他方のSTI構造36も、溝(トレンチ)37と、この溝37内に埋め込まれたSiO2系材料からなる素子分離用絶縁膜38とを有している。

【0044】

STI構造34,37の製造方法は、特に限定されるものではなく、公知の方法を使用してSTI構造34,37を形成すればよい。たとえば、図2のSOI基板10上にシリコン酸化膜とシリコン窒化膜とを順次成膜し、次に、フォトリソグラフィ技術とエッチング技術とにより、これらシリコン酸化膜とシリコン窒化膜とSOI基板10とを選択的にエッチングして素子分離用の溝34,37を形成する。そして、これら溝34,37の内壁を熱酸化する。その後、CVD法により、これら溝34,37の内部にシリコン酸化物などの絶縁膜を堆積させる。さらに、化学機械研磨(CMP:Chemical Mechanical Polishing)法あるいは化学機械平坦化(CMP:Chemical Mechanical Planarization)法により、当該絶縁膜の上面を平坦化する。その後、シリコン酸化膜とシリコン窒化膜とは個別にウェットエッチングにより除去される。以上のプロセスの結果として、図16に示されるようなSTI構造34,37を作製することができる。

【0045】

上記STI構造33,36間の領域には、半導体層16P上に、ゲート絶縁膜71、ゲート電極72及びサイドウォールスペーサ73A,73Bからなるゲート構造70が形成される。ゲート構造70の両側には、ソース拡散領域160sとドレイン拡散領域160dとが形成されている。また、これらソース拡散領域160sとドレイン拡散領域160dとからそれぞれゲート電極72の直下の領域に突出するエクステンション領域160se,160deが形成されている。ボディ領域160bは、ソース拡散領域160sとドレイン拡散領域160dとエクステンション領域160se,160deと埋め込み絶縁膜12とで囲まれている領域である。

【0046】

また、半導体装置2では、上記ゲート構造70と半導体層16PとSTI構造33,36とを被覆するようにSiO2系材料からなる層間絶縁膜80が形成されている。この層間絶縁膜80には、ソース拡散領域160sの上面とドレイン拡散領域160dの上面とにそれぞれ達するコンタクトホール81A,81Bが形成されており、これらコンタクトホール81A,81Bには、それぞれ、タングステンやタンタルなどの高融点金属材料からなるコンタクトプラグ82A,82Bが埋め込まれている。コンタクトホール81A,81Bの上端部はそれぞれ上層配線90A,90Bと電気的に接続されている。

【0047】

図16に示されるように、半導体リソグラフィでのレチクルの位置ズレにより、コンタクトホール81Bの形成領域がSTI構造36と重複している。このため、コンタクトホール81A,81Bをエッチングで形成する際に、エッチングバリア膜14に達する深さまで素子分離用絶縁膜38がエッチングされているが、エッチングバリア膜14の存在により、コンタクトホール81Bが埋め込み絶縁膜12を貫通することが防止されている。

【0048】

上記実施の形態の半導体装置1や変形例の半導体装置2は、SOI基板上にゲート構造20,70が形成されたものであるが、本発明はこれらに限定されるものではない。ゲート構造20,70以外の半導体素子構造がSOI基板10上に形成される構造において、コンタクトホールの形成領域が素子分離領域と重複しても、このコンタクトホールが埋め込み絶縁膜12を貫通することを防止することができる。

【符号の説明】

【0049】

1,2,100 半導体装置、 10 SOI(Silicon On Insulator)基板、 11 半導体基材(支持基板)、 12 埋め込み絶縁膜、 13 下部絶縁膜、 14 エッチングバリア膜、 15 上部絶縁膜、 16 半導体層(SOI層)、 16b ボディ領域、 16s ソース拡散領域、 16d ドレイン拡散領域、 16se,16de エクステンション領域、 17d 欠陥層、 18 水素イオン、 20 ゲート構造、 21 ゲート絶縁膜、 22 ゲート電極、 23A,23B サイドウォールスペーサ、 33,36 素子分離構造(STI構造)、 35,38 素子分離用絶縁膜、 31A,31B エピタキシャル層、 40 層間絶縁膜、 41A,41B コンタクトホール、 42A,42B コンタクトプラグ、 50A,50B 上層配線、 70 ゲート構造、 71 ゲート絶縁膜、 72 ゲート電極、 73A,73B サイドウォールスペーサ、 80 層間絶縁膜、 81A,81B コンタクトホール、 82A,82B コンタクトプラグ、 90A,90B 上層配線。

【技術分野】

【0001】

本発明は、素子分離領域を有する半導体装置及びその製造技術に関する。

【背景技術】

【0002】

近年、モバイル機器やパーソナル音響機器などの高性能化や多機能化に伴い、このような機器に使用されるLSIの低消費電力化や高性能化が強く要求されている。バルク基板を用いて製造されたCMOSデバイスでは、プロセスの微細化に伴う高集積化や高速化により、消費電力が大きくなるという問題がある。それ故、低消費電力で動作し得る新たな素子構造を持つCMOSデバイスが待望されている。このような状況のなかで、埋め込み絶縁膜を有するSOI(Silicon On Insulator)基板を用いて製造された半導体デバイス(以下、SOIデバイスと呼ぶ。)は、LSIの低消費電力化と微細化とを実現し得るデバイスとして期待されている。SOIデバイスでは、埋め込み絶縁膜(BOX膜)の存在により、PMOSトランジスタやNMOSトランジスタなどの素子同士を電気的に完全に分離することができるので、ラッチアップ(Latch up)が生じず、高密度なレイアウトが可能になるという利点がある。

【0003】

SOIデバイスは、一般に、部分空乏型SOI(PD−SOI:Partially−Depleted SOI)デバイスと完全空乏型SOI(FD−SOI:Fully Depleted SOI)デバイスとに分類される。いずれのSOIデバイスも、ゲート電極の直下に、ゲート絶縁膜とソース拡散領域とドレイン拡散領域と埋め込み絶縁膜とで囲まれたボディ領域を有している。PD−SOIは、ボディ領域が部分的に空乏化された構造であるが、このPD−SOIには、基板浮遊効果(floating body effect)により、たとえば、デバイス動作時のサブスレショルド特性(Sファクタ)が悪化するという問題がある。一方、FD−SOIでは、ボディ領域が完全に空乏化されているので、基板浮遊効果が生じない。このため、低電圧且つ低消費電流での動作が得られやすいという利点がある。

【0004】

また、素子分離構造は、一般に、LOCOS(Local Oxidation Of Silicon)やSTI(Shallow Trench Isolation)を用いて形成される。LOCOSは、半導体基板の表面を選択的に酸化して素子分離用の絶縁膜を形成する方法であり、STIは、半導体基板に浅い溝を形成しこの溝に絶縁膜を埋め込む方法である。

【0005】

上記SOIデバイスや素子分離技術に関する先行技術文献としては、たとえば、特開2003−289144号公報(特許文献1)や特開平06−140427号公報(特許文献2)が挙げられる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2003−289144号公報

【特許文献2】特開平06−140427号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上記LOCOSやSTIといった素子分離法のほかに、半導体基板の表面を選択的にエッチングしてメサ形状の半導体層を形成しこれを活性領域(素子領域)として利用する素子分離法(以下、メサ分離法と呼ぶ。)を使用することもできる。このメサ形状の半導体層上にゲート構造(ゲート絶縁膜及びゲート電極)を形成し、ゲート構造の両側の当該半導体層に不純物を導入してソース/ドレイン拡散領域を形成することでトランジスタ構造を作製することが可能である。ソース/ドレイン拡散領域は、コンタクトプラグを介して上層配線と電気的に接続される。このコンタクトプラグは、たとえば、ソース/ドレイン拡散領域を被覆する層間絶縁膜を選択的にエッチングしてコンタクトホールを形成し、このコンタクトホールにタングステンなどの導電性材料を埋め込むことにより形成することができる。

【0008】

SOI基板にメサ分離法を適用してトランジスタ構造を作製する場合には、後に詳述するように、メサ形状の半導体層を形成する工程で、素子分離領域においてSOI基板内部の埋め込み絶縁膜の上面が露出するまでエッチングが行われる。メサ形状の半導体層を用いてトランジスタ構造が作製された後は、層間絶縁膜を全面に亘って堆積する工程と、この層間絶縁膜を選択的にエッチングしてソース/ドレイン拡散領域に達するコンタクトホールを形成する工程とが実行されるが、そのコンタクトホールの位置ズレによりコンタクホールの形成領域が素子分離領域で露出する埋め込み絶縁膜と重複(オーバーラップ)することがある。この場合、コンタクトホールの形成の際に層間絶縁膜とともに当該埋め込み絶縁膜が過剰にエッチングされることで素子特性が劣化するおそれがある。

【0009】

また、LOCOSやSTIを用いて形成された素子分離領域を有するトランジスタ構造においても、コンタクトホールの位置ズレによりコンタクトホールの形成領域が素子分離用絶縁膜と重複する場合がある。この場合にも、コンタクトホールの形成の際に、層間絶縁膜とともに素子分離用絶縁膜が過剰にエッチングされることで素子特性が劣化するおそれがある。

【0010】

上記に鑑みて本発明の目的は、基板上の層間絶縁膜に形成されたコンタクトホールの位置ズレが生じてコンタクトホールの形成領域が素子分離領域と重複しても、素子特性の劣化を抑制することができるSOI基板及びその製造方法、並びに半導体装置及びその製造方法を提供することである。

【課題を解決するための手段】

【0011】

本発明の第1の態様によるSOI基板は、半導体基材と、半導体層と、前記半導体基材と前記半導体層とに挟み込まれ、前記半導体基材から前記半導体層を電気的に絶縁分離する埋め込み絶縁膜とを備え、前記埋め込み絶縁膜は、窒化膜を含むことを特徴とする。

【0012】

本発明の第2の態様による半導体装置は、前記SOI基板と、前記SOI基板上に形成された半導体素子構造とを備えることを特徴とする。

【0013】

本発明の第3の態様による半導体装置の製造方法は、前記SOI基板を用意する工程と、前記SOI基板上に半導体素子構造を形成する工程とを備えることを特徴とする。

【0014】

本発明の第4の態様によるSOI基板の製造方法は、半導体層を含む第1の半導体基材を用意する工程と、第2の半導体基材の主面上に窒化膜を含む絶縁膜を形成する工程と、前記第2の半導体基材上の当該絶縁膜と前記第1の半導体基材の当該半導体層とを貼り合わせる工程とを備え、前記絶縁膜は、前記半導体層を前記第2の半導体基材から電気的に絶縁分離するように形成されることを特徴とする。

【発明の効果】

【0015】

本発明によれば、層間絶縁膜に形成されたコンタクトホールの位置ズレにより素子分離領域でSOI基板がエッチングされても、窒化膜がエッチングストッパとして機能するので、素子特性の劣化を抑制することができる。

【図面の簡単な説明】

【0016】

【図1】本発明に係る実施の形態の半導体装置の構造を概略的に示す断面図である。

【図2】本実施の形態の半導体装置の製造工程(第1工程)を概略的に示す断面図である。

【図3】本実施の形態の半導体装置の製造工程(第2工程)を概略的に示す断面図である。

【図4】本実施の形態の半導体装置の製造工程(第3工程)を概略的に示す断面図である。

【図5】本実施の形態の半導体装置の製造工程(第4工程)を概略的に示す断面図である。

【図6】本実施の形態の半導体装置の製造工程(第5工程)を概略的に示す断面図である。

【図7】本実施の形態の半導体装置の製造工程(第6工程)を概略的に示す断面図である。

【図8】本実施の形態の半導体装置の製造工程(第7工程)を概略的に示す断面図である。

【図9】本実施の形態の半導体装置の製造工程(第8工程)を概略的に示す断面図である。

【図10】本実施の形態の半導体装置の製造工程(第9工程)を概略的に示す断面図である。

【図11】本実施の形態の半導体装置の製造工程(第10工程)を概略的に示す断面図である。

【図12】本実施の形態のSOI基板の製造工程の一部を概略的に示す断面図である。

【図13】本実施の形態のSOI基板の製造工程の一部を概略的に示す断面図である。

【図14】本実施の形態のSOI基板の製造工程の一部を概略的に示す断面図である。

【図15】比較例の半導体装置の構造を概略的に示す断面図である。

【図16】本発明に係る他の実施の形態の半導体装置の構造を概略的に示す断面図である。

【発明を実施するための形態】

【0017】

以下、本発明に係る実施の形態について図面を参照しつつ説明する。

【0018】

図1は、本発明に係る実施の形態の半導体装置(SOIトランジスタ)1の構造を概略的に示す断面図である。この半導体装置1は、半導体基材(支持基板)11と、この半導体基材11上に配置された埋め込み絶縁膜12と、この埋め込み絶縁膜12上に配置された半導体層(SOI層)16とを備えている。半導体層16はメサ形状に加工された凸部であり、SOIトランジスタ1のゲート構造20は、この半導体層16上に形成されている。本実施の形態のSOIトランジスタ1は、このメサ形状の半導体層16を活性領域(素子領域)として利用し、半導体層16のメサ形状は、活性領域以外の素子分離領域を画定するものである。

【0019】

埋め込み絶縁膜12は、おもて面側の半導体層16を裏面側の半導体基材11から電気的に絶縁分離する機能を有し、図1に示されるように下部絶縁膜13、エッチングバリア膜14及び上部絶縁膜15を含む。下部絶縁膜13と上部絶縁膜15とは、たとえばシリコン酸化膜で構成され、エッチングバリア膜14は、上部絶縁膜15よりも緻密な絶縁材料(たとえば、窒化膜)で構成される。後述するように、このエッチングバリア膜14は、層間絶縁膜40にコンタクトホール41A,41Bを異方性エッチングにより形成する際のエッチングストッパとして機能する。

【0020】

ゲート構造20は、半導体層16上に成膜されたゲート絶縁膜21と、このゲート絶縁膜21上に形成されたゲート電極22と、ゲート電極22の両側壁に形成された一対のサイドウォールスペーサ23A,23Bとで構成されている。ゲート絶縁膜21は、1nm(ナノメートル)〜数十nm程度の範囲の膜厚を有することができる。ゲート絶縁膜21の構成材料としては、たとえば、シリコン酸化物、シリコン窒化物、あるいは、シリコン酸化物よりも誘電率が高い高誘電率材料(たとえば、窒素添加のハフニウムシリケートなどの酸化ハフニウム系材料)を使用することができる。また、ゲート電極22は、50nm〜500nm程度の範囲の膜厚を有し、不純物が高濃度でドープされた多結晶シリコンや、チタンなどの高融点金属材料を用いて形成されればよい。

【0021】

半導体層16は、数nm〜数百nm程度の厚みを有し、たとえば、単結晶シリコン材料で構成されている。半導体層16には、p型またはn型の導電型を有するソース拡散領域16s及びドレイン拡散領域16dと、これらソース拡散領域16s及びドレイン拡散領域16dに挟まれるボディ領域16bとが形成されている。また、ソース拡散領域16sからドレイン拡散領域16dの方向に突出するLDD(Lightly Doped Drain)領域またはエクステンション領域16seが形成され、ドレイン拡散領域16dからソース拡散領域16sの方向に突出するLDD領域またはエクステンション領域16deが形成されている。本実施の形態のボディ領域16bは、ほぼ完全に空乏化された領域である。

【0022】

また、ゲート構造20のゲート長方向両側には、半導体層16を下地とするエピタキシャル層31A,31Bが形成されている。これらエピタキシャル層31A,31Bは、主に寄生抵抗を低減させる目的で形成されたものである。

【0023】

そして、ゲート構造20と半導体層16と素子分離領域(メサ形状の半導体層16が形成されない領域)とを被覆するように層間絶縁膜40が形成されている。層間絶縁膜40は、たとえば、500nm〜1500nmの範囲内の膜厚を有し、SiO2、SiOC、SiCあるいはSiCNといった絶縁材料で構成されればよい。この層間絶縁膜40には、エピタキシャル層31A,31Bの上面にそれぞれ達するコンタクトホール41A,41Bが形成されており、これらコンタクトホール41A,41Bには、それぞれ、タングステンやタンタルなどの高融点金属材料からなるコンタクトプラグ42A,42Bが埋め込まれている。これらコンタクトホール41A,41Bの下端部は、エピタキシャル層31A,31Bを介してソース拡散領域16s及びドレイン拡散領域16dにそれぞれ電気的に接続されており、コンタクトホール41A,41Bの上端部はそれぞれ上層配線50A,50Bと電気的に接続されている。

【0024】

本実施の形態の半導体装置1では、フォトリソグラフィや紫外線リソグラフィといった半導体リソグラフィでのレチクルの位置ズレにより、コンタクトホール41Bの形成領域が正確な位置からずれて素子分離領域と重複している。このため、コンタクトホール41A,41Bをエッチングで形成する際に、上部絶縁膜15に達する深さまでSOI基板10がエッチングされているが、エッチングバリア膜14の存在により、コンタクトホール41Bが埋め込み絶縁膜12を貫通することが防止される。

【0025】

次に、図2〜図11を参照しつつ本実施の形態の半導体装置1の製造方法の一例を以下に説明する。図2〜図11は、本実施の形態の半導体装置1の製造工程を概略的に示す断面図である。

【0026】

まず、図2に示すように、半導体基材11と埋め込み絶縁膜12と半導体層16Pとが積層されたSOI基板10を用意する。半導体基材11と半導体層16Pとは、シリコン単結晶材料からなる。このSOI基板10の製造方法については後述する。次に、半導体層16Pをメサ形状にエッチング加工するために、フォトリソグラフィやEUV(Extreme Ultra Violet)リソグラフィなどの半導体リソグラフィにより半導体層16P上にレジストパターン19を形成する(図3)。そして、このレジストパターン19をマスクとする異方性エッチングを実行して半導体層16Pを加工する。この結果、図4に示されるように、活性領域をなすメサ形状の凸部を有する半導体層16が形成される。

【0027】

その後、たとえばCVD(Chemical Vapor Deposition)法により、図5に示されるように、図4の構造上に、ハフニウムシリケートなどの高誘電率材料からなる数nm程度の厚みの絶縁膜21Pと、100nm程度の厚みの導電層22Pとを順次成膜する。導電層22Pは、多結晶シリコンや窒化チタンを用いて形成されればよい。次いで、半導体リソグラフィにより図5の構造上にレジストパターン(図示せず)を形成し、このレジストパターンをマスクとするエッチングを実行して図6のゲート絶縁膜21とゲート電極22とを形成する。そして、これらゲート絶縁膜21とゲート電極22とをマスクとして、ゲート電極22の両側の半導体層16内部に不純物60をイオン注入し活性化することで、LDD領域またはエクステンション領域用の不純物拡散領域16se,16deを形成する。

【0028】

その後、たとえばCVD法により、図7の構造上に、シリコン酸化物などの絶縁材料からなる10nm〜300nm程度の厚みの絶縁膜(図示せず)を堆積し、この絶縁膜を異方性エッチングによりエッチバックする。この結果、図8に示されるように、ゲート電極22の両側壁にサイドウォールスペーサ23A,23Bが形成される。これらサイドウォールスペーサ23A,23Bとゲート絶縁膜21とゲート電極22とでゲート構造20が構成される。

【0029】

次に、選択エピタキシャル成長(SEG:Selective Epitaxial Growth)法により、図9に示されるように、半導体層16の露出面を下地とするエピタキシャル層31A,31Bを成膜する。選択エピタキシャル成長法としては、シラン系ガス(たとえば、シランガス、ジシランガスあるいはジクロロシランガス)と塩素系ガスとを含む原料ガスを用いたCVD法が挙げられる。次に、ゲート構造20をマスクとして、エピタキシャル層31A,31Bを介して半導体層16内部に不純物をイオン注入し活性化することにより、ゲート構造20の両側にソース拡散領域16sとドレイン拡散領域16dとが形成される。なお、ソース拡散領域16sとドレイン拡散領域16dとが互いに入れ替わってもよい。

【0030】

次に、たとえばプラズマCVD法により、図9の構造上に、SiO2系材料からなる500nm〜1500nm程度の厚みの層間絶縁膜40を形成する。この層間絶縁膜40の上面は、必要に応じて、たとえばCMP(Chemical Mechanical Polish)を用いて平坦化される。次いで、フォトリソグラフィやEUVリソグラフィなどの半導体リソグラフィにより層間絶縁膜40上にレジストパターン(図示せず)を形成し、このレジストパターンをマスクとする異方性エッチングを実行して層間絶縁膜40をパターニングする。この結果、図11に示されるように、エピタキシャル層31A,31Bを介してソース拡散領域16s及びドレイン拡散領域16dと電気的に接続されたコンタクトホール41A,41Bが形成される。

【0031】

たとえばCVD法により、コンタクトホール41A,41Bの内壁に窒化膜などのバリア膜を形成し、さらに、コンタクトホール41A,41B内部にタングステンなどの高融点材料を埋め込むことで、図1のコンタクトプラグ42A,42Bが形成される。その後は、銅やアルミニウムなどの配線材料からなる上層配線50A,50Bが形成される。

【0032】

本実施の形態の半導体装置1では、図3及び図4に示したように、メサ形状の半導体層16を形成する際に、SOI基板10内部の埋め込み絶縁膜12の上面が露出するまでエッチングが行われる。また、図11に示したように、半導体リソグラフィで使用されたレチクルの位置ズレにより、コンタクトホール41Bの形成領域が素子分離領域と重複(オーバラップ)している。それ故、層間絶縁膜40だけでなく上部絶縁膜15がエッチングされているが、エッチングバリア膜14がエッチングストッパとして機能するので、コンタクトホール41Bが埋め込み絶縁膜12を貫通することが確実に防止される。したがって、半導体基材11と半導体層(SOI層)16との間でショート(電気的短絡)が発生することが確実に防止されるので、歩留まりの向上が可能となる。

【0033】

たとえば、シリコン窒化膜からなるエッチングバリア膜14の膜厚が数nm〜50nm程度(好ましくは5nm〜10nm程度)の範囲内のとき、エッチングバリア膜14のエッチングレート(=R1)に対する上部絶縁膜15のエッチングレート(=R2)の比率(=R2/R1)すなわち選択比を5〜40程度、より好ましくは10〜20程度にすれば、コンタクトホール41Bがエッチングバリア膜14を貫通することを防止することができる。実際の実験において、基板温度を50℃とし、C4F8ガス(流量:26sccm)とArガス(流量:500sccm)とO2ガス(流量:10sccm)とを含むエッチングガスを用いて層間絶縁膜(シリコン酸化膜)40に対する異方性エッチングを実行したとき、コンタクトホール41Bがエッチングバリア膜14を貫通することが防止された。

【0034】

また、埋め込み絶縁膜12の膜厚が十分に薄いとき、半導体基材11をバックゲートとして利用することができる。具体的には、半導体基材(支持基板)11へのバイアス電圧の印加により、SOIトランジスタ1のしきい値電流の制御や、素子特性の劣化またはバラツキの改善が可能となる。たとえば、上部絶縁膜15と下部絶縁膜13とが誘電率3.9のシリコン酸化膜であり、エッチングバリア膜14が誘電率7.5のシリコン窒化膜である場合、シリコン酸化膜の誘電率に比べてシリコン窒化膜の誘電率は約2倍であるため、エッチングバリア膜14の厚みを、上部絶縁膜15と下部絶縁膜13との合計厚みの倍程度の厚みにしても、バックゲート効果を得ることができると考えられる。このような観点から、バックゲート効果を得るために、埋め込み絶縁膜12の全体の膜厚の上限を、たとえば10nm〜20nm程度にすることが望ましい。

【0035】

なお、エッチングバリア膜14の構成材料としてシリコン窒化物に代用する材料を用いてもよい。この場合、エッチングバリア膜14の厚みを、その材質の誘電率のシリコン酸化膜の誘電率に対する比率に相当する膜厚にすることが可能である。

【0036】

次に、図12〜図14を参照しつつ、本実施の形態の半導体装置1の製造に使用されるSOI基板10の製造方法を説明する。図12〜図14は、SOI基板10の製造工程を概略的に示す断面図である。

【0037】

まず、図12(A)に示されるように、単結晶シリコンウエハである半導体基材11の主面を熱酸化して下部絶縁膜(熱酸化膜)13を形成する。次いで、たとえばCVD法により、この下部絶縁膜13上に窒化膜からなるエッチングバリア膜14を成膜する。他方、図12(B)に示されるように、単結晶シリコン材料からなる他の半導体基材17の主面を熱酸化して上部絶縁膜(熱酸化膜)15を形成する。そして、上部絶縁膜15を介して半導体基材17に水素イオン18を打ち込むことにより、一定の深さ(たとえば、表面から0.1μm〜数μmの深さ)に分布する欠陥層17dを形成する。

【0038】

次に、図13に示されるように、半導体基材11上のエッチングバリア膜14と半導体基材17上の上部絶縁膜15とを貼り合わせる。そして、熱処理により、欠陥層17dを境にして半導体基材11から半導体層16Pを剥離することにより、図14のSOI基板10が作製される。半導体層16Pの表面は、必要に応じて研磨される。

【0039】

なお、図14のSOI基板10では、エッチングバリア膜14が下部絶縁膜13と上部絶縁膜15とで挟み込まれている。その理由は、窒化膜とシリコンとの界面準位が素子特性に影響を与えることを抑制するためである。窒化膜とシリコンとの界面準位が素子特性にほとんど影響を与えない場合には、下部絶縁膜13,15の一方または双方を形成しなくてもよい。

【0040】

以上に説明したように実施の形態の半導体装置1は、埋め込み絶縁膜12に窒化膜を有するSOI基板10を使用して作製されるので、コンタクトホール41Bの形成領域が素子分離領域と重複する場合でも、コンタクトホール41Bが埋め込み絶縁膜12を貫通することが防止される。図15は、比較例の半導体装置100の構造を概略的に示す断面図である。図15の構造は、埋め込み絶縁膜12Pがシリコン酸化膜のみからなる点を除いて、実施の形態の半導体装置1の構造と同じである。図15に示されるように、半導体装置100はエッチングバリア膜を有していないので、コンタクトホール41Bが埋め込み絶縁膜12Pを貫通し、半導体基材11の上部領域PAまで到達している。このため、半導体基材11と半導体層16とがショートして不良品が発生するという問題がある。

【0041】

本実施の形態の半導体装置1では、バックゲート効果の実現のために極薄の埋め込み絶縁膜12を有するSOI基板10を使用する場合でも、コンタクトホール41Bが埋め込み絶縁膜12を貫通することを防止することができる。したがって、半導体基材11と半導体層16との間のショート不良を防止することができ、歩留まり向上を実現することができる。

【0042】

以上、図面を参照して本発明の実施の形態について述べたが、これは本発明の例示であり、上記以外の様々な形態を採用することもできる。たとえば、上記実施の形態は、メサ分離法に基づいたSOIトランジスタ構造を有しているが、メサ分離法に代えて、STIやLOCOSを用いて形成された素子分離用絶縁膜を有するSOIトランジスタ構造でも、上記実施の形態の場合と同様に、コンタクトホールがSOI基板内部の埋め込み絶縁膜を貫通することが防止される。

【0043】

図16は、素子分離領域を形成するSTI構造33,34を有する半導体装置2の構造の一例を概略的に示す断面図である。この半導体装置2では、STI構造33,36が、半導体層16Pの表面から埋め込み絶縁膜12に至るまで深さ方向に延在している。一方のSTI構造33は、溝(トレンチ)34と、この溝34内に埋め込まれたSiO2系材料からなる素子分離用絶縁膜35を有しており、他方のSTI構造36も、溝(トレンチ)37と、この溝37内に埋め込まれたSiO2系材料からなる素子分離用絶縁膜38とを有している。

【0044】

STI構造34,37の製造方法は、特に限定されるものではなく、公知の方法を使用してSTI構造34,37を形成すればよい。たとえば、図2のSOI基板10上にシリコン酸化膜とシリコン窒化膜とを順次成膜し、次に、フォトリソグラフィ技術とエッチング技術とにより、これらシリコン酸化膜とシリコン窒化膜とSOI基板10とを選択的にエッチングして素子分離用の溝34,37を形成する。そして、これら溝34,37の内壁を熱酸化する。その後、CVD法により、これら溝34,37の内部にシリコン酸化物などの絶縁膜を堆積させる。さらに、化学機械研磨(CMP:Chemical Mechanical Polishing)法あるいは化学機械平坦化(CMP:Chemical Mechanical Planarization)法により、当該絶縁膜の上面を平坦化する。その後、シリコン酸化膜とシリコン窒化膜とは個別にウェットエッチングにより除去される。以上のプロセスの結果として、図16に示されるようなSTI構造34,37を作製することができる。

【0045】

上記STI構造33,36間の領域には、半導体層16P上に、ゲート絶縁膜71、ゲート電極72及びサイドウォールスペーサ73A,73Bからなるゲート構造70が形成される。ゲート構造70の両側には、ソース拡散領域160sとドレイン拡散領域160dとが形成されている。また、これらソース拡散領域160sとドレイン拡散領域160dとからそれぞれゲート電極72の直下の領域に突出するエクステンション領域160se,160deが形成されている。ボディ領域160bは、ソース拡散領域160sとドレイン拡散領域160dとエクステンション領域160se,160deと埋め込み絶縁膜12とで囲まれている領域である。

【0046】

また、半導体装置2では、上記ゲート構造70と半導体層16PとSTI構造33,36とを被覆するようにSiO2系材料からなる層間絶縁膜80が形成されている。この層間絶縁膜80には、ソース拡散領域160sの上面とドレイン拡散領域160dの上面とにそれぞれ達するコンタクトホール81A,81Bが形成されており、これらコンタクトホール81A,81Bには、それぞれ、タングステンやタンタルなどの高融点金属材料からなるコンタクトプラグ82A,82Bが埋め込まれている。コンタクトホール81A,81Bの上端部はそれぞれ上層配線90A,90Bと電気的に接続されている。

【0047】

図16に示されるように、半導体リソグラフィでのレチクルの位置ズレにより、コンタクトホール81Bの形成領域がSTI構造36と重複している。このため、コンタクトホール81A,81Bをエッチングで形成する際に、エッチングバリア膜14に達する深さまで素子分離用絶縁膜38がエッチングされているが、エッチングバリア膜14の存在により、コンタクトホール81Bが埋め込み絶縁膜12を貫通することが防止されている。

【0048】

上記実施の形態の半導体装置1や変形例の半導体装置2は、SOI基板上にゲート構造20,70が形成されたものであるが、本発明はこれらに限定されるものではない。ゲート構造20,70以外の半導体素子構造がSOI基板10上に形成される構造において、コンタクトホールの形成領域が素子分離領域と重複しても、このコンタクトホールが埋め込み絶縁膜12を貫通することを防止することができる。

【符号の説明】

【0049】

1,2,100 半導体装置、 10 SOI(Silicon On Insulator)基板、 11 半導体基材(支持基板)、 12 埋め込み絶縁膜、 13 下部絶縁膜、 14 エッチングバリア膜、 15 上部絶縁膜、 16 半導体層(SOI層)、 16b ボディ領域、 16s ソース拡散領域、 16d ドレイン拡散領域、 16se,16de エクステンション領域、 17d 欠陥層、 18 水素イオン、 20 ゲート構造、 21 ゲート絶縁膜、 22 ゲート電極、 23A,23B サイドウォールスペーサ、 33,36 素子分離構造(STI構造)、 35,38 素子分離用絶縁膜、 31A,31B エピタキシャル層、 40 層間絶縁膜、 41A,41B コンタクトホール、 42A,42B コンタクトプラグ、 50A,50B 上層配線、 70 ゲート構造、 71 ゲート絶縁膜、 72 ゲート電極、 73A,73B サイドウォールスペーサ、 80 層間絶縁膜、 81A,81B コンタクトホール、 82A,82B コンタクトプラグ、 90A,90B 上層配線。

【特許請求の範囲】

【請求項1】

半導体基材と、

半導体層と、

前記半導体基材と前記半導体層とに挟み込まれ、前記半導体基材から前記半導体層を電気的に絶縁分離する埋め込み絶縁膜と

を備え、

前記埋め込み絶縁膜は、窒化膜を含む

ことを特徴とするSOI基板。

【請求項2】

請求項1に記載のSOI基板であって、前記窒化膜は、シリコン窒化膜であることを特徴とするSOI基板。

【請求項3】

請求項2に記載のSOI基板であって、

前記埋め込み絶縁膜は、埋め込み酸化膜を含み、

前記埋め込み酸化膜は、シリコン酸化膜である

ことを特徴とするSOI基板。

【請求項4】

請求項3に記載のSOI基板であって、前記シリコン酸化膜は、熱酸化膜であることを特徴とするSOI基板。

【請求項5】

請求項3または4に記載のSOI基板であって、前記窒化膜は、化学気相成長法を用いて前記埋め込み酸化膜上に形成された膜であることを特徴とするSOI基板。

【請求項6】

請求項1から5のうちのいずれか1項に記載のSOI基板と、

前記SOI基板上に形成された半導体素子構造と

を備えることを特徴とする半導体装置。

【請求項7】

請求項6に記載の半導体装置であって、

前記半導体素子構造は、

前記SOI基板の当該半導体層の上に形成され、コンタクトホールを有する層間絶縁膜と、

前記コンタクトホールに埋め込まれ、前記半導体層と電気的に接続されたコンタクトプラグと

を含むことを特徴とする半導体装置。

【請求項8】

請求項7に記載の半導体装置であって、

前記半導体素子構造は、前記半導体層上にゲート絶縁膜とゲート電極とを含むゲート構造を有し、

前記半導体層は、

互いに同じ導電型を有し前記ゲート構造の両側に形成された第1及び第2の不純物拡散領域と、

前記第1及び第2の不純物拡散領域の間に且つ前記ゲート構造の直下に形成されたボディ領域と

を含み、

前記第1及び第2の不純物拡散領域のいずれか一方が前記コンタクトプラグと電気的に接続されている

ことを特徴とする半導体装置。

【請求項9】

請求項8に記載の半導体装置であって、

前記コンタクトホールの形成領域が素子分離領域と重複しており、

前記半導体層は、前記素子分離領域を画定するメサ形状の凸部を有する、

ことを特徴とする半導体装置。

【請求項10】

請求項9に記載の半導体装置であって、前記凸部の側壁下端が前記埋め込み絶縁膜の上面に達していることを特徴とする半導体装置。

【請求項11】

請求項8に記載の半導体装置であって、

前記半導体基板の上面から前記埋め込み絶縁膜に至るまで深さ方向に延在する素子分離用絶縁膜をさらに備え、

前記コンタクトホールの形成領域は、前記素子分離用絶縁膜の形成領域と重複している

ことを特徴とする半導体装置。

【請求項12】

請求項8から11のうちのいずれか1項に記載の半導体装置であって、前記半導体層と前記コンタクトプラグとの間に介在し前記半導体層を下地として形成されたエピタキシャル層をさらに備えることを特徴とする半導体装置。

【請求項13】

請求項1から5のうちのいずれか1項に記載のSOI基板を用意する工程と、

前記SOI基板上に半導体素子構造を形成する工程と

を備えることを特徴とする半導体装置の製造方法。

【請求項14】

請求項13に記載の半導体装置の製造方法であって、

前記半導体素子構造を形成する当該工程は、

前記SOI基板の当該半導体層の上に層間絶縁膜を堆積する工程と、

所定のエッチング条件にて前記層間絶縁膜を選択的にエッチングしてコンタクトホールを形成する工程と、

前記半導体層と電気的に接続されたコンタクトプラグを前記コンタクトホールに埋め込む工程と

を含むことを特徴とする半導体装置の製造方法。

【請求項15】

請求項14に記載の半導体装置の製造方法であって、

互いに同じ導電型の不純物を前記半導体層内に導入して第1及び第2の不純物拡散領域を形成する工程をさらに備え、

前記半導体素子構造を形成する当該工程は、前記半導体層上にゲート絶縁膜とゲート電極とを含むゲート構造を形成する工程を含み、

前記第1及び第2の不純物拡散領域は、前記ゲート構造をマスクとして前記半導体層内に前記不純物を導入することにより前記ゲート構造の両側に形成された領域であり、

前記第1及び第2の不純物拡散領域のいずれか一方が前記コンタクトプラグと電気的に接続される

ことを特徴とする半導体装置の製造方法。

【請求項16】

請求項15に記載の半導体装置の製造方法であって、前記半導体層を選択的にエッチングして、素子分離領域を画定するメサ形状の凸部を形成する工程をさらに備え、

前記コンタクトホールの形成領域が前記素子分離領域と重複する

ことを特徴とする半導体装置の製造方法。

【請求項17】

請求項16に記載の半導体装置の製造方法であって、前記半導体層を選択的にエッチングする当該工程では、前記凸部の側壁下端が前記埋め込み絶縁膜の上面に達するまでエッチングが実行されることを特徴とする半導体装置の製造方法。

【請求項18】

請求項15に記載の半導体装置の製造方法であって、前記半導体基板の上面から前記埋め込み絶縁膜に至るまで深さ方向に延在する素子分離用絶縁膜を形成する工程をさらに備え、

前記コンタクトホールの形成領域は、前記素子分離用絶縁膜の形成領域と重複する

ことを特徴とする半導体装置の製造方法。

【請求項19】

請求項14から18のうちのいずれか1項に記載の半導体装置の製造方法であって、

前記コンタクトホールが形成される前に、選択的エピタキシャル成長法により前記半導体層を下地としてエピタキシャル層を形成する工程をさらに備え、

前記コンタクトホールは、前記エピタキシャル層上に形成される

ことを特徴とする半導体装置の製造方法。

【請求項20】

半導体層を含む第1の半導体基材を用意する工程と、

第2の半導体基材の主面上に窒化膜を含む絶縁膜を形成する工程と、

前記第2の半導体基材上の当該絶縁膜と前記第1の半導体基材の当該半導体層とを貼り合わせる工程と

を備え、

前記絶縁膜は、前記半導体層を前記第2の半導体基材から電気的に絶縁分離するように形成されることを特徴とするSOI基板の製造方法。

【請求項21】

請求項20に記載のSOI基板の製造方法であって、

前記第1の半導体基材に不純物イオンを打ち込むことにより一定の深さで分布する欠陥層を形成する工程と、

当該貼り合わせる工程が完了した後に、前記欠陥層を境にして前記第1の半導体基材を2片に分割することにより前記半導体層を前記第1の半導体基材から剥離する工程と

をさらに備えることを特徴とするSOI基板の製造方法。

【請求項22】

請求項20または21に記載のSOI基板の製造方法であって、前記窒化膜は、シリコン窒化膜であることを特徴とするSOI基板の製造方法。

【請求項23】

請求項20から22のうちのいずれか1項に記載のSOI基板の製造方法であって、

前記絶縁膜を形成する工程は、

前記第2の半導体基材の主面上に酸化膜を形成する工程と、

前記酸化膜上に前記窒化膜を形成する工程とを含み、

前記酸化膜は、シリコン酸化膜である

ことを特徴とするSOI基板の製造方法。

【請求項24】

請求項23に記載のSOI基板の製造方法であって、前記酸化膜は、前記第2の半導体基材の当該主面を熱酸化することで形成されることを特徴とするSOI基板の製造方法。

【請求項25】

請求項23または24に記載のSOI基板の製造方法であって、前記窒化膜は、化学気相成長法を用いて前記酸化膜上に形成されることを特徴とするSOI基板の製造方法。

【請求項1】

半導体基材と、

半導体層と、

前記半導体基材と前記半導体層とに挟み込まれ、前記半導体基材から前記半導体層を電気的に絶縁分離する埋め込み絶縁膜と

を備え、

前記埋め込み絶縁膜は、窒化膜を含む

ことを特徴とするSOI基板。

【請求項2】

請求項1に記載のSOI基板であって、前記窒化膜は、シリコン窒化膜であることを特徴とするSOI基板。

【請求項3】

請求項2に記載のSOI基板であって、

前記埋め込み絶縁膜は、埋め込み酸化膜を含み、

前記埋め込み酸化膜は、シリコン酸化膜である

ことを特徴とするSOI基板。

【請求項4】

請求項3に記載のSOI基板であって、前記シリコン酸化膜は、熱酸化膜であることを特徴とするSOI基板。

【請求項5】

請求項3または4に記載のSOI基板であって、前記窒化膜は、化学気相成長法を用いて前記埋め込み酸化膜上に形成された膜であることを特徴とするSOI基板。

【請求項6】

請求項1から5のうちのいずれか1項に記載のSOI基板と、

前記SOI基板上に形成された半導体素子構造と

を備えることを特徴とする半導体装置。

【請求項7】

請求項6に記載の半導体装置であって、

前記半導体素子構造は、

前記SOI基板の当該半導体層の上に形成され、コンタクトホールを有する層間絶縁膜と、

前記コンタクトホールに埋め込まれ、前記半導体層と電気的に接続されたコンタクトプラグと

を含むことを特徴とする半導体装置。

【請求項8】

請求項7に記載の半導体装置であって、

前記半導体素子構造は、前記半導体層上にゲート絶縁膜とゲート電極とを含むゲート構造を有し、

前記半導体層は、

互いに同じ導電型を有し前記ゲート構造の両側に形成された第1及び第2の不純物拡散領域と、

前記第1及び第2の不純物拡散領域の間に且つ前記ゲート構造の直下に形成されたボディ領域と

を含み、

前記第1及び第2の不純物拡散領域のいずれか一方が前記コンタクトプラグと電気的に接続されている

ことを特徴とする半導体装置。

【請求項9】

請求項8に記載の半導体装置であって、

前記コンタクトホールの形成領域が素子分離領域と重複しており、

前記半導体層は、前記素子分離領域を画定するメサ形状の凸部を有する、

ことを特徴とする半導体装置。

【請求項10】

請求項9に記載の半導体装置であって、前記凸部の側壁下端が前記埋め込み絶縁膜の上面に達していることを特徴とする半導体装置。

【請求項11】

請求項8に記載の半導体装置であって、

前記半導体基板の上面から前記埋め込み絶縁膜に至るまで深さ方向に延在する素子分離用絶縁膜をさらに備え、

前記コンタクトホールの形成領域は、前記素子分離用絶縁膜の形成領域と重複している

ことを特徴とする半導体装置。

【請求項12】

請求項8から11のうちのいずれか1項に記載の半導体装置であって、前記半導体層と前記コンタクトプラグとの間に介在し前記半導体層を下地として形成されたエピタキシャル層をさらに備えることを特徴とする半導体装置。

【請求項13】

請求項1から5のうちのいずれか1項に記載のSOI基板を用意する工程と、

前記SOI基板上に半導体素子構造を形成する工程と

を備えることを特徴とする半導体装置の製造方法。

【請求項14】

請求項13に記載の半導体装置の製造方法であって、

前記半導体素子構造を形成する当該工程は、

前記SOI基板の当該半導体層の上に層間絶縁膜を堆積する工程と、

所定のエッチング条件にて前記層間絶縁膜を選択的にエッチングしてコンタクトホールを形成する工程と、

前記半導体層と電気的に接続されたコンタクトプラグを前記コンタクトホールに埋め込む工程と

を含むことを特徴とする半導体装置の製造方法。

【請求項15】

請求項14に記載の半導体装置の製造方法であって、

互いに同じ導電型の不純物を前記半導体層内に導入して第1及び第2の不純物拡散領域を形成する工程をさらに備え、

前記半導体素子構造を形成する当該工程は、前記半導体層上にゲート絶縁膜とゲート電極とを含むゲート構造を形成する工程を含み、

前記第1及び第2の不純物拡散領域は、前記ゲート構造をマスクとして前記半導体層内に前記不純物を導入することにより前記ゲート構造の両側に形成された領域であり、

前記第1及び第2の不純物拡散領域のいずれか一方が前記コンタクトプラグと電気的に接続される

ことを特徴とする半導体装置の製造方法。

【請求項16】

請求項15に記載の半導体装置の製造方法であって、前記半導体層を選択的にエッチングして、素子分離領域を画定するメサ形状の凸部を形成する工程をさらに備え、

前記コンタクトホールの形成領域が前記素子分離領域と重複する

ことを特徴とする半導体装置の製造方法。

【請求項17】

請求項16に記載の半導体装置の製造方法であって、前記半導体層を選択的にエッチングする当該工程では、前記凸部の側壁下端が前記埋め込み絶縁膜の上面に達するまでエッチングが実行されることを特徴とする半導体装置の製造方法。

【請求項18】

請求項15に記載の半導体装置の製造方法であって、前記半導体基板の上面から前記埋め込み絶縁膜に至るまで深さ方向に延在する素子分離用絶縁膜を形成する工程をさらに備え、

前記コンタクトホールの形成領域は、前記素子分離用絶縁膜の形成領域と重複する

ことを特徴とする半導体装置の製造方法。

【請求項19】

請求項14から18のうちのいずれか1項に記載の半導体装置の製造方法であって、

前記コンタクトホールが形成される前に、選択的エピタキシャル成長法により前記半導体層を下地としてエピタキシャル層を形成する工程をさらに備え、

前記コンタクトホールは、前記エピタキシャル層上に形成される

ことを特徴とする半導体装置の製造方法。

【請求項20】

半導体層を含む第1の半導体基材を用意する工程と、

第2の半導体基材の主面上に窒化膜を含む絶縁膜を形成する工程と、

前記第2の半導体基材上の当該絶縁膜と前記第1の半導体基材の当該半導体層とを貼り合わせる工程と

を備え、

前記絶縁膜は、前記半導体層を前記第2の半導体基材から電気的に絶縁分離するように形成されることを特徴とするSOI基板の製造方法。

【請求項21】

請求項20に記載のSOI基板の製造方法であって、

前記第1の半導体基材に不純物イオンを打ち込むことにより一定の深さで分布する欠陥層を形成する工程と、

当該貼り合わせる工程が完了した後に、前記欠陥層を境にして前記第1の半導体基材を2片に分割することにより前記半導体層を前記第1の半導体基材から剥離する工程と

をさらに備えることを特徴とするSOI基板の製造方法。

【請求項22】

請求項20または21に記載のSOI基板の製造方法であって、前記窒化膜は、シリコン窒化膜であることを特徴とするSOI基板の製造方法。

【請求項23】

請求項20から22のうちのいずれか1項に記載のSOI基板の製造方法であって、

前記絶縁膜を形成する工程は、

前記第2の半導体基材の主面上に酸化膜を形成する工程と、

前記酸化膜上に前記窒化膜を形成する工程とを含み、

前記酸化膜は、シリコン酸化膜である

ことを特徴とするSOI基板の製造方法。

【請求項24】

請求項23に記載のSOI基板の製造方法であって、前記酸化膜は、前記第2の半導体基材の当該主面を熱酸化することで形成されることを特徴とするSOI基板の製造方法。

【請求項25】

請求項23または24に記載のSOI基板の製造方法であって、前記窒化膜は、化学気相成長法を用いて前記酸化膜上に形成されることを特徴とするSOI基板の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2012−160637(P2012−160637A)

【公開日】平成24年8月23日(2012.8.23)

【国際特許分類】

【出願番号】特願2011−20521(P2011−20521)

【出願日】平成23年2月2日(2011.2.2)

【出願人】(308033711)ラピスセミコンダクタ株式会社 (898)

【Fターム(参考)】

【公開日】平成24年8月23日(2012.8.23)

【国際特許分類】

【出願日】平成23年2月2日(2011.2.2)

【出願人】(308033711)ラピスセミコンダクタ株式会社 (898)

【Fターム(参考)】

[ Back to top ]