Fターム[5F032DA00]の内容

素子分離 (28,488) | 製造方法 (11,387)

Fターム[5F032DA00]の下位に属するFターム

被着、成長 (2,719)

除去 (4,961)

変質 (1,976)

ウエハの接合、接着 (247)

熱処理(熱酸化、熱窒化を除く) (606)

斜方向の処理(例;イオン注入、エッチング) (61)

平坦化 (764)

マスク工程の省略(セルファライン) (47)

Fターム[5F032DA00]に分類される特許

1 - 6 / 6

評価素子、半導体装置および半導体装置の製造方法

【課題】活性領域と素子分離絶縁膜との段差を精度よく評価する技術を提供する。

【解決手段】半導体基板10に形成されたトレンチに埋め込まれた素子分離絶縁膜18と、前記半導体基板10に形成され不純物を含む活性領域36と、前記活性領域36と前記素子分離絶縁膜18との間の段差を測定するための前記活性領域36の幅W1〜W7が異なる複数の段差測定部52a〜52gと、を具備する評価素子によって前記段差を測定し、この測定結果に基づき、ゲート寸法を調整する。

(もっと読む)

半導体装置の耐圧シミュレーション方法およびシミュレーション装置

【課題】シミュレータの解析領域を縮小した場合であっても計算結果を保証し得る半導体装置の耐圧シミュレーション方法およびかかるシミュレーション方法を実行するシミュレーション装置を提供する。

【解決手段】

半導体装置に含まれるn型領域およびp型領域と同一の不純物濃度を有するnpn構造若しくはpnp構造を含む接合構造に対して一次元シミュレーションを行って、半導体装置における空乏層についての一次元シミュレーション値を取得する。少なくとも1つのpnジャンクションを含む半導体装置の一部である対象領域について、一次元シミュレーション値を用いて多次元シミュレーションを行って、対象領域内のpnジャンクションを逆バイアスしたときの対象領域内部における一次元シミュレーション値に基づく空乏層のエッジ位置を算出する。空乏層のエッジ位置が対象領域内の所定位置に達したときの対象領域への印加電圧を半導体装置の耐圧と推定する。

(もっと読む)

半導体酸化工程の応力分布計算方法

【課題】酸化シミュレーションにおける応力分布計算の精度の劣化を抑えることができる半導体酸化工程の応力分布計算方法を提供する。

【解決手段】酸化種104の拡散方程式を解くことによりシリコン100の酸化に関する物理分布情報を取得し、半導体素子112の領域を等間隔で複数の補助メッシュ32に分割した補助メッシュ空間を設定し、物理分布情報を補助メッシュ32に設定して応力分布を計算し、応力分布を平均化した平均化応力分布を計算し、半導体素子112の領域を非等間隔で複数の実メッシュ34に分割した実メッシュ空間を設定し、補助メッシュ空間における平均化応力分布を実メッシュ空間における応力分布に変換し、変換後の応力分布に基づいて、半導体素子112の形状を更新する。

(もっと読む)

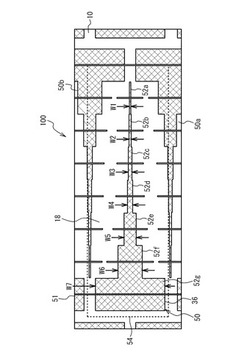

表示装置、表示装置の製造方法及びSOI基板

【課題】SOI基板の大面積化を図り、当該SOI基板を用いた表示装置の製造の生産性を向上させることができる製造技術を提供する。

【解決手段】絶縁表面を有する基板上に複数の単結晶半導体層を接合させ、当該単結晶半導体層を用いてトランジスタを含む回路を形成して表示装置を製造する。単結晶半導体層は、単結晶半導体基板から剥離されたものを適用し、1つの単結晶半導体層の大きさは、一つの表示パネルに相当する大きさ(パネルサイズ)とする。

(もっと読む)

半導体装置の製造方法および製造システム

【課題】トランジスタ領域のSTIとACTIVEの段差を解消し、ゲート電極幅のバラツキを抑制する。

【解決手段】半導体装置の製造方法は、半導体基板上に絶縁膜を形成する工程と、前記半導体基板の所定の箇所に素子分離用のトレンチを形成する工程と、前記トレンチを埋め込み酸化膜で埋め込む工程と、前記半導体基板上に堆積された前記埋め込み酸化膜を前記絶縁膜が露出するまで研磨する工程と、前記研磨後の前記絶縁膜の残膜厚を測定する工程と、前記残膜厚の測定値に基づいて、前記研磨後の埋め込み酸化膜のエッチング量を決定する工程と、前記エッチング量に基づいて、前記研磨後の埋め込み酸化膜をエッチング処理する工程と、を含む。

(もっと読む)

薄膜の製造方法、薄膜及び薄膜素子

【課題】液状の薄膜材料を付与して、所定の領域に薄膜を高精度に形成することができ、しかも工程の簡略化及びコストの低減を果たすことが可能な薄膜の製造方法を提供する。

【解決手段】一方面1aに凹凸が形成されている支持体1の一方面1aに可撓性基板2を配置し、可撓性基板2を凹凸に沿うように付着させ、可撓性基板2の支持体1に付着されている側とは反対側の面において、上記凹凸に追随して設けられている凹凸の凹部に、液状の薄膜材料3を付与し、固化させ、薄膜を形成する。

(もっと読む)

1 - 6 / 6

[ Back to top ]