Fターム[5F032DA74]の内容

Fターム[5F032DA74]に分類される特許

1 - 20 / 606

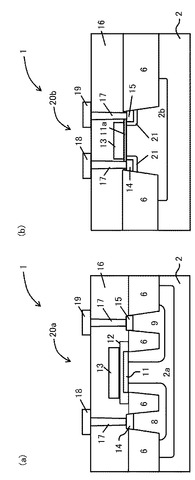

半導体装置およびその製造方法

半導体装置およびその製造方法

【課題】低耐圧トランジスタ特性への影響なく、耐圧特性および動作特性が安定した高耐圧素子を組み込む。

【解決手段】同一の半導体基板2上に、トレンチ分離絶縁膜(プラズマ酸化膜6)によって素子分離された高耐圧素子20aと低耐圧素子20bを設けた半導体装置1において、高耐圧素子形成領域におけるトレンチ分離絶縁膜(プラズマ酸化膜6)の表面高さが低耐圧素子形成領域におけるトレンチ分離絶縁膜(プラズマ酸化膜6)の表面高さよりも低く形成されている。高耐圧素子形成領域におけるトレンチ分離絶縁膜(プラズマ酸化膜6)の表面高さが、高耐圧素子20aのチャネルを形成する半導体基板2の表面に対して−10〜60nm(より好ましくは−10〜30nm)だけ高くなるように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

基板処理方法

【課題】 溝パターン内への絶縁層や配線層等の埋め込みを簡易に行うことができ、工程短縮やコスト低減をはかる。

【解決手段】 基板10の表面に形成された溝内に溶媒を埋め込むための基板処理方法であって、基板10の表面上に溶媒42を供給しながら、基板10の表面に弾性材料で形成された溶媒保持材22を接触させた状態で、基板10の表面と溶媒保持材22とが摺動するように、基板10及び前記溶媒保持材22をそれぞれ回転させる。

(もっと読む)

半導体装置の製造方法

【課題】注入した導電性不純物により形成される結晶欠陥の密度を低減し、歩留まり率が向上するような半導体装置の製造方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板を加熱することにより、半導体基板の基板温度を200から500℃の間の所望の温度に維持すると同時に、半導体基板に導電性不純物をイオン注入法もしくはプラズマドーピング法を用いてドーピングし、ドーピングした導電性不純物を活性化させるための活性化処理を行う。

(もっと読む)

成膜装置及び半導体装置の製造方法

【課題】膜厚を確保することが可能な成膜装置及び半導体装置の製造方法を提供する。

【解決手段】実施形態にかかる成膜装置は溝を有する基板に液体材料を供給して前記溝内に前記液体材料を埋め込み、液層を形成する塗布部と、前記溶液層を乾燥させて固化する乾燥部と、前記乾燥中に前記液層の表面に蒸気を照射する蒸気供給部と、を備えることを特徴とする。

(もっと読む)

トレンチ内に誘電層を形成する方法

【課題】半導体構造の形成方法、より具体的にはトレンチ内における誘電層の形成方法を提供する。

【解決手段】半導体構造を形成する方法は、基板上にシリコン酸化被膜を形成するために、シリコン前駆体と原子酸素前駆体を約150℃以下の処理温度において反応させることを含む。シリコン酸化被膜は酸素含有環境内で紫外線(UV)硬化される。

(もっと読む)

半導体装置の製造方法

【課題】素子の特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板上の一部の領域にマスク膜を形成する工程と、前記マスク膜を形成した領域及び前記マスク膜を形成していない領域の双方において、前記半導体基板の上方に、マスク部材を形成する工程と、前記マスク部材をマスクとしてエッチングを施すことにより、前記マスク膜及び前記半導体基板の上層部分をパターニングする工程と、前記パターニングされたマスク膜をマスクとしてエッチングを施すことにより、前記パターニングされた半導体基板の上層部分の一部を除去する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】FinFETの特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板の上層部分に凹部を形成する工程と、前記凹部内に犠牲材を配置する工程と、前記半導体基板及び前記犠牲材を選択的に除去することにより、一方向に延び、周期的に配列された複数本のフィンを形成する工程と、前記フィン間の空間の下部に素子分離絶縁膜を形成する工程と、前記犠牲材を除去する工程と、前記フィンの露出面上にゲート絶縁膜を形成する工程と、前記素子分離絶縁膜上に、前記フィンを跨ぐように、前記一方向に対して交差した方向に延びるゲート電極を形成する工程と、を備える。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】膜応力の小さい低誘電率の絶縁膜を形成できる基板処理装置を提供する。

【解決手段】処理室内へ無機シリコンガスと酸素含有ガスを供給している状態で、励起エネルギーを処理室内へ供給して、基板表面にシリコン酸化膜を形成するシリコン酸化膜形成工程と、処理室内へ有機シリコンガスを供給している状態で、励起エネルギーを処理室内へ供給して、基板表面にシリコン膜を形成するシリコン膜形成工程と、を行うことにより、処理室内の基板表面に絶縁膜を形成するよう、基板処理装置を構成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を製造することはできないから、高抵抗の拡散抵抗は実現できなかった。

【解決手段】一組の薄膜構造体の対向する間隔に、サイドウォール形成用の絶縁膜を形成する際に生じる空隙を利用して露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を形成する。薄膜構造体を配線抵抗として利用すれば、これらを接続して設けることにより温度特性に優れる抵抗素子を構成することもできる。

(もっと読む)

半導体装置およびその製造方法

【課題】デバイス特性の向上を図る。

【解決手段】半導体装置の製造方法は、半導体基板10に基板部10aと前記基板部上のフィン部10bとを形成する工程と、前記フィン部の側面上に、第1シリコン酸化膜12を形成する工程と、前記第1シリコン酸化膜の側面上に、前記シリコン酸化膜の上面より低い上面を有するポリシラザン膜13を形成する工程と、前記ポリシラザン膜を窒化および酸化することでシリコン酸窒化膜13aに転換する工程と、全面に、前記フィン部を覆うように第2シリコン酸化膜14を形成する工程と、前記第1シリコン酸化膜および前記第2シリコン酸化膜をエッチングすることにより、前記第1シリコン酸化膜の上面を前記シリコン酸窒化膜の上面以下の高さにする工程と、前記フィン部内に高濃度半導体層40を形成する工程と、を具備する。

(もっと読む)

集積回路装置及びその製造方法

【課題】FinFETの特性が均一な集積回路装置及びその製造方法を提供する。

【解決手段】実施形態に係る集積回路装置は、半導体基板の上面に形成され、第1方向に延びる複数本のフィンと、前記フィン間に配置された素子分離絶縁膜と、前記第1方向に対して交差した第2方向に延び、前記素子分離絶縁膜上に設けられたゲート電極と、前記フィンを前記ゲート電極から絶縁する絶縁膜と、を備える。そして、連続して配列された複数本の前記フィンが配置された第1領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも下方の第1の位置に位置し、前記第1領域から見て前記第2方向に位置する第2領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも上方の第2の位置に位置する。また、前記第2領域においては、前記素子分離絶縁膜が前記フィンの側面の全体を覆っている。

(もっと読む)

半導体装置及びその製造方法

【課題】 対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和する。

【解決手段】 半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する半導体装置。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】SiCが用いられる半導体層中において、簡易な工程で再現性よく埋め込み絶縁層を形成する。

【解決手段】単結晶のSiC12の表面の温度を局所的に急激に上昇させ、その後で急激に冷却することによって、単結晶を局所的に非晶質化層30を形成することができる。この非晶質層30は、元の単結晶SiCの導電型や抵抗率に関わらず、高抵抗層(絶縁層)となる。このため、こうした非晶質層を埋め込み絶縁層と同様に使用することができる。このためには、(1)レーザー光を効率的に吸収する層100を局所的に半導体層の上に形成してからレーザー光を照射する、(2)レーザー光を局所的に半導体層に照射する、という2つの手段のいずれかを用いることができる。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】ランプアニールによるレイアウトに起因した温度バラつきを低減する。

【解決手段】この半導体装置10は、基板100と、基板100に埋め込まれた素子分離領域200と、基板100のうち、素子分離領域200の無い領域に形成された不純物層(エクステンション領域322、ソース領域324、エクステンション領域342、及びドレイン領域344)と、を備える。この素子分離領域200は、たとえば、波長300nm以上890nm以下においてSiO2よりも光吸収係数が大きい材料から形成されている光吸収層220を含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させ、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板1の主面に酸化膜として絶縁膜2を形成し、絶縁膜2上に窒化シリコン膜を形成してから、素子分離用の溝4aをプラズマドライエッチングにより形成し、溝4aを埋めるように酸化シリコンからなる絶縁膜6をHDP−CVD法で形成し、CMP処理により溝4aの外部の絶縁膜6を除去し、溝4a内に絶縁膜6を残す。それから、窒化シリコン膜を除去する。その後、絶縁膜2をウェットエッチングで除去して半導体基板1を露出させるが、この際、半導体基板1の主面に140ルクス以上の光を当てながら絶縁膜2をウェットエッチングする。

(もっと読む)

トレンチ埋め込み用樹脂組成物

【課題】基体に形成されたトレンチ内に酸化シリコンを埋め込むために使用するのに好適なトレンチ埋め込み用樹脂組成物を提供すること。

【解決手段】本発明に係るトレンチ埋め込み用樹脂組成物は、酸化シリコン粒子をトレンチ埋め込み用樹脂組成物全体に対して0.35重量%以上2.20重量%以下で、並びに、一般式(1)〜(3)で表される化合物の合計に対して、一般式(1):Si(OR1)4で表されるテトラアルキシキシラン化合物を45mol%以上87mol%以下で、一般式(2):R2Si(OR1)3で表されるトリアルコキシシラン化合物を10mol%以上50mol%以下で、そして一般式(3):R22Si(OR1)2で表されるジアルコキシシラン化合物を1.5mol%以上3.6mol%以下で含有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させる。

【解決手段】シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させ、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成し、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。

(もっと読む)

半導体装置の製造方法

【課題】高アスペクト比の要求される溝内に緻密な膜質の酸化シリコン膜を形成した素子分離領域を提供する。

【解決手段】半導体基板上にマスク窒化膜3をマスクに素子分離溝4Aを形成し、ライナー窒化膜形成後、気相法により流動性シラザン化合物膜7を溝4Aの上方でマスク窒化膜3の上面より高くなるように形成した後、酸化性雰囲気下で熱処理して第一の酸化シリコン膜8に変換すると同時に緻密化し、その後マスク窒化膜3上面まで平坦化する。

(もっと読む)

1 - 20 / 606

[ Back to top ]