Fターム[5F032DA41]の内容

Fターム[5F032DA41]の下位に属するFターム

Fターム[5F032DA41]に分類される特許

1 - 20 / 77

トレンチ埋め込み方法、及びトレンチ埋め込み用組成物

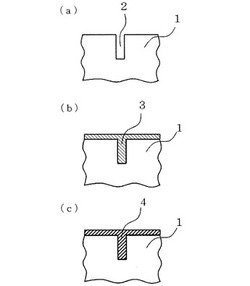

【課題】高アスペクト比のトレンチ内に埋め込んだ際に、クラック、及びボイドが生じにくく、かつ高密度に埋め込むことができるトレンチ埋め込み方法。

【解決手段】(1)トレンチ2を有する基体1上に、シロキサン系重合体、空孔形成剤、及び有機溶媒を含むトレンチ埋め込み用組成物を、少なくとも該組成物が前記トレンチ内に充填されるように塗布し、塗膜3を形成する工程、及び、(2)工程(1)で得られた塗膜3に加熱処理および光処理の少なくともいずれか一方を行う工程、を含むトレンチ埋め込み方法。

(もっと読む)

半導体装置の製造方法

【課題】レーザ光の照射を利用したエッチング加工による半導体装置の製造方法であって、複雑形状や深くて大きい除去領域等のエッチング加工が必要な広範囲の半導体装置の製造に適用可能で、高いエッチング速度が得られる半導体装置の製造方法を提供する。

【解決手段】単結晶シリコンからなる基板10に対して、焦点位置を移動させてレーザ光Lをパルス照射し、前記単結晶シリコンを部分的に多結晶化して、前記単結晶シリコン中に連続した改質層11を形成する改質層形成工程と、前記改質層11をエッチングして除去するエッチング工程と、を備える半導体装置の製造方法とする。

(もっと読む)

半導体装置

【課題】本発明は、SOIにおいて適したゲッタリング方法を適用して得られる半導体装置を提供する。

【解決手段】埋め込み酸化膜と、埋め込み酸化膜上に表面シリコン層を有するSOI構造を有する半導体装置において、埋め込み酸化膜上に、表面シリコン層を活性層として有するトランジスタと、素子分離絶縁膜を有し、素子分離絶縁膜上に容量が形成されており、素子分離絶縁膜に希ガス元素又は金属元素が含まれていることを特徴とする半導体装置とする。

(もっと読む)

薄膜トランジスタとその製造方法、薄膜トランジスタアレイとその製造方法、及び、ディスプレイ装置

【課題】製造工程において半導体膜の膜質を低下させることなくその性能を維持し、少ない工程数によって、かつ、製造上の歩留まり及びスループットの優れた構造を有する薄膜トランジスタ及びその製造方法等を提供する。

【解決手段】薄膜トランジスタ100は、酸化物半導体膜120を有し、当該酸化物半導体膜120は、各薄膜半導体毎に、ゲート電極160下及び隣接された薄膜トランジスタ間とにそれぞれ形成された第1領域121及び122と、ソース電極140及びドレイン電極150下であって第1領域121の前記水平方向におけるそれぞれの両端に並設されており、ソース電極140及びドレイン電極150にそれぞれ電気的に接続され、かつ、非駆動時に前記第1領域121及び122より低抵抗である第2領域123及び124と、を有している。

(もっと読む)

空洞半導体基板、ならびに空洞半導体基板および半導体素子の製造方法

【課題】 生産性に優れる空洞半導体基板、ならびに空洞半導体基板および半導体素子の製造方法を提供する。

【解決手段】 空洞半導体基板1は、支持基板10と、半導体基板20と、を有する。この半導体基板20は、下主面21bの上に一体的に形成され且つ当該下主面21bから突出している脚部22を介して支持基板10の上に張り合わされている。この半導体基板20は、下主面21bが支持基板10から離隔している。

(もっと読む)

有機トランジスタ及び有機トランジスタの製造方法

【課題】導体層におけるソース電極とドレイン電極との電極間のチャネル領域が結晶相であり、且つ該半導体層における該チャネル領域以外の第2の領域が非結晶相である構成ではない場合に比べて、半導体素子間の電気的な分離が実現された有機トランジスタを提供する。

【解決手段】有機トランジスタ10は、基板12上に、ゲート電極14G、ゲート絶縁膜16、ソース電極18S及びドレイン電極18D、及び半導体層20が設けられている。半導体層20における、ソース電極18S及びドレイン電極18Dとの電極間の領域であるチャネル領域20Aは、結晶相とされている。また、半導体層20における、このチャネル領域20A以外の第2の領域20Bは、非結晶相とされている。

(もっと読む)

半導体装置の製造方法

【課題】SOIデバイスにおいて生じやすい基板浮遊問題やホットキャリアの問題を充分に抑制することが可能で、広く分布する部分分離絶縁膜であっても周囲の構造に対し結晶欠陥を生じさせにくい半導体装置の製造方法を提供する。

【解決手段】各MOSトランジスタTR1の間に設けられた部分分離絶縁膜5b内におよそ一定の間隔を置いて、素子としての機能を有しないダミー領域DM1を形成する。これにより、部分分離絶縁膜5b下のシリコン層3bよりも抵抗値の低いダミー領域DM1の占める割合が増加して、基板浮遊問題やホットキャリアの問題の抑制が行えるようになる。

(もっと読む)

半導体装置およびその作製方法

【課題】特性の良い光電変換素子を有する半導体装置を提供することを目的の一とする。または、簡単な工程で、特性の良い光センサ光電変換装置を有する半導体装置を提供することを目的の一とする。

【解決手段】光透過性を有する基板と、光透過性を有する基板上の絶縁層と、絶縁層上の、光電変換を奏する半導体領域、第1の導電型を示す半導体領域、および、第2の導電型を示す半導体領域を有する単結晶半導体層と、第1の導電型を示す半導体領域と電気的に接続された第1の電極と、第2の導電型を示す半導体領域と電気的に接続された第2の電極とを有する光電変換素子とを備える半導体装置を提供する。

(もっと読む)

ポリシラザン系トレンチ埋め込み用組成物

【課題】基体に形成されたトレンチ内にシリコン酸化物を埋め込むために使用するのに好適な、トレンチへの埋め込み性が高く、硬化収縮率が小さく、かつ良好なクラック耐性を有するシリコン酸化物塗膜を与えるトレンチ埋め込み用組成物を提供すること。

【解決手段】水素化ポリシラザン化合物と、シリカ粒子に由来する構造を有する反応物とを含むことを特徴とするトレンチ埋め込み用組成物を提供する。

(もっと読む)

ポリシラン系トレンチ埋め込み用組成物

【課題】基体に形成されたトレンチ内にシリコン酸化物を埋め込むために使用するのに好適な、トレンチへの埋め込み性が高く、硬化収縮率が小さく、かつ良好なクラック耐性を有するシリコン酸化物塗膜を与えるトレンチ埋め込み用組成物を提供すること。

【解決手段】水素化ポリシラン化合物と、シリカ粒子に由来する構造を有する反応物とを含むことを特徴とするトレンチ埋め込み用組成物を提供する。

(もっと読む)

半導体装置の製造方法

【課題】微細なSTI溝であっても、空孔を形成させることなく絶縁膜を埋め込むことができる。

【解決手段】本発明の半導体装置の製造方法は、基板101にSTI溝を形成する工程と、STI溝の側壁及び底面に熱酸化膜104を形成する工程と、STI溝の底部に位置する熱酸化膜104の表面をプラズマ処理する工程と、STI溝の内部にCVD法により絶縁膜105を形成する工程と、を含む。

(もっと読む)

ポリシロキサン系トレンチ埋め込み用反応物

【課題】基体に形成されたトレンチ内に酸化シリコンを埋め込むために使用するのに好適な溶液のポットライフが長く、トレンチへの埋め込み性が高く、HF耐性、クラック耐性を有するトレンチ埋め込み用反応物を提供する。

【解決手段】トレンチ埋め込み用縮合反応物を、該縮合反応物が少なくともポリシロキサン化合物とシリカ粒子との縮合反応物を含み、該ポリシロキサン化合物がHSiO3/2基、MeHSiO基、及びH2SiO基から選ばれる基の少なくとも一種を40mol%以上有し、該ポリシロキサンの重量平均分子量が1000以上200000以下であり、該シリカ粒子の平均一次粒径が1nm以上100nm以下とする。

(もっと読む)

PECVDを用いた流動性誘電体による間隙の充填

【課題】アスペクト比が高くて幅が狭い凹状フィーチャーに誘電層を形成するための新規方法を提供する。

【解決手段】間隙に流動性重合膜をプラズマ強化化学気相成長(PECVD)法によって形成した後で、当該膜を誘電材料に変換するためのインサイチュ(in−situ)処理を実行することを含む。インサイチュ処理は、純粋な熱処理プロセスまたはプラズマ処理プロセス。堆積−インサイチュ処理−堆積−インサイチュ処理というプロセスを実行して、間隙に誘電層を形成する。この一連の手順は、間隙をボトムアップ式に充填するべく必要なだけ繰り返される。エクサイチュ処理後プロセスは、間隙の充填が完了した後で実行される。特定の実施形態によると、誘電率が3.0未満の膜が形成される。上記プロセスは、フロントエンドおよびバックエンドの間隙充填に利用可能である。

(もっと読む)

シリコン酸化膜の形成方法および不揮発性半導体記憶装置の製造方法

【課題】低温で良好な絶縁膜であるシリコン酸化膜を形成する。

【解決手段】シリコン基板1上にトレンチ1a、1bを形成し、シラザン結合を有するポリマーを有機溶媒に溶かした塗布剤を塗布して塗布膜を形成する。塗布膜に含まれる有機溶媒を気化させてポリマー膜を形成する。ポリマー膜に90℃以下の温度で紫外線を照射し、そのポリマー膜を50℃以上80℃未満の温度の純水または水溶液中に浸漬することによってシリコン酸化膜3に転換する。

(もっと読む)

半導体装置の製造方法

【課題】1000℃以上の高温処理ができないものにおいても、トレンチ内のボイドによって半導体層に歪みやクラックが発生してしまわないようにする。

【解決手段】活性層12の上に第1、第2下地酸化膜14、15を形成し、活性層12が露出するように各下地酸化膜14、15をパターニングする(図2(b))。パターニングした各下地酸化膜14、15をマスクとして活性層12にトレンチ16を形成する(図2(c))。そして、トレンチ16の側壁に側壁酸化膜17を形成し(図2(d))、トレンチ16内外の空間が繋がるように、側壁酸化膜17の上に第1層間絶縁膜18を形成する(図3(a))。この後、第1層間絶縁膜18の上に埋め込み材19を形成し(図3(b))、埋め込み材19を溶融させて、トレンチ16内の空間を埋め込み材19で埋め込む熱処理を行う(図3(c))。

(もっと読む)

半導体装置の製造方法

【課題】溝部形成にマスクとして用いたSiO2膜を除去する際に用いられた薬液が、溝部が疎水性であるとはじかれてしまい、はじかれた薬液が溝部で囲まれた領域において空気を抱え込み気泡が発生するという現象があり、これをなくす溝部形成方法を提供する。

【解決手段】マスクを用いて、シリコン基板101にドライエッチングにより溝部106を形成し、その疎水性の溝部106の内部に親水化処理を行った後に、溝部形成にマスクとして用いたSiO2膜104をウェット処理により除去する。

(もっと読む)

シャロー・トレンチ・アイソレーション構造とその形成方法

【課題】絶縁特性に優れたシャロー・トレンチ・アイソレーション構造とそれを形成するための簡便かつ低コストな方法の提供。

【解決手段】表面の溝構造が二酸化ケイ素膜により埋設されており、前記二酸化ケイ素膜が前記基板の表面側に局在し、前記溝の底部に空孔を具備してなるシャロー・トレンチ・アイソレーション構造。このようなアイソレーション構造は、基板表面にポリシラザン組成物を塗布し、前記塗膜の表面に紫外線を照射して、塗膜の表面近傍にあるポリシラザンの一部を硬化させ、さらに前記塗膜を焼成することにより形成させることができる。

(もっと読む)

単結晶SiC基板の製造方法および単結晶SiC基板

【課題】SiC層とSiO2等の埋め込み絶縁層との界面を均一な状態にして結晶性のよいSiC層が得られ、しかも低コストで生産性のよい単結晶SiC基板の製造方法を提供する。

【解決手段】所定厚さの表面Si層3と埋め込み絶縁層4とを有するSi基板1を準備し、上記Si基板1を炭素系ガス雰囲気中で加熱して上記表面Si層3を単結晶SiC層6に変成させる単結晶SiC基板の製造方法であって、上記表面Si層3を単結晶SiC層6に変成させる際に、埋め込み絶縁層4との界面8近傍のSi層を残存Si層5として残す。

(もっと読む)

シリコン酸化膜の成膜方法、シリコン酸化膜、半導体装置および半導体装置の製造方法

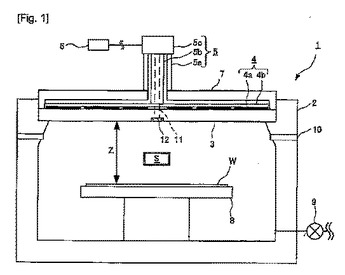

プラズマ処理装置1のチャンバ2内に、シリコン化合物ガス、酸化性ガス、および希ガスを供給する。マイクロ波をチャンバ2内に供給し、マイクロ波により生成されたプラズマで、被処理基板上にシリコン酸化膜を形成する。希ガスの分圧比は、シリコン化合物ガスと酸化性ガスと希ガスを併せたトータルガス圧の10%以上の割合であって、シリコン化合物ガスと酸化性ガスの有効流量比(酸化性ガス/シリコン化合物ガス)は、3以上11以下とする。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのレイアウトが微細化された場合であっても、STI法に起因した電気的特性の劣化を抑制することができる半導体装置の製造方法を提供する。

【解決手段】シリコン基板SB上に、無応力状態、圧縮応力状態、および1GPaよりも小さい引張応力状態のいずれかの状態を有するシリコン窒化膜ST1が形成される。シリコン基板SBのシリコン窒化膜ST1が形成された側に溝部TRが形成される。溝部TRを埋め、かつシリコン窒化膜ST1を覆うように、埋込シリコン酸化膜BIが形成される。シリコン窒化膜ST1が露出するまで埋込シリコン酸化膜BIの表面側が研磨される。

(もっと読む)

1 - 20 / 77

[ Back to top ]