Fターム[5F032DA01]の内容

Fターム[5F032DA01]の下位に属するFターム

Fターム[5F032DA01]に分類される特許

1 - 20 / 54

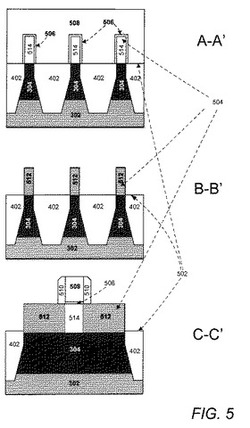

バッファ付きフィンFETデバイス

【課題】フィンFETデバイスのロバストネスを向上させる。

【解決手段】トランジスタデバイスであって、半導体基板と、半導体基板に形成されたバッファ付き垂直フィン状構造であって、垂直フィン状構造は、ドレーン領域とソース領域512との間にチャンネル領域514を含む上位の半導体層と、上位の半導体層の下のバッファ領域304であって、第1のドーピング極性を有するバッファ領域と、第1のドーピング極性と反対である第2のドーピング極性を有するウェル領域302の少なくとも一部分と、バッファ領域とウェル領域との間の少なくとも1つのp−n接合であって、該垂直フィン状構造の水平断面を少なくとも部分的にカバーする少なくとも1つのp−n接合とを含むバッファ付き垂直フィン状構造と、上位の半導体層のチャンネル領域をおおい形成されたゲートスタックとを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置及びその製造方法並びに抵抗器及び半導体素子

【課題】pn接合におけるリーク電流を抑制する。

【解決手段】N−型半導体層10と、シリサイド層20sがその表面に形成されたP−型半導体層20とが、絶縁体9上に形成される。半導体層10にはPMOSトランジスタを、半導体層20にはNMOSトランジスタを、それぞれ形成することができる。半導体層10,20がpn接合J50aを形成する場合、これはシリサイド層20sの端部から近く、結晶欠陥が小さい位置に存在するので、ここにおけるリーク電流は非常に小さい。半導体層10,20が形成するpn接合は、シリサイド層20sの端部から2μm以下の距離にあることが望ましい。

(もっと読む)

半導体装置の製造方法

【課題】素子分離領域に用いる微細化したトレンチを、ボイドを発生させることなく絶縁膜で埋設する。これにより、素子分離領域を介して隣接して配置する素子間の短絡を防止し、製造歩留まりの低下を抑制する。

【解決手段】半導体装置の製造方法は、半導体基板内のトレンチ内に、内部にボイドを有する第1絶縁膜を形成する。この後、エッチングにより、トレンチ内に第1絶縁膜の一部が残留すると共にボイドが露出するように第1絶縁膜を除去する。次に、ALD法により、ボイド内及びトレンチの露出した内壁上に第2絶縁膜を成膜した後、エッチングステップとデポジションステップを有するHDP−CVD法のサイクルを1サイクル以上、行うことにより、素子分離領域を形成する。

(もっと読む)

半導体装置の製造方法

【課題】エッチングレートを高くしつつ、均一な角度の側壁面を有するトレンチを形成できるトレンチ形成工程を含む半導体装置の製造方法を提供する。

【解決手段】アスペクト比が所定値となるまでは保護膜形成工程と保護膜剥離工程およびエッチング工程の3工程によってトレンチ12の底部を掘り進め、アスペクト比が所定値以上となると保護膜形成工程とエッチング工程の2工程によってトレンチ12の底部を掘り進める。これにより、アスペクト比が所定値以上となったときに、ダメージ層14の厚みに応じてトレンチ12のうちエッチング工程によってエッチングされる幅が狭くなるようにでき、半導体基板10のうちダメージ層14とダメージ層14ではない部分の境界の角度がほぼ所望の角度となるようにできる。また、高アスペクト比の領域では2工程によってトレンチ12の底部を掘り進められるため、エッチングレートも増大する。

(もっと読む)

有機トランジスタ及び有機トランジスタの製造方法

【課題】導体層におけるソース電極とドレイン電極との電極間のチャネル領域が結晶相であり、且つ該半導体層における該チャネル領域以外の第2の領域が非結晶相である構成ではない場合に比べて、半導体素子間の電気的な分離が実現された有機トランジスタを提供する。

【解決手段】有機トランジスタ10は、基板12上に、ゲート電極14G、ゲート絶縁膜16、ソース電極18S及びドレイン電極18D、及び半導体層20が設けられている。半導体層20における、ソース電極18S及びドレイン電極18Dとの電極間の領域であるチャネル領域20Aは、結晶相とされている。また、半導体層20における、このチャネル領域20A以外の第2の領域20Bは、非結晶相とされている。

(もっと読む)

半導体装置及びその製造方法

【課題】例えばフィン型の半導体装置とその製造方法を提供すること。

【解決手段】半導体基板102上に第1の層108と、この第1の層上に形成された第の2層110と、この第2の層上に形成された第3の層112とを含む多層構造104を形成し、前記半導体基板と前記多層構造との上部を除去することにより、前記半導体基板上に複数のフィン202とこのフィン上に前記多層構造204の一部を形成し、前記フィンの間206に、上面が多層構造の上面と一致する分離材料300を形成し、前記第2の層を露出するよう前記第3の層と前記分離材料の上部とをエッチングし、前記第1の層が露出するように前記第2の層と残存する前記分離材料の上部の一部とをエッチングする。

(もっと読む)

半導体装置

【課題】トランジスタ間の分離性が良好な半導体装置を提供する。

【解決手段】半導体装置において、第1導電型の半導体基板と、前記半導体基板の上層部分を複数の能動領域に区画する素子分離絶縁膜と、前記能動領域の上部に相互に離隔して形成された第2導電型のソース層及びドレイン層と、前記半導体基板上における前記ソース層と前記ドレイン層との間のチャネル領域の直上域に設けられたゲート電極と、前記半導体基板と前記ゲート電極との間に設けられたゲート絶縁膜と、第1導電型であり、実効的な不純物濃度が前記半導体基板の実効的な不純物濃度よりも高く、前記能動領域における前記ソース層及び前記ドレイン層の直下域に形成され、前記ゲート電極の直下域には形成されていないパンチスルーストッパ層と、を設ける。

(もっと読む)

改善されたアイソレーションを備えるハイブリッド基板及びハイブリッド基板の簡素化した製造方法

【課題】実施が容易なハイブリッド基板の製造方法の提供。

【解決手段】アイソレーション領域5と、第1アクティヴ領域1と、第2アクティヴ領域3とを画定するエッチング・マスクを形成するステップと、少なくともアイソレーション領域5と第1半導体材料2の第1アクティヴ領域1とを画定するために、第1半導体材料2から作られた層及び第2半導体材料4から作られた層と、第2アイソレーション材料から作られた層6とをパターニングし、第1アクティヴ領域1の主面を解放することによって基板内に空間を形成し、第1アクティヴ領域1の上方でエッチング・マスクを除去するステップと、空間及びエッチング・マスクに第1アイソレーション材料を充填するステップと、第1アイソレーション材料を平坦化するステップと、第1アクティヴ領域の主面が解放されるまで、第1アイソレーション材料をエッチングするステップと、を連続的に備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】メモリ領域の高密度化を図ることができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置は、半導体基板10上にメモリセル領域と周辺回路領域とを有する。まず、メモリセル領域の半導体基板10に溝を形成し、メモリセル領域の溝内に酸化膜を形成し、メモリセル領域の溝内における底面の酸化膜のみを除去し、メモリセル領域の溝をシリコンで埋めることで、リソグラフィ限界以下の幅の酸化膜からなる素子分離20を形成する。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ分離構造を有する半導体装置においてトランジスタのドレイン電流の減少などを防止する。

【解決手段】半導体基板10の主表面に活性領域11を分離するトレンチ埋込材21を備え、この埋込材の表面を、少なくとも半導体基板10に接する部分で半導体基板10の主表面より所定高さ落ち込むように形成する。

(もっと読む)

半導体素子及び半導体素子のパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を倍加させる半導体素子のパターン形成工程及び該工程を容易に適用可能な構造の半導体素子を提供する。

【解決手段】半導体素子は、第1方向に相互平行に延びている複数のラインパターンを含む。複数のラインパターンのうちから選択される複数の第1ラインパターンは、第2方向に沿って交互に選択されて両側で各々隣接している2つのラインパターンの両端部のうち、素子領域の第1端部にさらに近い各端部に比べて、第1端部からさらに遠く位置する第1端部を有する。複数のラインパターンのうちから選択される複数の第2ラインパターンは、第2方向に沿って交互に選択され、両側で各々隣接している2つのラインパターンの両端部のうち、第1端部にさらに近い各端部より、第1端部からさらに近く位置する第2端部を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】従来の同一サイズの半導体装置と比較してゲート耐圧を向上させるとともに、素子分離層をバーズビークを含まない構造とすることにより素子分割領域の面積を縮小し、素子の微細化を図ることができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体基板表面に素子形成領域から素子分割領域に亘って延在するLOCOS膜を形成する。素子形成領域内の半導体基板上にLOCOS膜に接続されたゲート酸化膜を形成する。LOCOS膜およびゲート酸化膜を覆うように導電膜を形成する。導電膜を部分的にエッチングしてゲート酸化膜およびLOCOS膜の一部を覆うゲート電極を形成する。導電膜のエッチングによって露出したLOCOS膜を部分的にエッチングしてLOCOS膜を素子分離層とゲート酸化膜の端部を構成する高膜厚部とに分割する。LOCOS膜のエッチングによって露出した半導体基板の表面にイオン注入を行ってゲート電極を挟む位置にドレイン領域およびソース領域を形成する。

(もっと読む)

半導体デバイス、その製造装置及び製造方法

【課題】酸化膜の形成に自由度をもたせる。低温で窒素成分を低減または含まない酸化膜を形成する。バッチ方式の成長装置にて低温で厚い酸化膜膜を形成する。

【解決手段】アルキル基或いはアルコキシ基を含むシリコン系のガス又はシロキサンガス又はシラザンガスと、前記ガスを酸化させる酸化剤とを、減圧状態で500℃以下の温度下で反応させる。前記ガスに対して、シランガス、ジシランガス、リン系ガス、又は、ボロン系ガスを添加剤として反応させる。

(もっと読む)

成膜装置およびそれを用いた成膜方法

【課題】超臨界流体に原料を溶解させた処理媒体を用いてトレンチ内部を埋め込むに際し、トレンチ内部にボイドが残されないように成膜を行う。

【解決手段】ヒータ23に第1の電圧を印加する間に基板30の表面31側よりも裏面32側の温度上昇速度を大きくする第1の工程と、ヒータ23に第2の電圧を印加する間に基板30の裏面32側よりも表面31側の温度下降速度を大きくする第2の工程とを繰り返し、基板30の表面31側と裏面32側との間の温度勾配を大きくすることにより基板30の表面31側に成膜を行う。これにより、基板30の表面31側と裏面32側との温度変化速度に差を生じさせ、基板30の表面31側と基板30の裏面32側との温度差を大きくする。したがって、溝33の底部における成膜の速度が溝33の開口部側よりも速くなり、溝33の底から順に成膜することが可能となる。

(もっと読む)

成膜装置およびそれを用いた成膜方法

【課題】超臨界流体に原料を溶解させた処理媒体を用いてトレンチ内部を埋め込むに際し、トレンチ内部にボイドが残されないように成膜を行う。

【解決手段】切替部30によって処理媒体供給部10から処理媒体70をチャンバ40に供給することにより基板50の表面51側に埋め込み膜60を形成する成膜工程と、切替部30によってエッチング媒体供給部20からエッチング媒体80を供給することにより溝53の開口部側に形成された埋め込み膜60をエッチングするエッチング工程と、を繰り返し行う。これにより、溝53の開口部側に形成された埋め込み膜60をエッチング媒体80によって選択的にエッチングして溝53の開口部が埋め込み膜60によって閉塞されることを抑制しつつ、基板50の表面51側に成膜を行う。

(もっと読む)

半導体装置の製造方法

【課題】化学機械研磨におけるストッパー膜の削れが小さく、半導体装置の製造における歩留まりを向上させる。

【解決手段】本発明の半導体装置の製造方法は、シリコン基板11を覆うようにアモルファスシリコン膜14を形成する工程と、アモルファスシリコン膜14およびシリコン基板11の一部を除去して、シリコン基板11の表面に素子分離溝15を形成する工程と、素子分離溝15を埋め込むようにアモルファスシリコン膜14上に絶縁膜16を形成する工程と、アモルファスシリコン膜14をストッパとして絶縁膜16を化学機械研磨し、絶縁膜16の上面を平坦化する工程とを有する。

(もっと読む)

SRAMデバイスにおけるHOTプロセスSTIおよび製造方法

【課題】H0T(ハイブリッド配向技術)プロセスおよび個々のデバイス間のSTI(シャロウトレンチアイソレーション領域)の組み合わせを使用して、同じ集積回路上のSRAMおよびロジック回路を提供する。

【解決手段】STIを備えたHOT基板上に複数のSRAM(1208)が形成され、さらに、複数のロジック回路が、複数のSOI(1202)領域上の一部のデバイスおよび複数のSOI(1202)領域上の他のデバイスと共に同じチップ上に形成される。

(もっと読む)

半導体装置

【課題】パターン用トレンチの周囲に結晶欠陥が生じても、その結晶欠陥が広範囲に広がるのを防止することができる半導体装置を提供する。

【解決手段】半導体層2の表面には、アライメントパターン7Aが形成されている。アライメントパターン7Aは、幅がb(b>a、たとえば、6μm)の直線部13を複数含んでいる。アライメントパターン用トレンチ14は、アライメントパターン7Aの直線部13の端部において、角部23を有している。半導体層2の表層部には、各アライメントパターン7A,7Bを取り囲む第1環状パターン8が形成されている。第1環状パターン8の幅は、分離部4の幅と同じ大きさaに設定されている。第1環状パターン8の屈曲部8Bは、円弧状に形成されており、その外周縁における曲率半径c2が11μm以上に設定されている。

(もっと読む)

ボイドフリーギャップ充填に対する誘電体膜品質を向上させる方法及びシステム

【課題】誘電体中にボイドやシームを生ずることなく充填するシリコン酸化物層を基板上に形成する方法を提供する。

【解決手段】基板の少なくとも一部を覆う第1の酸化物層を形成するステップであって、該第1の酸化物層が、残留する水、水酸基及び炭素種を含むステップとを含む。該方法はさらに、該第1のシリコン酸化物層と部分的に混合されている複数の非晶質シリコン成分を形成するために、該第1の酸化物層を複数のシリコン含有種に曝すステップを含む。また、該方法は、該複数の非晶質シリコン成分と部分的に混合されている該第1のシリコン酸化物層を、酸化環境中でアニーリングして、第2のシリコン酸化物層を該基板上に形成するステップを含む。非晶質シリコン成分の少なくとも一部は、酸化されて、該第2のシリコン酸化物層の一部になり、該第2のシリコン酸化物層内の未反応の残留する水酸基及び炭素種は、実質的に除去される。

(もっと読む)

1 - 20 / 54

[ Back to top ]