Fターム[5F032DA12]の内容

Fターム[5F032DA12]の下位に属するFターム

異種物質のエピタキシャル (189)

多結晶・非晶質と単結晶の同時成長 (17)

Fターム[5F032DA12]に分類される特許

1 - 20 / 264

半導体装置の製造方法

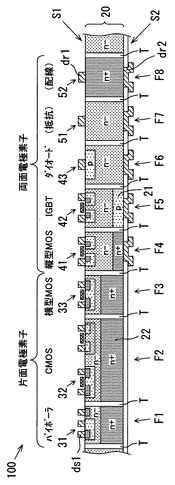

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

半導体装置

【課題】注入元素子から被注入素子への電子の移動を抑制する効果が高く、素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】第1および第2の主表面を有する半導体基板SUB内にはエピタキシャル層EPPと、n型不純物領域NRを含む注入元素子と、注入元素子と間隔を隔てて形成された被注入素子と、注入元素子と被注入素子との間の領域の少なくとも一部に形成され、注入元素子と被注入素子とを結ぶ方向に対して交差する方向に延在する接地電位が印加されたn型領域GNNおよびp型領域GPPを有するバリア層BRとを備える。さらに半導体基板SUB内でエピタキシャル層EPPに接するように形成されたフローティングp型裏面領域FLPを有する。

(もっと読む)

半導体装置の製造方法

【課題】素子の特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板上の一部の領域にマスク膜を形成する工程と、前記マスク膜を形成した領域及び前記マスク膜を形成していない領域の双方において、前記半導体基板の上方に、マスク部材を形成する工程と、前記マスク部材をマスクとしてエッチングを施すことにより、前記マスク膜及び前記半導体基板の上層部分をパターニングする工程と、前記パターニングされたマスク膜をマスクとしてエッチングを施すことにより、前記パターニングされた半導体基板の上層部分の一部を除去する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造のフラッシュメモリーの提供

【解決手段】

半導体基板1上にシリコン窒化膜2及びシリコン酸化膜3が選択的に設けられ、シリコン酸化膜3上には、選択的に横(水平)方向エピタキシャルSi層5が設けられ、Si層5の両側面には、それぞれ側面を接して横(水平)方向エピタキシャルSi層6が設けられた構造からなる半導体層が素子分離領域のシリコン窒化膜4により絶縁分離されている。Si層6の残りの周囲には第1のゲート酸化膜10を介して包囲型フローティングゲート電極11が設けられ、包囲型フローティングゲート電極11の周囲には第2のゲート酸化膜12を介して包囲型コントロールゲート電極13(ワード線)が設けられ、Si層5には概略ソースドレイン領域9が設けられている2重包囲型ゲート電極を有するMIS電界効果トランジスタより構成したフラッシュメモリー。

(もっと読む)

バッファ付きフィンFETデバイス

【課題】フィンFETデバイスのロバストネスを向上させる。

【解決手段】トランジスタデバイスであって、半導体基板と、半導体基板に形成されたバッファ付き垂直フィン状構造であって、垂直フィン状構造は、ドレーン領域とソース領域512との間にチャンネル領域514を含む上位の半導体層と、上位の半導体層の下のバッファ領域304であって、第1のドーピング極性を有するバッファ領域と、第1のドーピング極性と反対である第2のドーピング極性を有するウェル領域302の少なくとも一部分と、バッファ領域とウェル領域との間の少なくとも1つのp−n接合であって、該垂直フィン状構造の水平断面を少なくとも部分的にカバーする少なくとも1つのp−n接合とを含むバッファ付き垂直フィン状構造と、上位の半導体層のチャンネル領域をおおい形成されたゲートスタックとを備えている。

(もっと読む)

固体撮像装置及びその製造方法、電子機器

【課題】画素分離部の幅を縮小することや光電変換部の面積の拡大することを可能にする固体撮像装置を提供する。

【解決手段】第1導電型の電荷蓄積領域23を含む光電変換部及び画素トランジスタTr1から成る画素38と、画素38が複数配列された画素領域と、この画素領域内の隣接する画素38間の半導体層22に設けられたトレンチ42の内壁部に形成された、エピタキシャル成長による第1導電型の半導体層43と、この第1導電型の半導体層43の内部に形成され、隣接する画素38の電荷蓄積領域23を分離する、画素分離部41とを含んで、固体撮像装置21を構成する。

(もっと読む)

固体撮像装置および固体撮像装置の製造方法

【課題】本発明の一つの実施形態の目的は、素子分離特性を向上可能な固体撮像装置および固体撮像装置の製造方法を提供することである。

【解決手段】実施形態によれば、固体撮像装置の製造方法が提供される。固体撮像装置の製造方法は、素子分離領域形成工程と、電荷蓄積領域形成工程とを含む。素子分離領域形成工程では、第1導電型の半導体層をエピタキシャル成長させて光電変換素子間を分離する素子分離領域を形成する。電荷蓄積領域形成工程では、第2導電型の半導体層をエピタキシャル成長させて前記光電変換素子における電荷蓄積領域を形成する。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、シリコンエピタキシャル層に結晶欠陥が生じ易いという問題がある。

【解決手段】半導体装置1は、シリコン基板10、歪み付与層20、シリコン層30、FET40、および素子分離領域50を備えている。シリコン基板10上には、歪み付与層20が設けられている。歪み付与層20上には、シリコン層30が設けられている。歪み付与層20は、シリコン層30中のFET40のチャネル部に格子歪みを生じさせる。シリコン層30中には、FET40が設けられている。FET40は、ソース・ドレイン領域42、SD extension領域43、ゲート電極44およびサイドウォール46を含んでいる。ソース・ドレイン領域42と上述の歪み付与層20とは、互いに離間している。FET40の周囲には、素子分離領域50が設けられている。素子分離領域50は、シリコン層30を貫通して歪み付与層20まで達している。

(もっと読む)

半導体装置の製造方法およびCMOSイメージセンサーの製造方法

【課題】 半導体装置に発生するノイズを低減する

【解決手段】 シリコン基板100の第1部分110を覆い、シリコン基板100の第1部分110に隣接する第2部分120を覆わない窒化シリコン膜200をマスクとしてシリコン基板100を熱酸化することにより、酸化シリコン膜300を形成する。窒化シリコン膜200をマスクとして酸化シリコン膜300のバーズビーク部310の下へ斜めイオン注入を行うことにより、不純物領域121を形成する。

(もっと読む)

半導体の製造方法及び半導体装置

【課題】複雑な工程を経ることなく、通常の半導体製造装置を使用して、低コストで、半導体装置の、低電圧動作、高集積性を実現する。

【解決手段】次の工程(1)〜(5)で半導体装置を製造する。(1)シリコン結晶製の半導体支持基板の表面を洗浄し、酸化被膜を除去して、結晶面を露出させる工程、(2)該結晶面上に高誘電率非晶質薄膜を低温で堆積する工程、(3)該高誘電率非晶質薄膜の結晶化開始温度よりも低いプレアニール温度で該高誘電率非晶質薄膜をプレアニールする工程、(4)該半導体支持基板を選択的に急速加熱することにより該高誘電率非晶質薄膜内部に基板界面から該薄膜表面方向に向けて温度が低くなる急峻な温度勾配を形成することにより該高誘電率非晶質薄膜を結晶化して、エピタキシャル薄膜を形成する工程、(5)該エピタキシャル薄膜の上面に半導体結晶の配向膜を形成する工程を有する。

(もっと読む)

半導体装置

【課題】半導体基板上へのVFETと他の種類の素子との混載が可能でありながら、半導体基板上に積層される半導体層の表面に大きな段差を有しない半導体装置を提供する。

【解決手段】P型シリコン基板2上には、酸化シリコンからなるボックス層3、N+型横方向導電層4およびN−型表面層5が積層されている。ボックス層3上には、N−型表面層5の表面からボックス層3に至る深さを有する、平面視環状のディープトレンチ6が形成されている。ディープトレンチ6およびボックス層3に取り囲まれるトランジスタ形成領域8は、その周囲から分離されている。このトランジスタ形成領域8において、N−型表面層5の表層部には、ソース領域14およびドレイン領域16が形成されている。またディープトレンチ6の側面に沿って、ドレイン領域16とN+型横方向導電層4とに接続されたN+型縦方向導電層17が形成されている。

(もっと読む)

半導体装置

【課題】基板を介したクロストークを抑制でき、放熱性が高い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置1は、半導体基板10を備える。前記半導体基板の内部には空洞11が形成されている。また、前記半導体基板の内部には、前記空洞を前記半導体基板の上面に連通させる連通孔12も形成されている。前記半導体装置は、さらに、前記空洞及び前記連通孔の内面上に設けられた絶縁膜13と、前記空洞及び前記連通孔の内部に埋め込まれ、熱伝導率が前記絶縁膜の熱伝導率よりも高い伝熱部材14と、前記半導体基板における前記空洞の直上域に形成された素子21,22と、を備える。

(もっと読む)

半導体装置及びその製造方法、並びにSOI基板及びその製造方法

【課題】コンタクトホールの形成領域が素子分離領域と重複しても、素子特性の劣化を抑制できるSOI基板とこのSOI基板を用いた半導体装置とを提供する。

【解決手段】半導体装置1は、半導体基材11と埋め込み絶縁膜12と半導体層16とを有するSOI基板と、このSOI基板上に形成された半導体素子構造とを備える。埋め込み絶縁膜12は、半導体基材11から半導体層16を電気的に絶縁分離する機能を有し、窒化膜14を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】DRAMの微細化及び高集積化により、プロセス低温化が進み、400〜500℃熱処理による基板内の酸素ドナー化による電子発生量が多くなってきた。そのため、基板深くに形成されるウェル同士の分離耐圧が厳しくなり、デバイス劣化を引き起こしてしまう。

【解決手段】P型半導体基板11の表面から0.2〜1μmの範囲の深さに2E+17atom/cm3以上のピーク濃度を有するNウェル層12の下方に、P型半導体基板11中に発生するキャリア電子濃度より高濃度のP型不純物を含有する空乏層拡大防止層17を有する半導体装置。

(もっと読む)

埋め込みドープ層を有する完全空乏型SOIデバイス

【課題】完全空乏型SOIデバイスの製造に適したセミコンダクタオンインシュレータ(SeOI)ウェーハおよびそれを用いたデバイスを提供すること。

【解決手段】本発明は、第1の基板の表面領域にドープ層、ドープ層上に埋め込み酸化物層、埋め込み酸化物層上に半導体層を形成してSeOIウェーハを得る。SeOIウェーハの第2の領域の埋め込み酸化物層および半導体層を維持しながらSeOIウェーハの第1の領域から埋め込み酸化物層および半導体層を除去し、第2の領域に上部トランジスタを形成する。第1の領域にリセスチャネルアレイトランジスタを形成し、第2の領域にpチャネルトランジスタおよび/またはnチャネルトランジスタを形成する。ドープ層内またはこの近傍にバックゲートを形成し、第1の領域にリセスチャネルアレイトランジスタを形成し、ドープ層内またはその近傍にソース領域およびドレイン領域を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】包囲型ゲート電極付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に設けられた第1の半導体層5間に、第2の絶縁膜3が設けられていない部分上に設けられた第2の半導体層6が挟まれた構造からなる半導体層が島状に絶縁分離されて設けられ、第2の半導体層6の周囲にはゲート絶縁膜12を介して包囲型ゲート電極13が設けられ、第1の半導体層5には概略高濃度ソースドレイン領域(8、11)及び低濃度ソースドレイン領域(9、10)が設けられ、第2の半導体層6には概略チャネル領域が設けられ、高濃度のソースドレイン領域(8、11)及び包囲型ゲート電極13には配線体(17、18、20、21)が接続されているMISFET。

(もっと読む)

半導体装置の製造方法

【課題】SON構造の半導体装置において、フォトリソグラフィー工程で高精度の位置合わせができ、プロセスラインの汚染を防止することができて、素子特性の劣化が防止され、信頼性の高い半導体装置の製造方法を提供する。

【解決手段】SON構造9上部のシリコン層32の段差18をアライメントマーク20として用いることによって、アライメントマーク20の形状崩れが防止されて、フォトリソグラフィー工程で高精度の位置合わせができるようになる。また、段差18が小さいためにフォトリソグラフィー工程で凹部へのレジストの残留やプロセス途中で発生するゴミの残留が防止され、プロセスラインの汚染が防止できる。その結果、素子特性の劣化が防止され、信頼性の高い半導体装置の製造方法を提供することができる。

(もっと読む)

半導体装置

【課題】同一基板上に混載された他の素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体装置は、p形半導体層12と、n形のソース領域13と、絶縁体23と、n形半導体領域20と、n形のドレイン領域14と、p形のチャネル領域12aと、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、電極21とを備える。前記絶縁体は、前記p形半導体層の表面から前記p形半導体層の厚み方向に延びて形成されたトレンチt1内に設けられている。前記n形半導体領域は、前記ドレイン領域と前記絶縁体との間の前記p形半導体層の表面に設けられる。前記電極は、前記n形半導体領域に接続される。

(もっと読む)

エッチングで形成された溝を用いて厚い誘電体領域を形成する方法

【課題】エピタキシアル沈着工程だけを用いて製造される縁部端子領域を有する高電圧半導体ディバイスを提供すること。

【解決手段】半導体ディバイスの製造方法は相互に対向する第1及び第2の主表面を有する半導体基板を設けることを含む。この方法は、上記の半導体基板に少なくとも1つの溝と、第1メサおよび第2メサとを設けることを含む。この方法は、また、各溝の両側壁と底部とを酸化し、ドープされた酸化物を各溝ならびに第1および第2メサの頂部に沈着させて、沈着せられた酸化物が流動して、各第1メサのシリコンが完全に二酸化ケイ素に変換し、各第2メサのシリコンが部分的にのみ二酸化ケイ素に変換し、各溝には酸化物が充填される温度で、半導体基板を熱酸化させることを含む。

(もっと読む)

半導体装置の製造方法

【目的】SON構造上に素子を形成する場合や繰り返しのエピタキシャル成長で素子を形成する場合に正確な位置あわせをすることができる半導体装置の製造方法を提供すること。

【解決手段】シリコンウェハ1のダイシングライン4などの無効領域の内部にSON構造11のアライメントマーク9を形成し、このアライメントマーク9を赤色レーザ(透過型レーザ)の反射光16の変化で認識することで、図示しないSON構造23上に素子を形成する場合や繰り返しのエピタキシャル成長で素子を形成する場合に正確な位置合わせをすることができる。

(もっと読む)

1 - 20 / 264

[ Back to top ]