Fターム[5F032AA77]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 溝内埋込み分離 (7,414) | 埋込みに工夫 (1,675) | 溝内への選択的埋込み (1,094) | 研磨、ポリッシュ (827)

Fターム[5F032AA77]に分類される特許

1 - 20 / 827

半導体装置の製造方法

【課題】半導体基板をエッチングする際、ハードマスクの肩落ちによるエッチング深さの基板面内での粗密差を低減する。

【解決手段】半導体基板1上に、絶縁層(10,11)とアッシング除去可能な材料層を形成する工程と、材料層をパターニングする工程と、パターニングされた材料層をマスクに、絶縁層を貫通し、少なくとも半導体基板の一部をエッチングする第1のエッチング工程と、材料層がなくなる前にエッチングを一旦停止し、残存する材料層(12)をアッシング除去する工程と、絶縁層をマスクに半導体基板を所定の深さにエッチングする第2のエッチング工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置

【課題】バルク半導体基板上に形成されるトンネルトランジスタ同士を電気的に分離することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板内に形成された第1および第2の素子分離絶縁膜とを備える。さらに、前記装置は、前記第1および第2の素子分離絶縁膜間の前記半導体基板上に、ゲート絶縁膜を介して形成されたゲート電極を備える。さらに、前記装置は、前記半導体基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域を備える。さらに、前記装置は、前記半導体基板内に前記第1および第2の素子分離絶縁膜に接するように形成され、前記第1および第2の主端子領域の下面よりも深い位置に上面を有する、前記第2導電型の第1の拡散層を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、2つの埋め込みゲート用の溝部8a,8bによって分断された3つの活性領域6a,6b,6cのうち、中央部に位置する活性領域6bを分断するビットコンタクト用の溝部11の両側面に、埋め込みゲート用の溝部8a,8bの底面と同程度の深さで不純物を拡散させることによって形成された第1の不純物拡散層13a,13bと、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SOIウェハに高耐圧素子の領域と低耐圧素子の領域とが形成された半導体装置であって、製造工程の中で、作業ステージに静電吸着したり、異常放電を引き起こしたりすることを抑えることができる半導体装置を提供する。

【解決手段】半導体層2と、半導体層2の上に形成された絶縁層3と、絶縁層3の上に形成された半導体の第1領域10aと、絶縁層3の上に形成され、第1領域10aに隣接する半導体の第2領域20と、絶縁層3の上に形成され、第1領域10aの側面を覆うように取り囲み、第1領域10aと第2領域20とが直接接続するように開口された開口部31aを有する絶縁体の第1絶縁壁30aとを具備する。

(もっと読む)

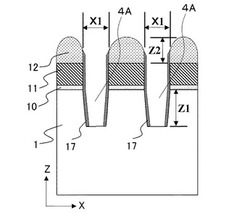

バッファ付きフィンFETデバイス

【課題】フィンFETデバイスのロバストネスを向上させる。

【解決手段】トランジスタデバイスであって、半導体基板と、半導体基板に形成されたバッファ付き垂直フィン状構造であって、垂直フィン状構造は、ドレーン領域とソース領域512との間にチャンネル領域514を含む上位の半導体層と、上位の半導体層の下のバッファ領域304であって、第1のドーピング極性を有するバッファ領域と、第1のドーピング極性と反対である第2のドーピング極性を有するウェル領域302の少なくとも一部分と、バッファ領域とウェル領域との間の少なくとも1つのp−n接合であって、該垂直フィン状構造の水平断面を少なくとも部分的にカバーする少なくとも1つのp−n接合とを含むバッファ付き垂直フィン状構造と、上位の半導体層のチャンネル領域をおおい形成されたゲートスタックとを備えている。

(もっと読む)

集積回路装置及びその製造方法

【課題】FinFETの特性が均一な集積回路装置及びその製造方法を提供する。

【解決手段】実施形態に係る集積回路装置は、半導体基板の上面に形成され、第1方向に延びる複数本のフィンと、前記フィン間に配置された素子分離絶縁膜と、前記第1方向に対して交差した第2方向に延び、前記素子分離絶縁膜上に設けられたゲート電極と、前記フィンを前記ゲート電極から絶縁する絶縁膜と、を備える。そして、連続して配列された複数本の前記フィンが配置された第1領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも下方の第1の位置に位置し、前記第1領域から見て前記第2方向に位置する第2領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも上方の第2の位置に位置する。また、前記第2領域においては、前記素子分離絶縁膜が前記フィンの側面の全体を覆っている。

(もっと読む)

半導体装置の製造方法

【課題】アモルファスカーボン膜などの酸化によりパターン精度が劣化する材料からなるハードマスク膜上に保護膜とマスク膜の積層膜を形成し、マスク膜をダブルパターニング技術を用いてパターニングすると、保護膜も2回のエッチングに曝されて、保護膜としての機能が損なわれ、パターニングに使用する有機膜除去のアッシングの際に、ハードマスク膜が酸化されてパターン精度が劣化し、忠実なパターン転写ができなくなる。

【解決手段】マスク膜6の2回目のエッチングの際に、パターニングに用いる有機膜(反射防止膜7b、8b)をマスク膜6表面は露出するが、保護膜5表面は露出しないようにエッチングし、マスク膜6のみを選択的にパターニングすることで、その後の残存する有機膜のアッシング除去に際して、ハードマスク膜4を酸化から保護する保護膜5の機能を確保でき、パターン転写の忠実性を確保できる。

(もっと読む)

半導体装置及びその製造方法

【課題】 対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和する。

【解決手段】 半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する半導体装置。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】ランプアニールによるレイアウトに起因した温度バラつきを低減する。

【解決手段】この半導体装置10は、基板100と、基板100に埋め込まれた素子分離領域200と、基板100のうち、素子分離領域200の無い領域に形成された不純物層(エクステンション領域322、ソース領域324、エクステンション領域342、及びドレイン領域344)と、を備える。この素子分離領域200は、たとえば、波長300nm以上890nm以下においてSiO2よりも光吸収係数が大きい材料から形成されている光吸収層220を含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させ、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板1の主面に酸化膜として絶縁膜2を形成し、絶縁膜2上に窒化シリコン膜を形成してから、素子分離用の溝4aをプラズマドライエッチングにより形成し、溝4aを埋めるように酸化シリコンからなる絶縁膜6をHDP−CVD法で形成し、CMP処理により溝4aの外部の絶縁膜6を除去し、溝4a内に絶縁膜6を残す。それから、窒化シリコン膜を除去する。その後、絶縁膜2をウェットエッチングで除去して半導体基板1を露出させるが、この際、半導体基板1の主面に140ルクス以上の光を当てながら絶縁膜2をウェットエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】DHF処理後に実施されるHPM処理またはAPM処理を、良好に行うことができる半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、槽内に水を導入して、槽内から希フッ酸を排出する工程と、槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、槽内に、H2O2と、上記水よりも温度の高い温水とを導入する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

半導体基板、その製造方法及び半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した半導体層が1つの絶縁膜上に設けられた半導体基板、その製造方法及び半導体装置を提供する。

【解決手段】実施形態に係る半導体基板は、第1絶縁層と、前記第1絶縁層の上に設けられた第1半導体層と、前記第1半導体層の上に選択的に設けられた第2絶縁層と、前記第2絶縁層を介して前記第1半導体層の上に設けられた第2半導体層と、を備える。さらに、前記第1半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記第1半導体層における前記第1絶縁層と前記第2絶縁層との間の部分と、前記第1半導体層の残りの部分と、を電気的に分離した第3絶縁層を備える。

(もっと読む)

半導体基板およびその製造方法、その半導体基板を用いた半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した厚さを有する半導体層が1つの絶縁膜上に設けられた半導体基板およびその製造方法、その半導体基板を用いた半導体装置を提供する。

【解決手段】実施形態に係る半導体基板10は、第1絶縁層5と、前記第1絶縁層の上に設けられた半導体層7とを有する半導体基板であって、前記半導体層の中に選択的に設けられ、前記半導体層の表面に平行に延在し、その延在方向の長さが前記第1絶縁層よりも短い第2絶縁層13と、前記半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記半導体層の前記第2絶縁層を含む部分と、前記半導体層の残りの部分と、を電気的に分離する第3絶縁層15と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させる。

【解決手段】シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させ、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成し、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。

(もっと読む)

半導体装置およびその製造方法

【課題】ワードライン間の素子分離を行い、メモリセルの微細化が可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10内に形成されたビットライン14と、ビットライン14上にビットライン14の長手方向に連続して設けられた絶縁膜ライン18と、ビットライン14間の半導体基板10上に設けられたゲート電極16と、ゲート電極16上に接して設けられ、ビットライン14の幅方向に延在したワードライン20と、ビットライン14間でありワードライン20間の半導体基板に形成されたトレンチ部22と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜に劣化が生じることを抑制する。

【解決手段】ハードマスクを用いて素子分離溝102を形成した後、素子分離溝102に素子分離膜20を埋め込む。次いで、ハードマスクの窒化シリコン膜210を除去する。次いで、ハードマスクの表面酸化膜200を薄くする。その後、シリコン基板100を熱酸化することにより、表面酸化膜を厚くして再酸化膜202を形成する。次いで、第1素子形成領域101及び第2素子形成領域103に位置するシリコン基板に、再酸化膜202を介してチャネル不純物を注入する。次いで、再酸化膜202を除去する。次いで、第1素子形成領域101に位置するシリコン基板100に、ゲート絶縁膜110及びゲート電極120を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】信頼性の高い半導体装置を実現する。

【解決手段】半導体装置100は、基板30と、基板30に埋め込まれた絶縁膜20と、絶縁膜20上に形成された複数の抵抗素子10と、を備えている。基板30は、複数の抵抗素子10を有する抵抗素子形成領域40において複数の凸部32を有している。複数の凸部32は、絶縁膜20に入り込んでおり、かつ上端が絶縁膜20の表面よりも低い。このため、信頼性の高い半導体装置を実現することが可能となる。

(もっと読む)

1 - 20 / 827

[ Back to top ]