Fターム[5F032DA22]の内容

Fターム[5F032DA22]の下位に属するFターム

ドライエッチング (915)

ウェットエッチング (802)

異方性エッチング(トレンチ用、V溝用) (510)

等方性エッチング (142)

サイドエッチング (80)

エッチングレートの相違を利用した選択エッチング (381)

側壁部を残すエッチング (146)

Fターム[5F032DA22]に分類される特許

1 - 20 / 465

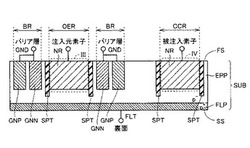

半導体装置

【課題】注入元素子から被注入素子への電子の移動を抑制する効果が高く、素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】第1および第2の主表面を有する半導体基板SUB内にはエピタキシャル層EPPと、n型不純物領域NRを含む注入元素子と、注入元素子と間隔を隔てて形成された被注入素子と、注入元素子と被注入素子との間の領域の少なくとも一部に形成され、注入元素子と被注入素子とを結ぶ方向に対して交差する方向に延在する接地電位が印加されたn型領域GNNおよびp型領域GPPを有するバリア層BRとを備える。さらに半導体基板SUB内でエピタキシャル層EPPに接するように形成されたフローティングp型裏面領域FLPを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】低耐圧トランジスタ特性への影響なく、耐圧特性および動作特性が安定した高耐圧素子を組み込む。

【解決手段】同一の半導体基板2上に、トレンチ分離絶縁膜(プラズマ酸化膜6)によって素子分離された高耐圧素子20aと低耐圧素子20bを設けた半導体装置1において、高耐圧素子形成領域におけるトレンチ分離絶縁膜(プラズマ酸化膜6)の表面高さが低耐圧素子形成領域におけるトレンチ分離絶縁膜(プラズマ酸化膜6)の表面高さよりも低く形成されている。高耐圧素子形成領域におけるトレンチ分離絶縁膜(プラズマ酸化膜6)の表面高さが、高耐圧素子20aのチャネルを形成する半導体基板2の表面に対して−10〜60nm(より好ましくは−10〜30nm)だけ高くなるように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】エッチングによるマスク窒化膜除去時に、STI構造を構成しているライナー膜に劣化が発生することを防止する。

【解決手段】半導体基板に形成したトレンチ内に素子分離構造を形成する工程を含み、前記素子分離構造を形成する工程は、前記トレンチ内の前記半導体基板上にパッド酸化膜を形成する工程と、前記パッド酸化膜上にALD法によりライナー膜を形成する工程と、前記ライナー膜上にSOD膜を形成する工程と、を含む半導体装置の製造方法。ライナー膜は酸化ハフニウム膜が好ましい。

(もっと読む)

半導体装置の製造方法

【課題】素子分離用の大きなエアギャップを容易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】一の実施形態による半導体装置の製造方法では、基板内に素子分離溝を形成し、前記素子分離溝の側壁面にアモルファス層を形成する。さらに、前記方法では、前記素子分離溝内に前記アモルファス層を介して犠牲膜を形成し、前記犠牲膜上にエアギャップ膜を形成する。さらに、前記方法では、前記エアギャップ膜の形成後に前記犠牲膜を除去することで、前記エアギャップ膜の下部の前記素子分離溝内にエアギャップを形成する。

(もっと読む)

不揮発性メモリ装置の製造方法

【課題】不揮発性メモリ装置の製造方法を提供する。

【解決手段】基板10上に第1絶縁膜11及び第1導電膜12を形成するステップと、第1領域Cの第1導電膜12、第1絶縁膜11及び基板10をエッチングして、第1素子分離トレンチを形成するステップと、第1素子分離トレンチに埋め立てられる第1素子分離膜を形成するステップと、第2絶縁膜16及び導電性のキャップ膜17を形成するステップと、第2領域Pのキャップ膜17及び第2絶縁膜16をエッチングするステップと、第2導電膜19を形成するステップと、第1領域Cの第2導電膜19、キャップ膜17、第2絶縁膜16、第1導電膜12及び第1絶縁膜11を選択的にエッチングして、第1ゲートパターンを形成しながら、第2領域Pの第2導電膜19、第1導電膜12、第1絶縁膜11及び基板10を選択的にエッチングして、第2領域Pに第2素子分離トレンチT2、T3を形成するステップとを含む。

(もっと読む)

半導体装置

【課題】素子分離すべき領域にダミーの補助ゲートを配置することで、電気的に分離する方法(FS方式)を採用しつつ、補助ゲートに給電するための新たな専用の配線を設けることによるチップの縮小化の弊害を解消する半導体装置を提供する。

【解決手段】半導体基板2に埋め込み形成された素子分離膜によって、複数のセル部活性領域が区画された半導体装置1であって、半導体基板2に設けられたゲート溝内に、ゲート絶縁膜を介して形成された補助セルゲート28aが、半導体基板2と電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】素子の特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板上の一部の領域にマスク膜を形成する工程と、前記マスク膜を形成した領域及び前記マスク膜を形成していない領域の双方において、前記半導体基板の上方に、マスク部材を形成する工程と、前記マスク部材をマスクとしてエッチングを施すことにより、前記マスク膜及び前記半導体基板の上層部分をパターニングする工程と、前記パターニングされたマスク膜をマスクとしてエッチングを施すことにより、前記パターニングされた半導体基板の上層部分の一部を除去する工程と、を備える。

(もっと読む)

誘電体分離基板および半導体装置

【課題】深い不純物拡散層の形成が容易な誘電体分離基板および半導体装置を提供する。

【解決手段】誘電体分離基板10では、半導体基板11に第1の厚さt1を有する絶縁膜12が設けられている。絶縁膜12上に第2の厚さt2を有する第1導電型の半導体層13が設けられている。半導体層13の下部に絶縁膜12に接して第2導電型の不純物拡散層14が部分的に設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜の膜厚が異なる複数のトランジスタを有する半導体装置において、オフリークの増加を抑制する。

【解決手段】半導体装置は、半導体層上に形成された第1MISトランジスタ及び第2MISトランジスタを備える。第1MISトランジスタは、活性領域101が素子分離膜102に囲まれた第1活性領域と、第1活性領域上に第1ゲート絶縁膜111を介して形成された第1ゲート電極104とを有する。第2MISトランジスタは、活性領域101が素子分離膜102に囲まれた第2活性領域と、第2活性領域上に第2ゲート絶縁膜103を介して形成された第2ゲート電極104とを有する。第2ゲート絶縁膜103は、第1ゲート絶縁膜111よりも薄い。第2MISトランジスタは、少なくとも第2ゲート電極104の下方において、第2活性領域と素子分離膜102との境界部上に、素子分離膜102の側面を覆う保護絶縁膜108を有する。

(もっと読む)

固体撮像装置及びその製造方法、電子機器

【課題】画素分離部の幅を縮小することや光電変換部の面積の拡大することを可能にする固体撮像装置を提供する。

【解決手段】第1導電型の電荷蓄積領域23を含む光電変換部及び画素トランジスタTr1から成る画素38と、画素38が複数配列された画素領域と、この画素領域内の隣接する画素38間の半導体層22に設けられたトレンチ42の内壁部に形成された、エピタキシャル成長による第1導電型の半導体層43と、この第1導電型の半導体層43の内部に形成され、隣接する画素38の電荷蓄積領域23を分離する、画素分離部41とを含んで、固体撮像装置21を構成する。

(もっと読む)

半導体装置の製造方法

【課題】DHF処理後に実施されるHPM処理またはAPM処理を、良好に行うことができる半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、槽内に水を導入して、槽内から希フッ酸を排出する工程と、槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、槽内に、H2O2と、上記水よりも温度の高い温水とを導入する工程とを有する。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】大面積のアクティブ面積を有するSOI基板を製造する。

【解決手段】Siを含む基板の一つの面の一部の上方に、SiGeを含む第1の層と、Siを含む第2の層とを基板側からこの順に配置する積層部を形成する工程(a)と、積層部の上方と基板の積層部が形成された領域とは異なる領域の上方とにまたがる第3の層を形成する工程(b)と、積層部の上方に位置する第3の層及び第2の層の各一部をエッチングすることにより、第1の層の一部を露出させる工程(c)と、工程(c)において露出した第1の層を、基板の第1の面に沿った方向にエッチングする工程(d)と、工程(c)においてエッチングされた第2の層を、基板の第1の面に沿った方向にエピタキシャル成長させる工程(e)と、積層部が形成された領域の基板と、第2の層との間にSiO2を含む第4の層を形成する工程(f)と、を含む。

(もっと読む)

半導体装置

【課題】微細化が可能であるメモリセル構造を備える半導体装置を提供する。

【解決手段】ワード線と、ビット線と、電源ノードと、ビット線と電源ノードとの間にPN結合を成す第1及び第2の領域並びに第2の領域とPN結合を成す第3の領域を少なくとも有するメモリ素子と、メモリ素子の第2の領域とは独立して設けられてメモリ素子の第2の領域と電気的に接続された第1の電極及び前記ワード線に接続された第2の電極を有するキャパシタと、を備える。

(もっと読む)

半導体装置の製造方法

【課題】高アスペクト比の要求される溝内に緻密な膜質の酸化シリコン膜を形成した素子分離領域を提供する。

【解決手段】半導体基板上にマスク窒化膜3をマスクに素子分離溝4Aを形成し、ライナー窒化膜形成後、気相法により流動性シラザン化合物膜7を溝4Aの上方でマスク窒化膜3の上面より高くなるように形成した後、酸化性雰囲気下で熱処理して第一の酸化シリコン膜8に変換すると同時に緻密化し、その後マスク窒化膜3上面まで平坦化する。

(もっと読む)

半導体装置およびその製造方法

【課題】ワードライン間の素子分離を行い、メモリセルの微細化が可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10内に形成されたビットライン14と、ビットライン14上にビットライン14の長手方向に連続して設けられた絶縁膜ライン18と、ビットライン14間の半導体基板10上に設けられたゲート電極16と、ゲート電極16上に接して設けられ、ビットライン14の幅方向に延在したワードライン20と、ビットライン14間でありワードライン20間の半導体基板に形成されたトレンチ部22と、を具備する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】信頼性の高い半導体装置を実現する。

【解決手段】半導体装置100は、基板30と、基板30に埋め込まれた絶縁膜20と、絶縁膜20上に形成された複数の抵抗素子10と、を備えている。基板30は、複数の抵抗素子10を有する抵抗素子形成領域40において複数の凸部32を有している。複数の凸部32は、絶縁膜20に入り込んでおり、かつ上端が絶縁膜20の表面よりも低い。このため、信頼性の高い半導体装置を実現することが可能となる。

(もっと読む)

半導体の製造方法及び半導体装置

【課題】複雑な工程を経ることなく、通常の半導体製造装置を使用して、低コストで、半導体装置の、低電圧動作、高集積性を実現する。

【解決手段】次の工程(1)〜(5)で半導体装置を製造する。(1)シリコン結晶製の半導体支持基板の表面を洗浄し、酸化被膜を除去して、結晶面を露出させる工程、(2)該結晶面上に高誘電率非晶質薄膜を低温で堆積する工程、(3)該高誘電率非晶質薄膜の結晶化開始温度よりも低いプレアニール温度で該高誘電率非晶質薄膜をプレアニールする工程、(4)該半導体支持基板を選択的に急速加熱することにより該高誘電率非晶質薄膜内部に基板界面から該薄膜表面方向に向けて温度が低くなる急峻な温度勾配を形成することにより該高誘電率非晶質薄膜を結晶化して、エピタキシャル薄膜を形成する工程、(5)該エピタキシャル薄膜の上面に半導体結晶の配向膜を形成する工程を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】異なる不純物濃度の埋め込み層を有する半導体装置を短時間かつ低コストで製造する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の表面に第1の酸化膜11を形成する第1の酸化膜形成ステップと、フォトダイオードが形成される第1の領域に形成された前記酸化膜の一部を除去して第1の間隔で第1の開口部を形成すると共に、トランジスタが形成される第2の領域に形成された前記酸化膜を除去して前記半導体基板の表面を露出させる第1の開口部12を形成ステップと、前記第1の酸化膜をマスクとして利用して前記第1の開口部及び前記第2の領域に対して第1の不純物を注入する第1の不純物注入ステップと、前記第1の不純物を熱拡散させる第1の熱拡散ステップと、を有する。

(もっと読む)

半導体装置

【課題】半導体基板上へのVFETと他の種類の素子との混載が可能でありながら、半導体基板上に積層される半導体層の表面に大きな段差を有しない半導体装置を提供する。

【解決手段】P型シリコン基板2上には、酸化シリコンからなるボックス層3、N+型横方向導電層4およびN−型表面層5が積層されている。ボックス層3上には、N−型表面層5の表面からボックス層3に至る深さを有する、平面視環状のディープトレンチ6が形成されている。ディープトレンチ6およびボックス層3に取り囲まれるトランジスタ形成領域8は、その周囲から分離されている。このトランジスタ形成領域8において、N−型表面層5の表層部には、ソース領域14およびドレイン領域16が形成されている。またディープトレンチ6の側面に沿って、ドレイン領域16とN+型横方向導電層4とに接続されたN+型縦方向導電層17が形成されている。

(もっと読む)

半導体装置

【課題】基板を介したクロストークを抑制でき、放熱性が高い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置1は、半導体基板10を備える。前記半導体基板の内部には空洞11が形成されている。また、前記半導体基板の内部には、前記空洞を前記半導体基板の上面に連通させる連通孔12も形成されている。前記半導体装置は、さらに、前記空洞及び前記連通孔の内面上に設けられた絶縁膜13と、前記空洞及び前記連通孔の内部に埋め込まれ、熱伝導率が前記絶縁膜の熱伝導率よりも高い伝熱部材14と、前記半導体基板における前記空洞の直上域に形成された素子21,22と、を備える。

(もっと読む)

1 - 20 / 465

[ Back to top ]