Fターム[5F032DA28]の内容

Fターム[5F032DA28]の下位に属するFターム

導電型・不純物濃度の相違の利用 (2)

Fターム[5F032DA28]に分類される特許

1 - 20 / 379

SOIウエハおよびSOIウエハの製造方法

【課題】除電構造と素子分離構造とを有するSOIウエハを、従来より少ない工程で製造することができるSOIウエハの製造方法の提供。

【解決手段】SOIウエハの周縁部分に活性層用半導体層および絶縁酸化膜を貫通する除電用トレンチをエッチングで形成すると同時に、当該周縁部分より内側の内側部分に上記活性層用半導体層を貫通し上記絶縁酸化膜に到達する素子分離用トレンチをエッチングで形成するトレンチ形成ステップを備え、上記トレンチ形成ステップは、上記周縁部分におけるエッチングレートが、上記内側部分におけるエッチングレートよりも高いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】SOI基板を使用せずバルク基板を用いてフィン型FETを製造すると、従来技術では素子領域と半導体基板との間の絶縁耐圧が低くなっていた。

【解決手段】本発明の半導体装置の製造方法では、素子分離膜の形成時にマスクとして用いる耐酸化用膜を、半導体基板表面に設ける溝部の底部から所定の距離まで離間した部分を除いて立設部の表面に形成することで、立設部の下部の素子分離膜がほぼ一定の膜厚にすることができた。このため、立設部と半導体基板との間の絶縁耐圧が向上し、リークもなく、信頼性が向上した。

(もっと読む)

半導体装置の製造方法

【課題】アモルファスカーボン膜などの酸化によりパターン精度が劣化する材料からなるハードマスク膜上に保護膜とマスク膜の積層膜を形成し、マスク膜をダブルパターニング技術を用いてパターニングすると、保護膜も2回のエッチングに曝されて、保護膜としての機能が損なわれ、パターニングに使用する有機膜除去のアッシングの際に、ハードマスク膜が酸化されてパターン精度が劣化し、忠実なパターン転写ができなくなる。

【解決手段】マスク膜6の2回目のエッチングの際に、パターニングに用いる有機膜(反射防止膜7b、8b)をマスク膜6表面は露出するが、保護膜5表面は露出しないようにエッチングし、マスク膜6のみを選択的にパターニングすることで、その後の残存する有機膜のアッシング除去に際して、ハードマスク膜4を酸化から保護する保護膜5の機能を確保でき、パターン転写の忠実性を確保できる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜の膜厚が異なる複数のトランジスタを有する半導体装置において、オフリークの増加を抑制する。

【解決手段】半導体装置は、半導体層上に形成された第1MISトランジスタ及び第2MISトランジスタを備える。第1MISトランジスタは、活性領域101が素子分離膜102に囲まれた第1活性領域と、第1活性領域上に第1ゲート絶縁膜111を介して形成された第1ゲート電極104とを有する。第2MISトランジスタは、活性領域101が素子分離膜102に囲まれた第2活性領域と、第2活性領域上に第2ゲート絶縁膜103を介して形成された第2ゲート電極104とを有する。第2ゲート絶縁膜103は、第1ゲート絶縁膜111よりも薄い。第2MISトランジスタは、少なくとも第2ゲート電極104の下方において、第2活性領域と素子分離膜102との境界部上に、素子分離膜102の側面を覆う保護絶縁膜108を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させ、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板1の主面に酸化膜として絶縁膜2を形成し、絶縁膜2上に窒化シリコン膜を形成してから、素子分離用の溝4aをプラズマドライエッチングにより形成し、溝4aを埋めるように酸化シリコンからなる絶縁膜6をHDP−CVD法で形成し、CMP処理により溝4aの外部の絶縁膜6を除去し、溝4a内に絶縁膜6を残す。それから、窒化シリコン膜を除去する。その後、絶縁膜2をウェットエッチングで除去して半導体基板1を露出させるが、この際、半導体基板1の主面に140ルクス以上の光を当てながら絶縁膜2をウェットエッチングする。

(もっと読む)

半導体装置およびその製造方法

【課題】ワードライン間の素子分離を行い、メモリセルの微細化が可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10内に形成されたビットライン14と、ビットライン14上にビットライン14の長手方向に連続して設けられた絶縁膜ライン18と、ビットライン14間の半導体基板10上に設けられたゲート電極16と、ゲート電極16上に接して設けられ、ビットライン14の幅方向に延在したワードライン20と、ビットライン14間でありワードライン20間の半導体基板に形成されたトレンチ部22と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル給電領域の面積を縮小して、半導体装置の微細化を行う。素子形成領域間のウェル電位のばらつきを抑制する。分離部の幅を細くする。

【解決手段】半導体装置は、半導体基板の表面に形成され、底部がウェル領域内に位置する溝状の分離部を有する。分離部は、ウェル領域と電気的に接続された導体配線と、底部に導体配線を埋め込む絶縁膜とを有する。分離部に囲まれるようにして区画されたウェル領域の一部は素子形成領域を形成し、素子形成領域には半導体素子が配置される。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体装置の製造方法

【課題】塗布法を用いて形成される酸化膜を溝の内部に充填した溝型の素子分離部を有する半導体装置において、溝の内部におけるボイドの発生を抑制して、埋め込み不良を低減することのできる技術を提供する。

【解決手段】0.2μm以下の溝幅を有する溝4Sの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも高く、かつ1.0μm以上の溝幅を有する溝4Lの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも低くなるように、半導体基板1の主面上にポリシラザン膜を形成し、続いて、300℃以上の熱処理を行うことにより、ポリシラザン膜を酸化シリコン(SiO2)からなる第1埋め込み膜8へ転化すると同時に、溝4Sの上部に局所的に生じたボイドを消滅させる。

(もっと読む)

半導体装置

【課題】SOI−MISFETにおいて、多結晶シリコンの残存による電気的な短絡、ゲート電極の寄生容量の増大を防止する。逆狭チャネル効果の抑制。

【解決手段】シリコン膜13を有するSOI基板上にゲート絶縁膜14、第1の多結晶シリコン膜15、ストッパー窒化膜(16)を順次堆積する。シリコン膜13、第1の多結晶シリコン膜15の側面に逆テーパー面(テーパー角θが鈍角)が形成されるようにエッチングして素子分離溝を形成する。STI埋め込み絶縁膜17を堆積し、CMPにより平坦化した後、等速性のRIEによりストッパー窒化膜(16)と絶縁膜17をエッチングして平坦な表面を得、その上に第2の多結晶シリコン膜18を堆積し(e)、積層多結晶シリコン膜をエッチングして積層ゲート電極(15、18)を形成する(f)。以下、ソース・ドレイン領域21、シリサイド膜22、層間絶縁膜23及びメタル配線24等を形成する(g)。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】信頼性の高いLocalSOI構造を有する基板を低コストで作製する。

【解決手段】第1の半導体からなる基板10上に、結晶成長により第2の半導体からなる層及び前記第1の半導体からなる層12を順次形成する半導体層形成工程と、前記第2の半導体からなる層をエッチングにより除去し開口領域13を形成する開口領域形成工程と、前記開口領域に、窒化物膜、炭化物膜又は酸化物膜を含む材料により形成される酸化遅延膜14を前記開口領域の入口における膜厚が所定の膜厚となるように成膜する酸化遅延膜成膜工程と、前記第1の半導体からなる基板及び前記第1の半導体からなる層の前記第1の半導体の一部を熱酸化することにより、前記開口領域に熱酸化膜15を形成する熱酸化工程とを有することを特徴とする、Local SOI半導体基板の製造方法。

(もっと読む)

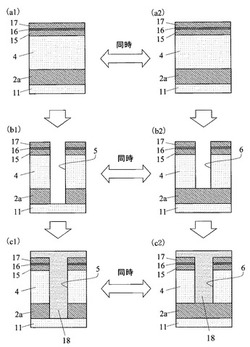

半導体装置及びその製造方法

【課題】包囲型ゲート電極付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に設けられた第1の半導体層5間に、第2の絶縁膜3が設けられていない部分上に設けられた第2の半導体層6が挟まれた構造からなる半導体層が島状に絶縁分離されて設けられ、第2の半導体層6の周囲にはゲート絶縁膜12を介して包囲型ゲート電極13が設けられ、第1の半導体層5には概略高濃度ソースドレイン領域(8、11)及び低濃度ソースドレイン領域(9、10)が設けられ、第2の半導体層6には概略チャネル領域が設けられ、高濃度のソースドレイン領域(8、11)及び包囲型ゲート電極13には配線体(17、18、20、21)が接続されているMISFET。

(もっと読む)

半導体装置の製造方法

【課題】レーザ光の照射を利用したエッチング加工による半導体装置の製造方法であって、複雑形状や深くて大きい除去領域等のエッチング加工が必要な広範囲の半導体装置の製造に適用可能で、高いエッチング速度が得られる半導体装置の製造方法を提供する。

【解決手段】単結晶シリコンからなる基板10に対して、焦点位置を移動させてレーザ光Lをパルス照射し、前記単結晶シリコンを部分的に多結晶化して、前記単結晶シリコン中に連続した改質層11を形成する改質層形成工程と、前記改質層11をエッチングして除去するエッチング工程と、を備える半導体装置の製造方法とする。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域となるSOI構造を有する半導体線条突出部の形状のばらつきを抑制し、トランジスタ特性のばらつきを減少することができる半導体装置を提供する。

【解決手段】半導体基板1の素子分離用の溝に埋込み絶縁膜が埋め込まれてなる素子分離領域2と、素子分離領域2によって区画されてなり、素子分離用の溝を区画する側壁面と半導体基板の1一面とを有し、かつ側壁面には埋込み絶縁膜に向けて突出した半導体線条突出部1aが素子分離用の溝に沿って設けられてなる活性領域Tと、半導体線条突出部1aを残して活性領域Tを分断するように設けられたゲート電極用のゲート溝3と、ゲート溝3の内面に形成されたゲート絶縁膜4と、ゲート溝3に埋め込まれたゲート電極5と、ゲート電極5のゲート長方向両側の活性領域Tにそれぞれ形成され、半導体線条突出部1aによって連結される不純物拡散領域7と、を具備してなることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】加工膜と非加工膜をRIE法で選択的に加工するときに、非加工膜の加工量を低減させる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層1,7,8の上に非加工膜14を形成する工程と、非加工膜14および下地層1,7,8に溝4を形成する工程と、溝内を埋め込むように加工膜5を形成する工程と、非加工膜14を露出させるように加工膜5を平坦化する工程とを備える。更に、加工膜5および非加工膜14の上に保護膜16を形成する工程と、RIE法を用いて、保護膜16をエッチングすると共に、加工膜5を選択的にエッチングして溝内の加工膜5を落とし込む工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】エッチング装置の経時変化や状態変化等によらずトレンチの深さのばらつきを低減することができる半導体装置の製造方法を得る。

【解決手段】まず、所望の深さよりも浅い深さを持つトレンチ16をSi基板10の主面に形成する。次に、トレンチ16の深さを測定する。トレンチ16の底面からSi基板10に酸素イオン18を注入する。この際に、測定したトレンチ16の深さと所望の深さの差に基づいて酸素イオン18の注入エネルギーを調整して、Si基板10の所望の深さに酸素イオン18が注入されるようにする。次に、熱処理を行って酸素イオン18を注入した位置にSiO2膜22を形成する。次に、SiO2膜22をエッチングストッパとして用いて、トレンチ16の底面からSi基板10を更にエッチングしてトレンチ24を形成する。その後、SiO2膜22を除去する。

(もっと読む)

半導体装置

【課題】半導体装置における素子形成領域エッジ部分の電界集中を抑制し、素子の消費電力低減を図る。

【解決手段】半導体装置は、シリコンを含む絶縁膜上に選択的に形成された厚さが35nm以下の半導体膜と、半導体膜の周囲に、半導体膜以上の厚みの酸化シリコン膜で絶縁膜上に形成された素子分離膜と、素子分離膜上及び半導体膜上に、素子分離膜及び半導体膜で構成される凹部に沿って平面図で直線状に形成されたゲート電極膜と、を有するため、半導体膜上面は、その周囲に設けられた酸化シリコン膜の上面よりも低く構成される。そのため、ゲート電極膜が半導体膜の側面の一部にまわりこんで形成されることはなく、従来のような電界集中の問題を抑制することができる。

(もっと読む)

半導体装置とその製造方法

【課題】下側半導体層と埋込み絶縁層と上側半導体層が積層した積層体を有する半導体装置の耐圧を向上させることを目的としている。

【解決手段】半導体装置10は、下側半導体層20と埋込み絶縁層30と上側半導体層40が積層したSOI基板50を有する。下側半導体層20の埋込み絶縁層30と接する面の一部に凹部66が形成されている。凹部66内の比誘電率は、下側半導体層20の比誘電率よりも低い。

(もっと読む)

1 - 20 / 379

[ Back to top ]