Fターム[5F032DA30]の内容

Fターム[5F032DA30]に分類される特許

1 - 20 / 146

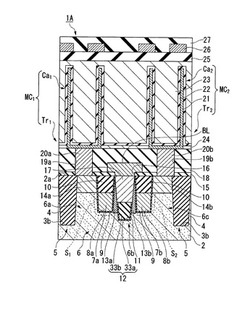

半導体装置及びその製造方法、並びにデータ処理システム

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、2つの埋め込みゲート用の溝部8a,8bによって分断された3つの活性領域6a,6b,6cのうち、中央部に位置する活性領域6bを分断するビットコンタクト用の溝部11の両側面に、埋め込みゲート用の溝部8a,8bの底面と同程度の深さで不純物を拡散させることによって形成された第1の不純物拡散層13a,13bと、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置の製造方法

【課題】SOI基板を使用せずバルク基板を用いてフィン型FETを製造すると、従来技術では素子領域と半導体基板との間の絶縁耐圧が低くなっていた。

【解決手段】本発明の半導体装置の製造方法では、素子分離膜の形成時にマスクとして用いる耐酸化用膜を、半導体基板表面に設ける溝部の底部から所定の距離まで離間した部分を除いて立設部の表面に形成することで、立設部の下部の素子分離膜がほぼ一定の膜厚にすることができた。このため、立設部と半導体基板との間の絶縁耐圧が向上し、リークもなく、信頼性が向上した。

(もっと読む)

半導体装置およびその製造方法

【課題】ワードライン間の素子分離を行い、メモリセルの微細化が可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10内に形成されたビットライン14と、ビットライン14上にビットライン14の長手方向に連続して設けられた絶縁膜ライン18と、ビットライン14間の半導体基板10上に設けられたゲート電極16と、ゲート電極16上に接して設けられ、ビットライン14の幅方向に延在したワードライン20と、ビットライン14間でありワードライン20間の半導体基板に形成されたトレンチ部22と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体装置

【課題】SOI−MISFETにおいて、多結晶シリコンの残存による電気的な短絡、ゲート電極の寄生容量の増大を防止する。逆狭チャネル効果の抑制。

【解決手段】シリコン膜13を有するSOI基板上にゲート絶縁膜14、第1の多結晶シリコン膜15、ストッパー窒化膜(16)を順次堆積する。シリコン膜13、第1の多結晶シリコン膜15の側面に逆テーパー面(テーパー角θが鈍角)が形成されるようにエッチングして素子分離溝を形成する。STI埋め込み絶縁膜17を堆積し、CMPにより平坦化した後、等速性のRIEによりストッパー窒化膜(16)と絶縁膜17をエッチングして平坦な表面を得、その上に第2の多結晶シリコン膜18を堆積し(e)、積層多結晶シリコン膜をエッチングして積層ゲート電極(15、18)を形成する(f)。以下、ソース・ドレイン領域21、シリサイド膜22、層間絶縁膜23及びメタル配線24等を形成する(g)。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルアレイおよび周辺回路領域の素子分離領域の深さを調節しつつ、周辺回路部の素子分離領域に形成されるマイクロトレンチ形状の影響を抑制し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板上に設けられデータを記憶する複数のメモリセルを含むメモリセルアレイと、半導体基板上に設けられメモリセルアレイを制御する周辺回路部とを備えている。素子分離部は、複数のメモリセルおよび周辺回路部が形成されるアクティブエリア間に設けられている。側壁膜は、周辺回路部におけるアクティブエリアの側面に設けられている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離溝を塗布系の材料で埋め込む素子分離構造において、熱処理時に素子分離溝に大きな応力が作用することを防止する。

【解決手段】メモリセル領域に形成され第1の開口幅を有する第1の素子分離溝と、周辺回路領域に形成され第1の開口幅より大きい第2の開口幅を有する第2の素子分離溝と、第1の素子分離溝の内面に形成された第1の酸化膜と、第1の酸化膜上に形成されて前記第1の素子分離溝内に埋め込まれた第1の塗布型酸化膜と、第2の素子分離溝の内面のうちの側部に形成された第2の酸化膜と、第2の素子分離溝内の内面のうちの底部上に形成された第3の酸化膜と、第3の酸化膜上に形成されて第2の素子分離溝内に埋め込まれた第2の塗布型酸化膜とを備えた。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】トレンチ2内に埋め込まれた第2の埋め込み絶縁膜4の一部が除去されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、浮遊ゲート電極6間が完全に埋め込まれないようにして制御ゲート電極8間にカバー絶縁膜10が掛け渡されることで、ビット線方向にDBに隣接する浮遊ゲート電極6間に空隙AG2が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域をライン上に形成することで、コンタクト領域のばらつきを抑制し、リセスゲート電極を用いて隣接するトランジスタ間の分離を行う構造を提供する。

【解決手段】半導体基板中に第1の方向に延在して形成される素子分離領域で分離された活性領域と、第1の方向と交差する第2の方向に延在し、素子分離領域及び活性領域に連通する溝内に形成されたリセスゲート電極と。リセスゲート電極で分断された活性領域であって、リセスゲート電極の底面より浅い領域に形成されるMOSトランジスタのソース/ドレイン領域とを備えた半導体装置であって、リセスゲート電極は、MOSトランジスタのゲート電極を構成する制御ゲート電極162tと、第1の方向に隣接するMOSトランジスタを素子分離する補助ゲート電極162iで構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】パワーデバイスの高耐圧とオン抵抗の低減とを同時に実現する。

【解決手段】実施形態に係わる半導体装置は、半導体基板101内のソース領域107A、ドレイン領域107B、及びドレイン領域107Bに接したドリフト領域105と、ソース領域107A及びドレイン領域107B間のドリフト領域105内のSTI絶縁層I−2と、STI絶縁層I−2上、ドリフト領域105上、並びに、ソース領域107A及びドレイン領域107B間のチャネル領域上のゲート電極110とを備える。STI絶縁層I−2は、第1及び第2のトレンチの内面上の第1の酸化膜102及び窒化膜103と、第1及び第2のトレンチを満たす窒化膜103上の第2の酸化膜104とを備える。第2のトレンチは、第1のトレンチ内に形成され、第1のトレンチの底面よりも低い底面を有し、第1のトレンチの幅よりも狭い幅を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域となるSOI構造を有する半導体線条突出部の形状のばらつきを抑制し、トランジスタ特性のばらつきを減少することができる半導体装置を提供する。

【解決手段】半導体基板1の素子分離用の溝に埋込み絶縁膜が埋め込まれてなる素子分離領域2と、素子分離領域2によって区画されてなり、素子分離用の溝を区画する側壁面と半導体基板の1一面とを有し、かつ側壁面には埋込み絶縁膜に向けて突出した半導体線条突出部1aが素子分離用の溝に沿って設けられてなる活性領域Tと、半導体線条突出部1aを残して活性領域Tを分断するように設けられたゲート電極用のゲート溝3と、ゲート溝3の内面に形成されたゲート絶縁膜4と、ゲート溝3に埋め込まれたゲート電極5と、ゲート電極5のゲート長方向両側の活性領域Tにそれぞれ形成され、半導体線条突出部1aによって連結される不純物拡散領域7と、を具備してなることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板上に形成されたメサ分離構造のMOSトランジスタのトランジスタ特性のバラツキを低減する。

【解決手段】MOSトランジスタは、埋込み酸化膜3上に形成されたメサ型SOI層5と、メサ型SOI層5の上面中央部の上に形成されたゲート酸化膜7と、メサ型SOI層5の上面端部の上にゲート酸化膜7よりも厚い膜厚で形成された第1シリコン酸化膜9と、メサ型SOI層5の側面に第2シリコン酸化膜11を介して形成されたシリコン窒化膜からなる側壁膜13と、ゲート酸化膜7上に形成されたゲート電極15を備えている。

(もっと読む)

半導体装置

【課題】SOI構造の単結晶半導体層(SiGe層/歪みSi層/SiGe層)上のMISFETの提供

【解決手段】半導体基板1に選択的に設けられた第1のトレンチの下部側面及び底面に絶縁膜3が設けられ、側面絶縁膜3間の底面絶縁膜3上に空孔4が設けられ、空孔4及び側面絶縁膜3上には単結晶半導体層が設けられ、半導体層は絶縁膜2が埋め込まれた第2のトレンチにより、島状に絶縁分離され、歪みSi層6直上にはゲート酸化膜11を介してゲート電極12が設けられ、半導体層には、ゲート電極12に自己整合してn型ソースドレイン領域(8、9)が、ゲート電極12の側壁のサイドウォール13に自己整合して、n+型ソースドレイン領域(7、10)がそれぞれ設けられ、ゲート電極12(配線図示せず)及びn+型ソースドレイン領域にはバリアメタル16を有する導電プラグ17を介してバリアメタル19を有する配線20が接続されているMISFET。

(もっと読む)

半導体装置及びその製作方法

【課題】半導体記憶装置に適するトランジスタ構造及びその製作方法の提供。

【解決手段】デュアルチャネルトランジスタ50は、少なくとも、第一方向に沿って伸展する第一STI(シャロートレンチアイソレーション)と第二方向に沿って伸展する第二STIにより分離され、第一STIと第二STIが交差する半導体アイランド22と、第二方向に沿って伸展し、半導体アイランドの表面から内側に向かって凹んだゲートトレンチ26と、第二方向に沿って伸展し、ゲートトレンチ内に設けられたゲート30と、第二方向に沿って設けられ、半導体アイランドの上面に設けられた第一ソース/ドレイン領域と、第一ソース/ドレイン領域の間に設けられた第一U字型チャネル領域60と、第二方向に沿って設けられ、半導体アイランドの上面に設けられた第二ソース/ドレイン領域と、第二ソース/ドレイン領域の間に設けられた第二U字型チャネル領域62とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ストレスライナー膜によるチャネル領域の効果的な歪みによりキャリア移動度が向上した半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、素子分離パターンを有する溝12を有する半導体基板2と、溝2の側面上に形成された側壁10と、半導体基板2の溝12に囲まれた領域に形成された、半導体基板2中にチャネル領域8を有するMOSFET3と、MOSFET3上および溝12内の側壁10上に連続して形成された、チャネル領域8に歪みを発生させるストレスライナー膜11とを有する。

(もっと読む)

フラッシュメモリの製造方法

【課題】フラッシュメモリの製造工程において、エッチングによるSTI膜の膜減りを抑制することができる製造方法と、それを可能にするスプリットゲートタイプのMONOS型フラシュメモリ構造を提供する。

【解決手段】ワードゲートとコントロールゲートを含むスプリットゲートタイプのMONOS型フラシュメモリの製造方法であって、STIによって分離された半導体基板の不純物拡散層上に、酸化膜を挟んだワードゲートを形成する工程と、該STIとワードゲートが形成された半導体基板の表面全体に酸化膜、窒化膜、酸化膜の順に成膜されるONO層を形成する工程と、該ONO層の上にコントロールゲート用導電膜(10)を形成する工程と、該コントロールゲート用導電膜の表面全体にマスク用絶縁膜(26)を形成する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】隣接する埋め込みビット線が短絡(ショート)することを防止した半導体装置を提供する。

【解決手段】半導体基板2の面内に枠状に形成された第1の溝部3と、第1の溝部3に絶縁膜4を埋め込むことによって形成された素子分離領域5と、素子分離領域5の内側に形成された素子形成領域6と、素子形成領域6において第1の方向Yに延在し、且つ、格子状に複数並んで形成された第2の溝部7と、第2の溝部7の両側面に不純物を拡散させることによって形成された埋め込みビット線10とを備え、第2の溝部7の両端が素子分離領域5に至るまで第1の方向Yに延在して設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】工程マークやアライメントマーク等を形成するトレンチ内のSOG膜にクラックが発生した場合に、そのクラックが素子形成領域に到達するのを防止する。

【解決手段】半導体基板10の素子形成領域10Tの外側において、工程マーク30Cは、トレンチ31のパターンで形成されている。素子形成領域10Tと、その外側のトレンチ31は層間絶縁膜21に覆われており、層間絶縁膜21は、トレンチ31内を埋めるSOG膜22に覆われている。さらに、半導体基板10の表面上には、トレンチ31及びトレンチ31上のSOG膜22を囲む環状ポリシリコン膜18が形成されている。

(もっと読む)

1 - 20 / 146

[ Back to top ]