Fターム[5F032AA45]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 溝内埋込み分離 (7,414) | 埋込み材料 (3,229) | 酸化シリコン (2,174) | 溝の表面に直接層状に形成されているもの (737)

Fターム[5F032AA45]に分類される特許

1 - 20 / 737

半導体装置およびその製造方法

SOIウエハおよびSOIウエハの製造方法

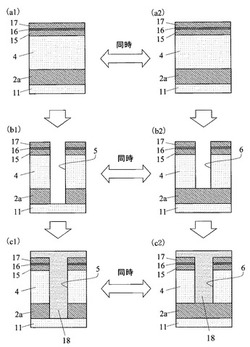

【課題】除電構造と素子分離構造とを有するSOIウエハを、従来より少ない工程で製造することができるSOIウエハの製造方法の提供。

【解決手段】SOIウエハの周縁部分に活性層用半導体層および絶縁酸化膜を貫通する除電用トレンチをエッチングで形成すると同時に、当該周縁部分より内側の内側部分に上記活性層用半導体層を貫通し上記絶縁酸化膜に到達する素子分離用トレンチをエッチングで形成するトレンチ形成ステップを備え、上記トレンチ形成ステップは、上記周縁部分におけるエッチングレートが、上記内側部分におけるエッチングレートよりも高いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

半導体装置及びその製造方法

【課題】エッチングによるマスク窒化膜除去時に、STI構造を構成しているライナー膜に劣化が発生することを防止する。

【解決手段】半導体基板に形成したトレンチ内に素子分離構造を形成する工程を含み、前記素子分離構造を形成する工程は、前記トレンチ内の前記半導体基板上にパッド酸化膜を形成する工程と、前記パッド酸化膜上にALD法によりライナー膜を形成する工程と、前記ライナー膜上にSOD膜を形成する工程と、を含む半導体装置の製造方法。ライナー膜は酸化ハフニウム膜が好ましい。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板をエッチングする際、ハードマスクの肩落ちによるエッチング深さの基板面内での粗密差を低減する。

【解決手段】半導体基板1上に、絶縁層(10,11)とアッシング除去可能な材料層を形成する工程と、材料層をパターニングする工程と、パターニングされた材料層をマスクに、絶縁層を貫通し、少なくとも半導体基板の一部をエッチングする第1のエッチング工程と、材料層がなくなる前にエッチングを一旦停止し、残存する材料層(12)をアッシング除去する工程と、絶縁層をマスクに半導体基板を所定の深さにエッチングする第2のエッチング工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】素子分離用の大きなエアギャップを容易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】一の実施形態による半導体装置の製造方法では、基板内に素子分離溝を形成し、前記素子分離溝の側壁面にアモルファス層を形成する。さらに、前記方法では、前記素子分離溝内に前記アモルファス層を介して犠牲膜を形成し、前記犠牲膜上にエアギャップ膜を形成する。さらに、前記方法では、前記エアギャップ膜の形成後に前記犠牲膜を除去することで、前記エアギャップ膜の下部の前記素子分離溝内にエアギャップを形成する。

(もっと読む)

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチ構造の表面に不要な溝が形成されず、また、素子の面積効率を良好なものとすることができる半導体装置の製造方法の提供。

【解決手段】トレンチ内にポリシリコンが充填され、当該ポリシリコンの上部がシリコン酸化膜により覆われたトレンチ構造を有する半導体装置の製造方法であって、シリコン活性層の上面に第1のシリコン酸化膜が積層されてなる基板に異方性エッチングを行うことにより、上記第1のシリコン酸化膜の上面から上記シリコン活性層内に伸びるトレンチを形成するトレンチ形成工程と、上記トレンチの側壁全体を一体的に覆う第2のシリコン酸化膜を形成する側壁酸化膜形成工程と、上記第2のシリコン酸化膜の形成後に、上記トレンチ内にポリシリコンを充填する充填工程と、上記トレンチ内に充填したポリシリコンの上部露出面を酸化させてキャップを形成するキャップ形成工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】素子の特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板上の一部の領域にマスク膜を形成する工程と、前記マスク膜を形成した領域及び前記マスク膜を形成していない領域の双方において、前記半導体基板の上方に、マスク部材を形成する工程と、前記マスク部材をマスクとしてエッチングを施すことにより、前記マスク膜及び前記半導体基板の上層部分をパターニングする工程と、前記パターニングされたマスク膜をマスクとしてエッチングを施すことにより、前記パターニングされた半導体基板の上層部分の一部を除去する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、2つの埋め込みゲート用の溝部8a,8bによって分断された3つの活性領域6a,6b,6cのうち、中央部に位置する活性領域6bを分断するビットコンタクト用の溝部11の両側面に、埋め込みゲート用の溝部8a,8bの底面と同程度の深さで不純物を拡散させることによって形成された第1の不純物拡散層13a,13bと、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】膜応力の小さい低誘電率の絶縁膜を形成できる基板処理装置を提供する。

【解決手段】処理室内へ無機シリコンガスと酸素含有ガスを供給している状態で、励起エネルギーを処理室内へ供給して、基板表面にシリコン酸化膜を形成するシリコン酸化膜形成工程と、処理室内へ有機シリコンガスを供給している状態で、励起エネルギーを処理室内へ供給して、基板表面にシリコン膜を形成するシリコン膜形成工程と、を行うことにより、処理室内の基板表面に絶縁膜を形成するよう、基板処理装置を構成する。

(もっと読む)

トレンチの埋め込み方法および半導体集積回路装置の製造方法

【課題】 素子の高集積度化がさらに進展し、素子分離用のトレンチのアスペクト比が大きくなったとしても素子分離領域の絶縁性の低下を抑制できるトレンチ埋め込み方法を提供すること。

【解決手段】 第1の最小分離幅を有する幅狭部と、第1の最小分離幅よりも広い第2の最小分離幅を有する幅広部とを含むトレンチが形成された半導体基板上に、シリコン酸化物ライナーを形成する工程と(ステップ2)、シリコン酸化物ライナー上に酸化障壁膜を形成する工程と(ステップ3)、酸化障壁膜上にシリコンライナーを形成する工程と(ステップ4)、トレンチの幅狭部を第1の埋め込み材によって埋め込む工程と(ステップ5)、トレンチの幅広部を第2の埋め込み材によって埋め込む工程と(ステップ6)、シリコンライナーを酸化する工程(ステップ7)とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】デバイス特性の向上を図る。

【解決手段】半導体装置の製造方法は、半導体基板10に基板部10aと前記基板部上のフィン部10bとを形成する工程と、前記フィン部の側面上に、第1シリコン酸化膜12を形成する工程と、前記第1シリコン酸化膜の側面上に、前記シリコン酸化膜の上面より低い上面を有するポリシラザン膜13を形成する工程と、前記ポリシラザン膜を窒化および酸化することでシリコン酸窒化膜13aに転換する工程と、全面に、前記フィン部を覆うように第2シリコン酸化膜14を形成する工程と、前記第1シリコン酸化膜および前記第2シリコン酸化膜をエッチングすることにより、前記第1シリコン酸化膜の上面を前記シリコン酸窒化膜の上面以下の高さにする工程と、前記フィン部内に高濃度半導体層40を形成する工程と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を悪化させず、アクティブ領域を終端領域に対して、簡単な方法により電気的に独立させることができ、さらには素子サイズの小型化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】エピタキシャル層23のアクティブ領域12と終端領域11との間に、エピタキシャル層23の表面24を形成するように、当該表面24に沿って全体にわたって形成されたチャネル層26を、ゲートトレンチ28の深さD1と同じ深さD2を有するアイソレーショントレンチ39で分断する。互いに同じ深さのゲートトレンチ28およびアイソレーショントレンチ39は、同一のエッチング工程で形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和する。

【解決手段】 半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する半導体装置。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】ランプアニールによるレイアウトに起因した温度バラつきを低減する。

【解決手段】この半導体装置10は、基板100と、基板100に埋め込まれた素子分離領域200と、基板100のうち、素子分離領域200の無い領域に形成された不純物層(エクステンション領域322、ソース領域324、エクステンション領域342、及びドレイン領域344)と、を備える。この素子分離領域200は、たとえば、波長300nm以上890nm以下においてSiO2よりも光吸収係数が大きい材料から形成されている光吸収層220を含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させ、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板1の主面に酸化膜として絶縁膜2を形成し、絶縁膜2上に窒化シリコン膜を形成してから、素子分離用の溝4aをプラズマドライエッチングにより形成し、溝4aを埋めるように酸化シリコンからなる絶縁膜6をHDP−CVD法で形成し、CMP処理により溝4aの外部の絶縁膜6を除去し、溝4a内に絶縁膜6を残す。それから、窒化シリコン膜を除去する。その後、絶縁膜2をウェットエッチングで除去して半導体基板1を露出させるが、この際、半導体基板1の主面に140ルクス以上の光を当てながら絶縁膜2をウェットエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】DHF処理後に実施されるHPM処理またはAPM処理を、良好に行うことができる半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、槽内に水を導入して、槽内から希フッ酸を排出する工程と、槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、槽内に、H2O2と、上記水よりも温度の高い温水とを導入する工程とを有する。

(もっと読む)

1 - 20 / 737

[ Back to top ]