Fターム[5F032AA06]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面、底面を絶縁物で分離するもの (1,104) | 支持基板を接着で形成するもの (217)

Fターム[5F032AA06]に分類される特許

1 - 20 / 217

SOIウエハおよびSOIウエハの製造方法

【課題】除電構造と素子分離構造とを有するSOIウエハを、従来より少ない工程で製造することができるSOIウエハの製造方法の提供。

【解決手段】SOIウエハの周縁部分に活性層用半導体層および絶縁酸化膜を貫通する除電用トレンチをエッチングで形成すると同時に、当該周縁部分より内側の内側部分に上記活性層用半導体層を貫通し上記絶縁酸化膜に到達する素子分離用トレンチをエッチングで形成するトレンチ形成ステップを備え、上記トレンチ形成ステップは、上記周縁部分におけるエッチングレートが、上記内側部分におけるエッチングレートよりも高いことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。

【解決手段】SOI基板SB上に形成されたマットMT内に複数のMOSFETを有する半導体装置において、BOX膜を貫き支持基板に達するコンタクトプラグCT2を形成することで、マットMTの周囲を、SOI基板SBの主面に沿う第1方向または第1方向に直交する第2方向に延在する複数のコンタクトプラグCT2により囲む。これにより、コンタクトプラグCT2をガードリングとして用い、マットMTの外部に流れる高周波信号に起因してマットMT内にノイズが発生することを防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】閾値電圧ばらつきを改善した半導体装置の製造方法を提供する。

【解決手段】SOI基板を用いた半導体装置の製造方法において、活性層基板を酸化して埋め込み酸化膜4bを生成する工程と、支持基板3表面に、MOSトランジスタ1の閾値電圧を決定するためのチャネルドープ10を行う工程と、支持基板3と活性層基板5とを前記埋め込み酸化膜を介して貼り合せる工程と、活性層基板を部分的に除去し埋め込み酸化膜4aを露出させる工程と、埋め込み酸化膜4a上にゲート電極6aを形成する工程と、を含む半導体装置の製造方法とする。

(もっと読む)

様々な絶縁領域及び/又は局所的な垂直導電領域を有する混合積層構造物を製造する方法

【課題】化学機械的研磨の長い段階に頼らずに半導体基板上に半導体構造物を製造することを提案する。

【解決手段】本発明は、深さpのパターンを有する表面トポロジーを有する半導体基板上に半導体構造物を製造する方法であって、前記方法は、(a)前記表面に第1絶縁材料の第1層(24)を形成する段階と、(b)前記第1層上に前記第1絶縁材料より密度が低い第2絶縁材料(28)の第2層を形成する段階と、(c)前記段階(a)及び段階(b)によって形成された構造物を薄膜化する段階と、(d)前記段階(c)によって薄膜化された前記構造体の第2層を緻密化する段階と、(e)前記段階(d)によって緻密化された前記第2層を有する構造体を薄膜化する段階と、(f)第2基板を用いた組立段階と、を含む方法である。

(もっと読む)

半導体装置の製造方法、半導体装置、SOI基板の製造方法およびSOI基板

【課題】SOI基板のチャージ蓄積による不良を抑制する。

【解決手段】まず、シード基板100の一面に、シード基板100の表面と同一面を形成するように、開口部220を有する絶縁層200を形成する(絶縁層形成工程)。次いで、シード基板100の一面に接するように、支持基板300を貼り合せる(貼り合せ工程)。次いで、シード基板100または支持基板300の一方を薄板化することにより、当該薄板化基板からなる半導体層120を形成する(半導体層形成工程)。以上の工程により、SOI基板を準備する。次いで、半導体層120に半導体素子60を形成する(半導体素子形成工程)。

(もっと読む)

半導体基板およびその製造方法、その半導体基板を用いた半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した厚さを有する半導体層が1つの絶縁膜上に設けられた半導体基板およびその製造方法、その半導体基板を用いた半導体装置を提供する。

【解決手段】実施形態に係る半導体基板10は、第1絶縁層5と、前記第1絶縁層の上に設けられた半導体層7とを有する半導体基板であって、前記半導体層の中に選択的に設けられ、前記半導体層の表面に平行に延在し、その延在方向の長さが前記第1絶縁層よりも短い第2絶縁層13と、前記半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記半導体層の前記第2絶縁層を含む部分と、前記半導体層の残りの部分と、を電気的に分離する第3絶縁層15と、を備える。

(もっと読む)

半導体装置

【課題】可撓性を有し、曲げ等の物理的変化に対して耐性を有する半導体装置および当該

半導体装置の作製方法を提供することを目的とする。

【解決手段】可撓性を有する基板上に設けられた、半導体膜、半導体膜上にゲート絶縁膜

を介して設けられたゲート電極およびゲート電極を覆って設けられた層間絶縁膜とを有す

る複数のトランジスタと、複数のトランジスタの間に設けられた屈折部分とを有し、屈折

部分は、層間絶縁膜に設けられた開口部に層間絶縁膜より弾性率が低い物質が充填されて

設けられている。また、本発明では、開口部に充填する物質として他にも、層間絶縁膜よ

りガラス転移点が低い物質や塑性を有する物質を設けることができる。

(もっと読む)

半導体装置及びその製造方法並びに抵抗器及び半導体素子

【課題】pn接合におけるリーク電流を抑制する。

【解決手段】N−型半導体層10と、シリサイド層20sがその表面に形成されたP−型半導体層20とが、絶縁体9上に形成される。半導体層10にはPMOSトランジスタを、半導体層20にはNMOSトランジスタを、それぞれ形成することができる。半導体層10,20がpn接合J50aを形成する場合、これはシリサイド層20sの端部から近く、結晶欠陥が小さい位置に存在するので、ここにおけるリーク電流は非常に小さい。半導体層10,20が形成するpn接合は、シリサイド層20sの端部から2μm以下の距離にあることが望ましい。

(もっと読む)

半導体装置及びその製造方法、並びにSOI基板及びその製造方法

【課題】コンタクトホールの形成領域が素子分離領域と重複しても、素子特性の劣化を抑制できるSOI基板とこのSOI基板を用いた半導体装置とを提供する。

【解決手段】半導体装置1は、半導体基材11と埋め込み絶縁膜12と半導体層16とを有するSOI基板と、このSOI基板上に形成された半導体素子構造とを備える。埋め込み絶縁膜12は、半導体基材11から半導体層16を電気的に絶縁分離する機能を有し、窒化膜14を有する。

(もっと読む)

埋め込みドープ層を有する完全空乏型SOIデバイス

【課題】完全空乏型SOIデバイスの製造に適したセミコンダクタオンインシュレータ(SeOI)ウェーハおよびそれを用いたデバイスを提供すること。

【解決手段】本発明は、第1の基板の表面領域にドープ層、ドープ層上に埋め込み酸化物層、埋め込み酸化物層上に半導体層を形成してSeOIウェーハを得る。SeOIウェーハの第2の領域の埋め込み酸化物層および半導体層を維持しながらSeOIウェーハの第1の領域から埋め込み酸化物層および半導体層を除去し、第2の領域に上部トランジスタを形成する。第1の領域にリセスチャネルアレイトランジスタを形成し、第2の領域にpチャネルトランジスタおよび/またはnチャネルトランジスタを形成する。ドープ層内またはこの近傍にバックゲートを形成し、第1の領域にリセスチャネルアレイトランジスタを形成し、ドープ層内またはその近傍にソース領域およびドレイン領域を形成する。

(もっと読む)

SOIウェハの製造方法

【課題】SOIウェハの支持基板ウェハの帯電を除去することのできるSOIウェハの製造方法を提供する。

【解決手段】活性層基板10と支持基板20との貼り合わせ面に酸化膜22を形成する酸化膜形成工程と、活性層基板10と支持基板20とを貼り合わせる貼り合わせ工程と、支持基板20に向けて活性層基板10に酸化膜22に達するまでのトレンチを形成するトレンチ形成工程と、トレンチから酸化膜22に向けて予め定められたイオンを注入するイオン注入工程と、トレンチ内部をポリシリコン3で充填する充填工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して貼り合わせられ、島状に絶縁分離されたGe層8(第2の半導体層)が設けられ、このGe層8に高濃度のソースドレイン領域(14、15)が形成されたPチャネルのMISFETと、Si基板1上にシリコン窒化膜2及び一部に空孔5を有するシリコン酸化膜3を介して、空孔5直上の歪みSi層7を挟み、左右にSiGe層6を有する構造からなるエピタキシャル半導体層(第1の半導体層)が島状に絶縁分離されて設けられ、歪みSi層7には概略チャネル領域が形成され、SiGe層6には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成されたNチャネルのMISFETとから構成したCMOS。

(もっと読む)

半導体装置およびその製造方法

【課題】少工数で製造可能で且つ高い耐圧性能を有する半導体装置を提供する。

【解決手段】素子形成領域と、素子形成領域を外部領域から絶縁分離するべく素子形成領域表面から基板表面までの深さで素子形成領域側面を包囲するよう形成された第1絶縁トレンチ領域10aとを備える半導体装置であって、素子形成領域は、埋め込みコレクタ領域と、コレクタ耐圧領域4と、ベース領域5と、表面コレクタ領域8bと、エミッタ領域8aと、ベース領域と表面コレクタ領域との間におけるキャリアの直線的な移動を遮るよう、当該領域間において素子形成領域表面から基板表面にまでの深さで形成される第2絶縁トレンチ領域10bとを備え、半導体装置を平面視した際、第2絶縁トレンチと第1絶縁トレンチ領域との間には、キャリアが第2絶縁トレンチを迂回してベース領域と表面コレクタ領域との間を移動するためのキャリア迂回領域12a,12bが形成される。

(もっと読む)

埋め込み配線を備える基板、その製造方法、これを利用する半導体装置およびその製造方法

【課題】 低抵抗の埋め込み配線を備える基板の製造方法を提供する。

【解決手段】 始めに半導体用基板100の第1面S1上に導電層120を形成する。次に、導電層120をパターニングして第1方向に延長する線形の導電層パターン122を形成する。導電層120をパターニングするとき露出する半導体用基板100をエッチングして導電層パターン120の下部に第1方向に延長する線形の半導体パターン104を形成する。次に導電層パターン120および半導体パターン104上に絶縁層150を形成する。半導体用基板100の第1面S1側の絶縁層150が支持基板160と当接するように支持基板160上に配置する。次に半導体用基板100のイオン注入層102側の絶縁層150が露出するように半導体用基板100を除去する。これにより、導電層パターン120は、半導体パターン104の埋め込み配線として利用することができる。

(もっと読む)

半導体装置

【課題】本発明は、SOIにおいて適したゲッタリング方法を適用して得られる半導体装置を提供する。

【解決手段】埋め込み酸化膜と、埋め込み酸化膜上に表面シリコン層を有するSOI構造を有する半導体装置において、埋め込み酸化膜上に、表面シリコン層を活性層として有するトランジスタと、素子分離絶縁膜を有し、素子分離絶縁膜上に容量が形成されており、素子分離絶縁膜に希ガス元素又は金属元素が含まれていることを特徴とする半導体装置とする。

(もっと読む)

半導体装置

【課題】支持基板に接地電極を備えることなく、第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供する。

【解決手段】支持基板10を、第1導電型領域10aと第2導電型領域10bとを有し、第1素子形成領域20にノイズが印加されてノイズが伝播されたときの当該ノイズの伝播経路中に、第1、第2導電型領域10a、10bで構成されるPNP接合またはNPN接合を有するものとする。このような半導体装置では、PNP接合またはNPN接合の間に構成される空乏層により、第1、第2素子形成領域20、30の間でノイズが伝播することを抑制することができる。

(もっと読む)

半導体装置

【課題】デカップリング容量及びガードリング等のノイズを低減する構造物を設けるための専用配置領域を必要としない半導体集積回路装置を提供する。

【解決手段】P−型シリコンからなる支持基板2を設け、この支持基板2上にP+型シリコン層3を設け、その上にN+型シリコン層4及びP+型シリコン層12を相互に同層に設ける。P+型シリコン層3及びN+型シリコン層4の不純物濃度は支持基板2の不純物濃度よりも高くする。また、N+型シリコン層4及びP+型シリコン層12上の全面に、埋込酸化膜5及びSOI層6を設ける。そして、P+型シリコン層3を接地電位配線GNDに接続し、N+型シリコン層4を電源電位配線VDDに接続する。これにより、P+型シリコン層3とN+型シリコン層4との間に、電源に並列に接続されたデカップリング容量C1が形成される。

(もっと読む)

逆阻止型絶縁ゲート形バイポーラトランジスタおよびその製造方法

【課題】半導体特性または拡散炉に悪影響を及ぼすような高温、長時間の拡散をすることなく、また、トレンチ形成のような長時間プロセス加工による良品率低下が無く、高耐圧用の厚い半導体基板の表面から裏面に達する程度の深さの拡散分離層を備える逆阻止型絶縁ゲート形バイポーラトランジスタの製造方法の提供。

【解決手段】第1導電型半導体基板1の半導体デバイス領域を取り巻く位置に、該第1導電型半導体基板を貫通する第2導電型貫通領域5を、いずれか一方の主面または両主面から形成する工程と、複数枚の前記第1導電型半導体基板1を鏡面加工し、前記第2導電型貫通領域5の位置を合わせて真空中で貼り合わせる工程とを有する半導体装置の製造方法とする。

(もっと読む)

半導体装置及びその製造方法

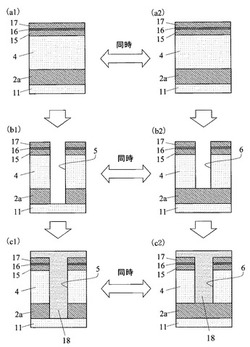

【課題】トレンチ分離されたSOI基板にIGBTとその制御回路等が形成される半導体装置において、IGBTの高耐圧化及びターンオフ特性の改善等が必要になる。

【解決手段】ダミー半導体基板16にN型エピタキシャル層8を形成し、N型エピタキシャル層8にトレンチ30を形成し、トレンチ30側壁及びN型エピタキシャル層8表面にN型バッファ層7、次にP型埋め込みコレクタ層6を形成し、トレンチ30底面及びP+型埋め込みコレクタ層6上を埋め込み絶縁膜5で被覆する。埋め込み絶縁膜5上をポリシリコン膜3で被覆し、該ポリシリコン膜3と絶縁膜2を介してP型半導体基板1を貼り合わせた後、ダミー半導体基板16を除去し、略同一平面状に露出するトレンチ30底面の埋め込み絶縁膜5、P+型埋め込みコレクタ層6、N型バッファ層7、N型ドリフト層8a等を具備するSOI基板を形成する。該SOI基板にIGBT等を形成する。

(もっと読む)

多層ウェーハ中のトレンチ構造

【課題】バーズビーク効果を軽減することのできる、SOIウェーハ内にトレンチを製造する方法を提供すること。

【解決手段】本発明は、基板と、基板上の酸化物層と、酸化物層上の半導体層とを備える多層ウェーハ内にトレンチ構造を製造する方法に関し、本方法は、半導体層および酸化物層を貫通して基板中へ延在するトレンチを形成するステップと、トレンチの内部表面において、半導体層のいくらかの材料が、トレンチの内部表面に露出した酸化物層の部分の一部の上に少なくとも流れるように、形成されたトレンチのアニール処理を行うステップとを含む。

(もっと読む)

1 - 20 / 217

[ Back to top ]