Fターム[5F110DD30]の内容

Fターム[5F110DD30]に分類される特許

41 - 53 / 53

半導体記憶装置およびその製造方法

【課題】従来の設計環境を活用することができ、製造コストの低い半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置の製造方法は、半導体基板10に複数のトレンチ22を形成し、半導体基板を水素雰囲気中において熱処理することによって、複数のトレンチの上部の開口を塞ぎつつ該複数のトレンチの下部の空間を互いに結合し、空洞25上に設けられた半導体層26を形成し、素子分離形成領域にある半導体層をエッチングし、半導体層の側面および底面に絶縁膜30を形成し、半導体層の下の空洞に電極材料31を充填し、素子分離形成領域における電極材料上に絶縁膜を形成することによって素子分離32を形成し、半導体層上にメモリ素子MCを形成することを具備する。

(もっと読む)

半導体装置

【課題】トランジスタ領域におけるゲート間距離などのレイアウトに依存することなく、半導体層のチャネル領域に有効に応力を作用させることができる半導体装置を実現する。

【解決手段】MOSトランジスタを備える半導体装置の構成として、素子分離層4で素子分離されたトランジスタ領域を有する半導体層3と、トランジスタ領域で半導体層3の第1の面上にゲート絶縁膜5を介して形成されたゲート電極6と、トランジスタ領域で半導体層3の第2の面上に形成された応力伝達パターン19Aと、半導体層3の第2の面上に応力伝達パターン19Aを覆う状態で形成された応力膜20とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】

埋め込み絶縁(BOX)膜の薄い完全空乏型シリコンオンインシュレータ(FDSOI)型トランジスタで、トランジスタの性能向上を図る歪印加手法の効果の増大を図る。

【解決手段】

極薄のSOI構造6を有するFDSOI型トランジスタで、極薄のBOX層4の裏側5に応力発生領域を設けてチャネル形成部分に歪を印加する。応力発生領域は、BOX裏側の所望の領域をイオン注入により非晶質化させ、しかる後に応力印加膜3を形成した状態において熱処理再結晶化を行うことにより、応力印加膜3からの応力をチャネル形成部分に転写させることで形成する。

(もっと読む)

半導体装置及び当該半導体装置を具備するIDラベル、IDタグ、IDカード

【課題】RFIDを有する半導体装置において、駆動電源のための電池の経時的劣化に伴う電池の残存容量の確認や電池の交換作業をすることなく、個体情報を送受信することができ、且つ駆動するための電源を外部からの電磁波の電力が十分でない場合であっても良好な個体情報の送受信状態を維持するRFIDを有する半導体装置を提供することを課題とする。

【解決手段】信号処理回路と、信号処理回路に接続された第1のアンテナ回路及び第2のアンテナ回路と、信号処理回路に接続されたバッテリーとを設け、第1のアンテナ回路は、信号処理回路に記憶されたデータを送信するための信号を送受信するものであり、第2のアンテナ回路は、バッテリーに充電するための信号を受信するものであり、第1のアンテナ回路が受信する信号と第2のアンテナ回路が受信する信号の波長が異なる構成とする。

(もっと読む)

半導体基板の製造方法

【課題】コストの上昇や、信頼性の低下を招かずにSOI構造を形成すること。

【解決手段】半導体基板の表面に複数の第1のトレンチを形成する工程と、

前記半導体基板に熱処理を施すことによって、前記複数の第1のトレンチを1つの平板状の空洞に変える工程と

を含むことを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子が形成される半導体基板の表面領域に結晶欠陥がより少なく、データを確実に保持でき、並びにコストが低廉な半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、半導体基板内にゲルマニウム含有層を形成するステップと、前記基板の表面から前記ゲルマニウム含有層に達するトレンチを形成するステップと、前記ゲルマニウム含有層を除去し、空洞を形成するステップとを備える。

(もっと読む)

活性半導体領域の下全面に存在し、応力を発生する誘電体エレメントを有するトランジスタ

【課題】 活性半導体領域の下全面に存在し、応力を発生する誘電体エレメントを有する半導体を作成すること。

【解決手段】 PFETのソース、ドレイン、及びチャネル領域が配置される活性半導体領域の底面の下全面に存在する独立した応力を発生する誘電体エレメントを含む構造体によって、圧縮応力がPFETのチャネル領域に加えられる。具体的には、応力を発生する誘電体エレメントは、活性半導体領域の底面の全面に接触し、それゆえ底面の面積と同一の広がりを持つ面積を有するコラプスド酸化物の領域を含む。応力を発生する誘電体エレメントの端部にある鳥嘴状酸化物領域が、応力を発生する誘電体エレメントの端部に上向きの力を加えて、PFETのチャネル領域に圧縮応力を与える。

(もっと読む)

薄膜トランジスタ基板とその製造方法

【課題】薄膜のリフティングが減少した薄膜トランジスタ基板を提供する。

【解決手段】本発明による薄膜トランジスタ基板は、プラスチック絶縁基板と;前記プラスチック絶縁基板の一面に形成されており、第1屈折率を有する第1シリコン窒化物層と;前記第1シリコン窒化物層上に形成されており、前記第1屈折率より小さい第2屈折率を有する第2シリコン窒化物層を含む薄膜トランジスタとを含むことを特徴とする。

(もっと読む)

薄膜トランジスタ基板及びその製造方法

【課題】工程効率に優れた薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】遮断膜上に形成されチャンネル領域両側に隣接した第1導電型低濃度ドーピング領域と第1導電型低濃度ドーピング領域に隣接した第1導電型ソース/ドレイン領域を含む第1半導体層と第1半導体層上に形成される第1ゲート絶縁膜と第1ゲート絶縁膜上に形成され第1半導体層内に形成されたチャンネル領域と低濃度ドーピング領域と重畳する第2ゲート絶縁膜と第2ゲート絶縁膜上に形成される第1ゲート電極とを含む第1導電型MOSトランジスタと、遮断膜上に形成されチャンネル領域両側に隣接した第2導電型ソース/ドレイン領域を含む第2半導体層と第2半導体層上に形成された第1ゲート絶縁膜と第1ゲート絶縁膜上に形成され第2半導体層と重畳する第2ゲート絶縁膜と第2ゲート絶縁膜上に形成される第2ゲート電極とを含む第2導電型MOSトランジスタとを有する。

(もっと読む)

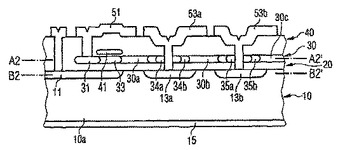

MOS型電界効果トランジスタ及びその製造方法

【課題】薄膜SOI構造を用いて高速化及び低消費電力化を実現するMOS型電界効果トランジスタの製造方法を提供することを課題とする。

【解決手段】埋め込み酸化膜上にチャネル層を有する半導体基板上に形成されるMOS型電界効果トランジスタの製造方法であって、前記半導体基板上にゲート酸化膜を介してゲート電極3を形成する工程と、前記ゲート電極3の側壁を覆う第1のサイドウォール16を形成する工程と、前記埋め込み酸化膜をエッチングしてボックス酸化膜5を形成する工程と、前記ボックス酸化膜5の側壁を覆う第2のサイドウォール6を形成する工程とを有し、前記第2のサイドウォール6は、前記ボックス酸化膜5の側壁に延在して、下方に向かって伸びるように形成されることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 容易に作製することができ、信頼性の高い半導体装置及びその製造方法を提供すること。

【解決手段】 基体1上に導体又は半導体材料を印刷法又は/及び塗布法によって島状パターン6に形成する工程と、この島状パターン6に有機半導体分子7を結合させて導電路8を形成する工程と、この導電路8を電界によって制御する制御部を形成する工程とを有する、半導体装置の製造方法。基体1と、導体又は半導体材料の印刷又は/及び塗布によって前記基体上に形成された島状パターン6と、この島状パターン6に有機半導体分子7が結合されて形成された導電路8と、この導電路8を電界によって制御する制御部とを有する、半導体装置。

(もっと読む)

半導体装置およびその作製方法

【課題】 大面積のガラス基板上に薄膜からなる集積回路を形成した後、基板から剥離を行い、接触、好ましくは非接触でデータの受信または送信が可能な微小なデバイスを大量に効率よく作製する方法を提供することを課題とする。特に薄膜からなる集積回路は、非常に薄いため、搬送時に飛んでしまう恐れがあり、取り扱いが難しかった。

【解決手段】

本発明は、分離層に対して少なくとも異なる2種類の方法を用いてダメージ(レーザ光照射によるダメージ、エッチングによるダメージ、または物理的手段によるダメージ)を複数回与えることにより、基板から被剥離層を効率よく剥離する。また、剥離後のデバイスに反りを持たせることによって、個々のデバイスの取り扱いを容易とする。

(もっと読む)

絶縁耐力の高いSOI半導体素子

本発明は、第1半導体域と第2半導体域との間に配置されたフィールド電極および/またはフィールド領域を備えた、SOI半導体素子に関するものである。電気的結合を、フィールド電極とフィールド領域との間で行うことができる。  (もっと読む)

(もっと読む)

41 - 53 / 53

[ Back to top ]