Fターム[5F110DD30]の内容

Fターム[5F110DD30]に分類される特許

21 - 40 / 53

背面放熱を伴う絶縁体上半導体

本発明の実施形態は、絶縁体上半導体(SOI)構造からの熱の放散を提供する。一実施形態では、集積回路を製造する方法が開示される。第1のステップでは、アクティブ回路が、SOIウエハのアクティブ層内に形成される。第2のステップでは、基板材料が、SOIウエハの背面上に配置された基板層から除去される。第3のステップでは、絶縁材料が、SOIウエハの背面から除去されて掘られた絶縁体領域を形成する。第4のステップでは、放熱層が、前記掘られた絶縁層上に堆積される。放熱層は、熱的に伝導性があり、かつ電気的に絶縁する。  (もっと読む)

(もっと読む)

冷却機構を含む接合型半導体構造体とその形成方法

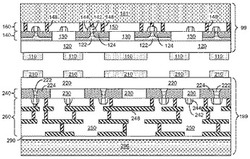

【課題】 冷却機構を有する接合型半導体基板を形成するための構造体、設計構造体、及びその形成方法を提供すること。

【解決手段】 2つの半導体基板を備える接合型基板が提供される。各々の半導体基板は、半導体デバイスを含む。少なくとも1つの基板貫通ビアが2つの半導体基板の間に設けられ、それらの間に単一の経路を提供する。2つの半導体基板の底側は、冷却機構を含む少なくとも1つの接合材料層によって接合される。1つの実施形態において、冷却機構は冷却チャネルであり、その中を通って冷却流体が流動し、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。別の実施形態において、冷却機構は、2つの端部とそれらの間の連続した経路を備えた導電性冷却フィンである。冷却フィンはヒートシンクに接続され、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。

(もっと読む)

有機電界発光表示装置及びその製造方法

【課題】有機電界発光表示装置及びその製造方法を提供する。

【解決手段】画素領域と非画素領域を備える基板と、前記基板上に位置するバッファ層と、前記バッファ層上に位置し、チャネル領域及びソース/ドレイン領域を備える半導体層と、前記半導体層のチャネル領域に対応するように位置するゲート電極と、前記半導体層と前記ゲート電極とを絶縁させるゲート絶縁膜と、前記半導体層のソース/ドレイン領域に電気的に接続するソース/ドレイン電極と、前記ゲート電極と前記ソース/ドレイン電極とを絶縁させる層間絶縁膜とを含み、前記バッファ層、ゲート絶縁膜、及び層間絶縁膜は、非画素領域上の一部が除去された形態で位置し、前記除去された面積はパネル面積の8〜40%であることを特徴とする有機電界発光表示装置の製造方法に関する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、しきい値電圧のばらつきが大きいトランジスタのしきい値電圧を調整してしきい値電圧のばらつきを低減することを可能にする。

【解決手段】基板11と絶縁層12とシリコン層13が積層されてなるSOI基板10の該シリコン層13の表面側にトランジスタ20を形成する工程と、SOI基板10上に、トランジスタ20を被覆する第1絶縁膜30と、トランジスタ20に電気的に接続される配線部40とを形成する工程と、配線部40を通じてトランジスタ20のしきい値電圧を測定する工程と、第1絶縁膜30表面に第2絶縁膜を介して支持基板を形成する工程と、SOI基板10の裏面側の基板11と絶縁層12の少なくとも一部を除去する工程と、測定されたしきい値電圧に基づいてトランジスタ20のしきい値電圧を調整する工程を有する。

(もっと読む)

SOI基板の作製方法

【課題】他の基板と区別して識別できるマークが形成され、ガラス基板上に、バッファ層を間に介在して単結晶半導体層が設けられたSOI基板を歩留まり良く作製する。

【解決手段】ガラス基板上に、バッファ層を間に介在させて、単結晶半導体層を形成し、バッファ層および単結晶半導体層が積層された積層体の周辺領域を除去してガラス基板を露出させる。そして、バッファ層および単結晶半導体層が積層された積層体の外側に露出するガラス基板にマークを形成する。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、寄生容量を充放電する変位電流が発生することを抑制し、回路の誤動作を防止する。

【解決手段】電界緩和層2dと支持基板2におけるp型の部分2eとによって構成されるPN接合により、高耐圧ダイオードを構成する。これにより、高耐圧ダイオードを構成するPN接合部に空乏層が形成され、この空乏層によって各部位および各支持台31a、31bを独立した電位に固定することが可能となる。このため、dv/dtサージによる変位電流の発生を抑制することが可能となる。また、変位電流が発生したとしても、支持台31aを通じて変位電流を引抜ける。このため、変位電流が低電位基準回路部LV内に流れることを防止することが可能となり、変位電流によって回路の誤動作が生じることを防止できる。

(もっと読む)

半導体装置及びその作製方法

【課題】単結晶半導体層と支持基板との間に導電層を形成する半導体装置において、熱による支持基板の反り量の小さくする。また、同半導体装置の生産性の良い作製方法を提供する。

【解決手段】単結晶半導体層と支持基板との間に導電層が形成され、前記単結晶半導体層と前記導電層との間にゲート絶縁膜が形成された構造を有し、前記導電層と支持基板との間に、隙間が設けられる構成を有する。単結晶半導体基板に前記導電層を作製時、第一の絶縁層が単結晶半導体層と支持基板との間に形成されるが、前記導電層形成時に用いたレジスト上に成膜し、この上部の第一の絶縁層はレジストと共に除去することで、第一の絶縁層に凹部を設ける。前記凹部を有した状態で単結晶半導体基板と支持基板とを貼り合わせることで、前記隙間を有する構造とし、また貼りあわせ前の単結晶半導体基板表面平坦化は不要となる。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、支持基板と活性層との間に配置される絶縁膜(例えば、BOX)にて構成される寄生容量を充放電する変位電流が発生することを抑制し、回路の誤動作を防止する。

【解決手段】低電位基準回路部LVに形成された第1サージ吸収層2aがトレンチ分離部5b内のドープトPoly−Si8bを通じてGND配線17aに電気的に接続されることでGND電位とされ、高電位基準回路部HVに形成された第2サージ吸収層2bがトレンチ分離部5b内のドープトPoly−Si8bを通じて仮想GND配線17bに電気的に接続されることで仮想GND電位とされるようにする。

(もっと読む)

半導体装置およびその製造方法

【課題】耐圧性の高い半導体装置を提供する。

【解決手段】このHVICは、シリコン基板1の表面に誘電体層2とSOI活性層3を積層し、SOI活性層3の表面にトランジスタ4を形成し、トランジスタ4の周りにトレンチ分離領域5を形成したものである。誘電体層2は、シリコン基板1の表面に形成された第1の埋込酸化膜10と、素子領域に対向して第1の埋込酸化膜10の下に形成されたシールド層11と、シールド層11の周りに形成された第2の埋込酸化膜12と、シールド層11および第2の埋込酸化膜12の下に形成された第3の埋込酸化膜13とを含む。したがって、誘電体層2内における等電位分布曲線PCの密度が小さくなり、高い耐圧性が得られる。

(もっと読む)

半導体装置

【課題】効率良く放熱すること、周囲の回路の誤動作の防止およびコンパクトな装置を提供する。

【解決手段】空洞部を内部に有し、空洞部の上方に形成された第1半導体領域と、空洞部を取り囲む領域の上方に形成された第2半導体領域と、を有する半導体基板と、第1半導体領域に形成された電力増幅器と、第2半導体領域に形成されたデジタル回路またはアナログ回路と、第1半導体領域を覆う第1絶縁膜と、第2半導体領域を覆う第2絶縁膜と、第2絶縁膜に設けられ、空洞部に接続する第1開口部と、電力増幅器に対して第1開口部と反対側の第2絶縁膜に設けられ、空洞部に接続し、第1開口部よりも開口面積が小さい第2開口部と、第1開口部から第2開口部に向かって外気が流れるように第1および第2絶縁膜上に形成され、第1開口部の第2開口部側の端部から第2開口部に向かうに連れて断面積が小さくなる流路とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】 nチャネル導電型電界効果トランジスタ及びpチャネル導電型電界効果トランジスタの電流駆動能力の向上を図る。

【解決手段】 半導体基板の一主面の第1の領域にチャネル形成領域が構成されたnチャネル導電型電界効果トランジスタと、前記半導体基板の一主面の第1の領域と異なる第2の領域にチャネル形成領域が構成されたpチャネル導電型電界効果トランジスタとを有する半導体装置であって、前記nチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力と、前記pチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力とが、各々で異なっている。前記nチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力は引っ張り応力であり、前記pチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力は圧縮応力である。

(もっと読む)

薄膜トランジスタ、配線基板、表示装置および電子機器

【課題】水分および酸素が吸着することによる経時的な特性の低下を回復することができる薄膜トランジスタ、かかる薄膜トランジスタを備え信頼性の高い配線基板、表示装置および電子機器を提供すること。

【解決手段】本発明の薄膜トランジスタは、基板2上に設けられ、ソース電極3およびドレイン電極4と、有機半導体層5と、ゲート絶縁層6と、ゲート電極7と、有機半導地層5およびゲート絶縁層6を加熱する加熱手段12と、加熱手段12の作動を制御する機能を有する制御手段13とを有しており、制御手段13は、加熱手段12を所定時に作動させることにより、有機半導体層5およびゲート絶縁層6を加熱して、有機半導体層5およびゲート絶縁層6に吸着した水分および酸素の吸着量を低下させるよう構成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】完全空乏型SOIトランジスタ、特にNMOSトランジスタにおいて、寄生チャネルの防止効果ばらつきを抑制し、さらに閾値電圧ばらつきをも制御して歩留の安定した完全空乏型SOIトランジスタを有する半導体装置の製造方法を提供する。

【解決手段】完全空乏型SOIトランジスタ、特にNMOSトランジスタの製造方法においてウエル形成工程前あるいは後に追加でイオン注入法を用いて絶縁膜に不純物注入を行う工程を有することで、製造過程における熱履歴のばらつきによる埋め込み絶縁膜への不純物の拡散を抑える。

(もっと読む)

半導体装置

【課題】高耐圧で、安全動作領域が広く、かつ、熱散逸性がよく、有効コンダクタンスおよび周波数特性が良好なSOIデバイスを提供すること。

【解決手段】半導体装置100において、p-基板101の表面層の一部にはBOX領域102が設けられる。BOX領域102は、ゲート構造部130の中心から下ろした垂線Lc付近まで設けられており、ドレイン領域112および拡張ドレイン領域108をp-基板101から分離する。ドレイン領域112の厚さは150nm〜300nmのいずれかであり、BOX領域102の厚さは150nm以上である。

(もっと読む)

光検出装置および電気光学装置

【課題】不純物導入工程として、N型およびP型のうちのいずれか一方の不純物を導入する工程のみを行なうだけで光センサを形成することのできる光検出装置、およびこの光検出装置を備えた電気光学装置を提供すること。

【解決手段】光検出装置300のセンサ回路310において、主センサ310Aおよび副センサ310Bは、真性領域1xの両側に高濃度N型の第1の不純物導入領域1yおよび第2の不純物導入領域1zが形成された半導体膜1wと、真性領域1xに対して絶縁層4aを介して対向する透光性のバイアス印加用電極5aとを備え、薄膜トランジスタと同一構造を有している。バイアス印加用電極5aに薄膜トランジスタをオフとする方向の電圧を印加するとともに、第1の不純物導入領域1yと第2の不純物導入領域1zとの間に所定の電圧を印加すると、真性領域1xに光が入射した際、光電流が流れる。

(もっと読む)

電子装置、放熱用基板及び電子機器

【課題】可撓性を維持しつつ、放熱フィンにより放熱性を向上させた電子装置および当該電子装置を備えた電子機器を提供する。

【解決手段】本実施形態に係る電子装置は、可撓性を有する薄膜装置1と、薄膜装置1に設けられ、互いに分離した複数の放熱フィン3と、を有する。各放熱フィン3は、テーパー状に成形されている。放熱フィン3と薄膜装置1との間には、熱伝導性の接着層2が介在している。接着層2は、基板上において複数に分割されている。または、接着層2は、シート状に成形され、複数の放熱フィンと薄膜装置1との間に介在している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】SOI基板を用いた高周波特性の良好なシリコンからなる半導体装置を得る。

【解決手段】シリコン基板上にシリコン酸化層が形成され、更にその上に薄膜シリコン層が形成されているSOI基板と、前記薄膜シリコン層に形成されたMOSFETとを備え、前記MOSFETの形成されている領域に対応する前記シリコン酸化層を介した背面のシリコン基板の領域が除去されていることを特徴とする半導体装置を提供することにより上記課題を解決する。

(もっと読む)

配線パターンとこれを用いた電子素子、有機半導体素子、積層配線パターンおよび積層配線基板

【課題】導電パターンの角部の盛り上がりが少なく、絶縁層を介して積層配線構造とした場合でも絶縁特性の良好な配線パターンと、これを用いた電子素子等を提供する。

【解決手段】濡れ性変化層2に、エネルギーを付与して高表面エネルギー部3とし、その上に導電性液体により導電パターン5を形成して配線パターン1とする。その際、導電パターンの平面視形状は角部に面取りが施された矩形の配線形状とし、その断面視形状は該角部の盛り上がりが少なく、パターン中央部となだらかに連なり全体が略平坦な形状とする。配線パターン1を用いて積層配線パターン、積層配線基板を構成する。又は濡れ性変化層2の低表面エネルギー部に接して半導体層を設け、電子素子、有機半導体素子を構成する。

(もっと読む)

薄膜トランジスタ基板、その製造方法及び薄膜トランジスタ基板形成用ベース基板

【課題】キャリア移動度がよく且つプラスチック基材に密着性よく設けられたポリシリコン膜を有する、低コストの薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】プラスチック基材10と、プラスチック基材10上に形成された歪付与膜11と、歪付与膜11上に形成されたバッファ膜12と、バッファ膜12上に形成されたポリシリコン膜13と、そのポリシリコン膜13上に形成されたゲート絶縁膜14と、ゲート絶縁膜14上に、又はゲート絶縁膜14のコンタクトホールを介して形成された電極15と、電極15等を覆う保護膜18とを有する薄膜トランジスタ基板1により、上記課題を解決する。

(もっと読む)

半導体薄膜改質装置

【課題】ステージと基板との位置ずれを抑制することにより、所望の領域のみにレーザを照射することができるようにする。

【解決手段】半導体材料の付着した基板を所定の基板載置部に収納可能とする密閉容器と、半導体材料に照射されて半導体材料を所定の熱処理温度まで加熱するための光を照射する光源と、密閉容器に設けられて光源からの光を透過して密閉容器内に導入するための光透過窓と、基板載置部に設けられて基板を基板載置部に固定保持するための保持手段と、光の照射時における密閉容器内の雰囲気圧力を、光照射によって溶融加熱された半導体材料の温度によって規定される蒸気圧を下まわらないように制御する圧力制御手段とを備える。

(もっと読む)

21 - 40 / 53

[ Back to top ]