Fターム[5F110EE42]の内容

Fターム[5F110EE42]の下位に属するFターム

Fターム[5F110EE42]に分類される特許

201 - 220 / 2,712

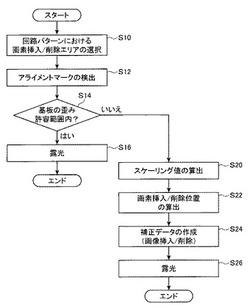

薄膜トランジスタの製造装置およびその製造方法、ならびにプログラム

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法、ならびにプログラムを提供する。

【解決手段】本発明は、基板上にゲート電極、ゲート絶縁層、半導体層、ソース電極およびドレイン電極が少なくとも設けられた薄膜トランジスタの製造方法である。ソース電極およびドレイン電極を形成する工程において、基板の歪み、または基板の伸縮率に基づいて、露光データを、スケーリング処理を用いて薄膜トランジスタのチャネル長を固定した状態で補正して第1の補正データを作成する。この第1の補正データに基づいて、ソース電極およびドレイン電極の形成領域にレーザ光を照射し、その形成領域を親液性にする。この形成領域に、ソース電極およびドレイン電極となる液滴を、打滴データに基づいて打滴する。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間にバッファ層が設けられた逆スタガ型(ボト

ムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン

電極層と半導体層との間に、半導体層よりもキャリア濃度の高いバッファ層を意図的に設

けることによってオーミック性のコンタクトを形成する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、少なくとも酸化物半導体膜中に希ガスイオンを注入する注入工程を行い、減圧下、窒素雰囲気下、又は希ガス雰囲気下において、希ガスイオンを注入した酸化物半導体膜に加熱工程を行って希ガスイオンを注入した酸化物半導体膜中に含まれる水素若しくは水を放出させ、酸化物半導体膜を高純度化する。

(もっと読む)

薄膜トランジスタの製造装置およびその製造方法

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法を提供する。

【解決手段】本発明は、基板上に薄膜トランジスタを製造する製造装置であり、基板に関する基板情報を取得する取得部と、取得部で得られた基板に関する基板情報に基づいて、基板の伸縮強度が高い方向を特定し、伸縮強度が高い方向と薄膜トランジスタのチャネル領域を挟んでソース電極およびドレイン電極が配置される配置方向とが直交するように薄膜トランジスタを形成する向きを設定する設定部とを有する。

(もっと読む)

有機TFT用ゲート絶縁膜および該絶縁膜を有する有機TFT素子

【課題】本発明の目的は、表面撥水性、絶縁性に優れた薄膜を与える硬化性組成物からなる有機TFT用ゲート絶縁膜およびそれを用いた有機薄膜トランジスタ素子を提供することである。

【解決手段】本発明とは、エポキシ基含有化合物を主成分とする硬化性組成物から成り、硬化後の薄膜表面における水接触角が95度以上であることを特徴とする有機TFT用ゲート絶縁膜であり、絶縁性に優れ、かつ表面撥水性が高いことより有機TFT用絶縁膜として適用でき、優れたトランジスタ特性発現する有機TFT素子を与える得ることを特徴する。

(もっと読む)

半導体装置の製造方法、強誘電体素子の製造方法および電子機器の製造方法

【課題】液体プロセスに採用し易い配向性の制御が可能な半導体装置や強誘電体素子の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、ソース電極およびドレイン電極と、前記ソース電極及び前記ドレイン電極との間に配置され、チャネル部を有する有機半導体膜と、ゲート電極と、前記チャネル部と前記ゲート電極との間に配置されたゲート絶縁膜と、を有する半導体装置の製造方法であって、前記チャネル部を第1の温度に加熱する工程と、前記第1の温度の前記有機半導体膜に、前記第1の温度よりも低い第2の温度の絶縁性ポリマーを含む液滴材料を配置し一定の方向に延ばす塗工工程により前記ゲート絶縁膜を形成する工程と、を有することを特徴とする。

(もっと読む)

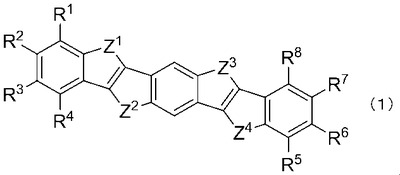

可溶性ヘテロアセン化合物及び該化合物を含有する薄膜および有機トランジスタ

【課題】有機半導体材料として好適な新規化合物の提供。

【解決手段】下記式(1)で示される化合物。

[式中、Z1〜Z4はそれぞれ独立に、硫黄原子又はセレン原子を表す。R1〜R8はそれぞれ独立に、水素原子、フッ素原子で置換されていてもよい炭素数1〜30のアルキル基、フッ素原子で置換されていてもよい炭素数1〜30のアルコキシ基、又は特定な置換シリル基を表す。]

(もっと読む)

電界効果トランジスタの製造方法及びそれに用いる製造装置

【課題】生産性が高く微細な電界効果トランジスタとその製造方法ならびに製造装置を提供すること。

【解決手段】以下の工程(1)から(3)よりなる印刷工程により前記基板上へラインもしくはスペース最小幅が1から50μmであり、印刷位置精度が100ppm以下の機能性膜の形成を行うことを特徴とする電界効果トランジスタの製造方法としたもの。

工程(1) 版の画線部に相当する溝構造部にドクターブレードを用いたインキング法で、機能性材料が溶媒へ溶解もしくは分散した薬液を充填する工程。

工程(2) 転写シリンダーと前記版を接触させ、前記溝構造部の薬液を前記転写シリンダーへ転移させる工程。

工程(3) 前記転写シリンダー上の薬液を前記基板の所定の位置へ転写し、機能性膜の形成を行う工程。

(もっと読む)

薄膜トランジスタアレイ、表示装置、およびそれらの製造方法

【課題】本発明は、開口率を大きくする必要がなく、印刷に適し、複数画素を用いずに面積階調できる薄膜トランジスタアレイ、表示装置、および薄膜トランジスタアレイの製造方法を提供する。

【解決手段】画素の有効領域の幅をA、画素の有効領域のネガパターンの幅をBとしたとき、幅Bが幅Aよりも大きな薄膜トランジスタとする。あるいは、対向電極と画素電極の距離をCとしたとき、距離Cが幅Bの4分の1以上B以下である表示装置とする。

(もっと読む)

フレキシブルデバイス用基板及びその製造方法

【課題】フレキシブルデバイス用基板であって、膜厚を非常に薄くしても断線等による電気的性質の低下が抑えられ、それにより歩留まりの向上した基板を提供する。

【解決手段】基材2と、前記基材2上に形成され、ポリイミドを含む平坦化層3とを有し、該平坦化層3表面の測定領域10μm角での表面粗さRaが5nm以下であり、かつ該平坦化層3表面の測定領域1μm角での表面粗さRaが5nm以下であるフレキシブルデバイス用基板1。ポリイミドの数平均分子量が2,000〜1,000,000であることが好ましい。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに画像表示装置

【課題】薄膜トランジスタにおいて、ゲート絶縁膜に直接ストライプ状に凹部を形成することで隔壁形成プロセスを省き、前記凹部をガイドとして塗布法により精度よく半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタの構造を提供する。また、その構造を用いた薄膜トランジスタの製造方法、及びそれを用いたが画像表示装置を提供すること。

【解決手段】基板と、前記基板上に形成されたゲート電極と、前記基板上及び前記ゲート電極上のゲート絶縁体層と、前記ゲート絶縁体層に形成された凹部と、前記絶縁体層の凹部内に形成される半導体層と、前記半導体層上の中央部に設けられる保護膜と、前記半導体層の両端部で接続されるソース電極とドレイン電極と、を有する薄膜トランジスタにおいて、前記ゲート絶縁体層の凹部がストライプ状に形成されていることを特徴とする薄膜トランジスタとする。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】隔壁形成プロセスを省き、かつ、塗布法により半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタを提供する。

【解決手段】基板上に形成された梯子状の凸部を有するゲートバス電極と、ゲートバス電極の表面形状に沿うように当該ゲートバス電極上および基板上に形成されたゲート電極と、ゲート電極の凹凸に沿うようにゲート電極上および基板上に形成されたゲート絶縁体層と、ゲート絶縁体層の凹部内に形成された半導体層と、半導体層の中央に形成された保護膜と、半導体層の両端部で接続されたソース電極とドレイン電極とを備える。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】十分なキャパシタ容量が得られ、リーク電流や寄生容量を抑制した薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】薄膜トランジスタを備え、そのゲート電極111、ソース電極131、ドレイン電極132、バス配線、画素電極133、ゲート絶縁膜121、層間絶縁膜122、半導体層141の全部もしくは一部が塗布法もしくは印刷法で形成されてなり、ゲート絶縁膜121および/もしくは層間絶縁膜122が連続膜から構成され、連続膜が薄膜部と厚膜部から構成されてなる。

(もっと読む)

電界効果型トランジスタ、表示素子、画像表示装置、及びシステム

【課題】低コストで、後工程にて形成される上層の塗布性に優れ、かつ高信頼性を示す電界効果型トランジスタなどの提供。

【解決手段】絶縁性基板と、前記絶縁性基板上に形成されたゲート電極と、前記ゲート電極上に形成されたゲート絶縁層と、前記ゲート絶縁層上に形成されたソース電極及びドレイン電極と、前記ゲート絶縁層上に形成され、かつ、少なくとも前記ソース電極及び前記ドレイン電極との間に形成された酸化物半導体層と、前記酸化物半導体層を被覆するように形成された保護層とを有し、前記保護層が、フッ素樹脂を含有し、前記保護層形成後の前記保護層の水に対する接触角が、75°以上90°以下である電界効果型トランジスタである。

(もっと読む)

半導体装置

【課題】微細化が容易で、短チャネル効果が生じにくい半導体装置を提供する。

【解決手段】トランジスタのチャネル長方向の断面形状において、アスペクト比の大きいゲート電極上に半導体層を形成することで、トランジスタを微細化しても短チャネル効果が生じにくいチャネル長を確保できる。また、半導体層と重畳し、ゲート電極より下層に絶縁層を介して下部電極を設ける。下部電極と重畳する半導体層は、下部電極の電位(電界)により導電型が付与され、ソース領域及びドレイン領域が形成される。半導体層の、ゲート絶縁層を介してゲート電極と対向する領域は、ゲート電極がシールドとして機能し、下部電極の電界の影響を受けない。すなわち、不純物導入工程を用いることなく、自己整合によりチャネル形成領域、ソース領域及びドレイン領域を形成することができる。これにより、微細化が容易で、短チャネル効果が生じにくい半導体装置が実現できる。

(もっと読む)

半導体装置

【課題】トランジスタのサイズを縮小しつつ、良好なスイッチング特性を有する半導体装置を提供する。

【解決手段】一対の第1の突起と、一対の第1の突起の間に設けられる第2の突起とを有するゲート電極と、ゲート電極を覆うゲート絶縁膜と、ゲート絶縁膜と接して、且つ一対の第1の突起および第2の突起に重畳する半導体膜と、半導体膜と接して、且つ一対の第1の突起と重畳する一対の電極と、を有し、半導体膜の側端は、半導体膜のチャネル幅方向において、一対の第1の突起の頂面より外側であり、一対の電極の側端は、半導体膜のチャネル幅方向において、一対の第1の突起の頂面より外側である半導体装置である。

(もっと読む)

電界効果型トランジスタ

【課題】駆動時の発熱温度を低下させる。

【解決手段】基板12の熱伝導率をNsub(W/mK)とし、熱拡散層14の熱伝導率をNkaku(W/mK)とし、熱拡散層14の膜厚をT(mm)とし、熱拡散層14の平面開口率をR(0≦R≦1)とし、S=T×Rとしたとき、例えば、基板12の熱伝導率Nsubが、Nsub<1.8の条件を満たし、熱拡散層14の熱伝導率Nkakuが、Nkaku>3.0×S^(−0.97×e^(−1.2×Nsub))且つNkaku≧Nsubの条件を満たす。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

201 - 220 / 2,712

[ Back to top ]