Fターム[5F110EE42]の内容

Fターム[5F110EE42]の下位に属するFターム

Fターム[5F110EE42]に分類される特許

161 - 180 / 2,712

表示装置

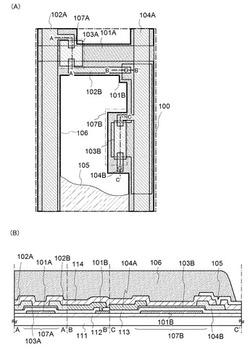

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上

を図ることのできる発光表示装置を提供することを課題の一とする。

【解決手段】薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は、走査

線として機能する第1の配線に電気的に接続されており、薄膜トランジスタは、第1の配

線上にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は、第1

の配線が設けられた領域をはみ出て設けられており、発光素子と、酸化物半導体層とが重

畳して設けられる。

(もっと読む)

半導体装置の作製方法

【課題】基板の大面積化を可能とするとともに、特性の改善された酸化物半導体層を形成し、所望の高い電界効果移動度を有するトランジスタを製造可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを課題の一つとする。

【解決手段】絶縁表面を有する基板上にゲート電極層を形成し、ゲート電極層上にゲート絶縁層を形成し、ゲート絶縁層上に酸化物半導体層を形成し、酸化物半導体層上にソース電極層及びドレイン電極層を形成し、酸化物半導体層、ソース電極層、及びドレイン電極層上に酸素を含む絶縁層を形成し、酸素を含む絶縁層上に水素を含む絶縁層を形成した後、熱処理を行うことにより、水素を含む絶縁層中の水素を少なくとも酸化物半導体層に供給することを特徴とする半導体装置の作製方法である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

半導体装置、表示モジュール、及び電子機器

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

大きい仕事関数および高い電気伝導度を有する電極を具備した電子素子

【課題】大きい仕事関数および高い電気伝導度を有する電極を具備した電子素子を提供する。

【解決手段】0.1S/cm以上の電気伝導度を有する導電性物質および低表面エネルギー物質を含み、第1面と、前記第1面に対向する第2面と、を有し、前記第2面の低表面エネルギー物質の濃度が、前記第1面の低表面エネルギー物質の濃度より高く、前記第2面の仕事関数が5.0eV以上であり、かつ前記第2面の電気伝導度が1S/cm以上である大きい仕事関数および高い電気伝導度を有する電極、を具備した電子素子である。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

酸化物半導体素子、酸化物半導体素子の製造方法、酸化物半導体素子を含む表示装置、及び酸化物半導体素子を含む表示装置の製造方法

【課題】酸化物半導体素子、酸化物半導体素子の製造方法、酸化物半導体素子を含む表示装置、及び酸化物半導体素子を含む表示装置の製造方法を提供すること。

【解決手段】酸化物半導体素子は、基板上に配置されるゲート電極と、リセス構造を含むゲート絶縁層と、ゲート絶縁層の一側上に配置されるソース電極と、ゲート絶縁層の他側上に配置されるドレーン電極と、ゲート絶縁層、ソース電極、及びドレーン電極上に配置されるアクティブパターンとを含むようにすることができる。リセス構造はゲート電極の上部に位置するようにすることができ、アクティブパターンはリセス構造を埋め立てるようにすることができる。酸化物半導体素子がリセス構造を有するゲート絶縁層を具備することによって、電荷移動度、閾値電圧分布、動作電流などの多様な電気的特性を向上させることができる。

(もっと読む)

半導体素子および電子機器

【課題】有機半導体層の上面の層の形状不良を抑えることが可能な半導体素子およびこれを備えた電子機器を提供する。

【解決手段】有機半導体層と、有機半導体層の上面に設けられた層とを有し、この層の外形線は、有機半導体層の外形線よりも内側にある半導体素子。この半導体素子を備えた電子機器。

(もっと読む)

アレイ基板及びその製造方法

【課題】アレイ基板及びその製造方法を提供する。

【解決手段】本発明による製造方法は、基板に無機材料の突起を形成するステップと;それぞれ第一透明導電層と第一金属層からなる反射領域パターン、ゲートライン及びゲートラインから分岐して出されるゲート電極と共通電極を形成するステップと;半導体層からなる活性化ランドパターンと第二金属層からなるデータラインパターンを形成し、活性化ランドパターン上でデータラインに接続されるソース電極とドレイン電極、及び半導体層からなるチャネルを形成するステップと;基板に無機材料を塗布し、無機材料に対して焼き戻し工程を行って一平坦層を形成し、ドレイン電極にビアホールを形成するステップと;反射領域に、ビアホールを介してドレイン電極に接続され且つ第二透明導電層からなる画素電極を形成するステップと、を有する。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】チャネルとなるナノワイアの周囲をゲート電極が取り巻いて形成されているFETが、より容易に高い精度で製造できるようにする。

【解決手段】被覆ナノワイア103を配置した基板121のゲート電極形成領域の上に、被覆ナノワイア103に交差して下部ゲート電極122に重なる上部ゲート電極124を形成する。上部ゲート電極124の形成は、公知のリソグラフィー技術とリフトオフとにより行えばよい。例えば、被覆ナノワイア103が下部ゲート電極122と交差して配置されている基板121の上に、電子ビーム露光により電極形成部に開口を備えるレジストパターンを形成し、この上に、電極材料を堆積する。この後、先に形成してあるレジストパターンを除去すれば、上部ゲート電極124が形成できる。

(もっと読む)

半導体装置の作製方法

【課題】チャネル形成領域が形成される半導体層のチャネル形成領域と逆側近傍の加工方法を工夫した半導体装置の作製方法を提供する。

【解決手段】少なくとも結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、少なくとも第1のエッチングと第2のエッチングを行い、第1のエッチングは非晶質半導体膜の一部を残存させつつ行い、第2のエッチングは非晶質半導体膜上の被覆膜を除去させた後に、非晶質半導体膜に対するエッチングレートが高く、且つ結晶性半導体膜に対するエッチングレートが低い条件により行い、積層半導体膜に設けられた結晶性半導体膜の一部を露出させる。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート

電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第

2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジ

スタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトラ

ンジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

薄膜トランジスタ

【課題】高移動度の薄膜トランジスタ、その製造方法及びその製造に用いるスパッタリングターゲットを提供する。

【解決手段】元素In,Ga及びZnを下記領域1、2又は3の原子比の範囲で含む酸化物を活性層とし、電界効果移動度が25cm2/Vs以上である薄膜トランジスタ。

領域1

0.58≦In/(In+Ga+Zn)≦0.68

0.15<Ga/(In+Ga+Zn)≦0.29

領域2

0.45≦In/(In+Ga+Zn)<0.58

0.09≦Ga/(In+Ga+Zn)<0.20

領域3

0.45≦In/(In+Ga+Zn)<0.58

0.20≦Ga/(In+Ga+Zn)≦0.27

(もっと読む)

表示装置の作製方法

【課題】表示装置の作製工程で紫外線の照射を行っても、酸化物半導体層を用いた薄膜ト

ランジスタのしきい値電圧のシフトを低減させることができる、表示装置の作製方法を提

供することを課題の一つとする。

【解決手段】少なくとも一回以上の紫外線の照射を行い、且つ酸化物半導体層を有する薄

膜トランジスタをスイッチング素子として用いる、表示装置の作製方法において、全ての

紫外線照射工程を終えた後で、紫外線照射による該酸化物半導体層のダメージを回復させ

る熱処理を行う表示装置の作製方法である。

(もっと読む)

コンパレータ、及びそれを用いた半導体装置

【課題】新たな構成のチョッパ型のコンパレータを提供する。

【解決手段】コンパレータは、インバータと、容量素子と、第1のスイッチと、第2のスイッチと、第3のスイッチとを有し、インバータの入力端子と出力端子とは、第1のスイッチを介して電気的に接続され、インバータの入力端子は、容量素子の一対の電極のうちの一方と電気的に接続され、容量素子の一対の電極のうちの他方は、第2のスイッチを介して参照電位が与えられ、入力された信号電位は第3のスイッチを介して容量素子の一対の電極のうちの他方に与えられ、インバータの出力端子から出力される電位を出力信号とし、第1のスイッチは、チャネルが酸化物半導体層に形成されるトランジスタを用いて構成される。

(もっと読む)

薄膜素子組立体

【課題】巻き取りを行っても傷や損傷が発生し難い構成、構造を有する薄膜素子組立体を提供する。

【解決手段】薄膜素子組立体にあっては、可撓性を有する基材20の第1面21上に複数の薄膜素子10が備えられており、基材20において、複数の薄膜素子10が備えられた第1領域の外側に、薄膜素子を備えていない第2領域が設けられており、基材20の第1面21の第2領域、又は、第2面22の第2領域、又は、第1面21及び第2面22の第2領域に凸部31が形成されている。

(もっと読む)

半導体記憶装置

【課題】不揮発性の記憶装置を有するCAMとする際に、メモリセルの低消費電力化を図ることのできる半導体記憶装置を提供することを課題の一とする。また、データの書き込みを繰り返し行う際の劣化をなくすことができる半導体記憶装置を提供することを課題の一とする。また、メモリセルの高密度化が可能な不揮発性の記憶装置を提供する。

【解決手段】酸化物半導体を半導体層に有する第1のトランジスタ及び当該第1のトランジスタをオフ状態とすることで書き込んだデータに対応する電位を保持できる容量素子を有するメモリ回路と、書き込んだ電位を参照するための参照回路を有し、参照回路を構成する第2のトランジスタの導通状態を検出することで、整合するデータのアドレスを取得し、高速な検索機能を可能にした半導体記憶装置である。

(もっと読む)

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

【課題】印刷可能半導体素子を製造するとともに、印刷可能半導体素子を基板表面上に組み立てるための方法及びデバイス、及び伸張形態で良好な性能が得られる伸縮可能な半導体構造及び伸縮可能な電子デバイスを提供する。

【解決手段】予め歪みが加えられた拡張状態の弾性基板が与えられる。印刷可能な半導体構造の内面の少なくとも一部を、予め歪みが加えられた拡張状態の弾性基板の外面に対して結合される。半導体構造の内面を湾曲させることにより弾性基板を少なくとも部分的に緩和状態へと弛緩させる。湾曲した内面を有する半導体構造が弾性基板から他の基板、好ましくはフレキシブル基板へと転写される。

(もっと読む)

薄膜トランジスタ基板の製造方法およびトップゲート構造薄膜トランジスタ基板

【課題】本発明は、簡便な工程で製造可能な、電荷注入効率に優れた薄膜トランジスタ基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、基板上に金属電極層を形成する金属電極層形成工程と、上記金属電極層の上面に、電子吸引性または電子供与性の官能基を有する表面処理剤で表面処理を行うことにより、表面処理層積層体を形成する表面処理工程と、上記表面処理層積層体をパターニングし、ソース電極およびドレイン電極を形成するパターニング工程と、上記ソース電極および上記ドレイン電極上に有機半導体層を形成する有機半導体層形成工程と、上記有機半導体層上にゲート絶縁層を形成するゲート絶縁層形成工程と、上記ゲート絶縁層上にゲート電極を形成するゲート電極形成工程と、を有することを特徴とする薄膜トランジスタ基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

161 - 180 / 2,712

[ Back to top ]