Fターム[5F110GG03]の内容

Fターム[5F110GG03]に分類される特許

141 - 160 / 1,130

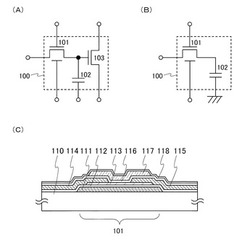

記憶装置、半導体装置

【課題】長い期間においてデータの保持が可能な記憶装置を提供する。

【解決手段】記憶素子と、上記記憶素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタとを有する。上記トランジスタは、通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられており、また、活性層に酸化物半導体を含むためにオフ電流が極めて低い。上記記憶装置では、絶縁膜に囲まれたフローティングゲートに高電圧で電荷を注入するのではなく、オフ電流の極めて低いトランジスタを介して記憶素子の電荷量を制御することで、データの記憶を行う。

(もっと読む)

液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】半導体層205のエッチングと、画素電極210とドレイン電極206bを接続するためのコンタクトホール208の形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように、種結晶上に第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を積層形成する。

(もっと読む)

半導体装置、及びその製造方法

【課題】高品質な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成される半導体領域、半導体領域内に形成され、互いに分離されているソース領域及びドレイン領域、半導体領域内に形成され、ソース領域及びドレイン領域を分離するチャネル領域、チャネル領域上に形成され、1×1019atoms/cm2よりも大きいピーク濃度で、Si、O、またはNとは異なる少なくとも一つの要素を有する界面酸化層、及び界面酸化層上に形成され、実質的に界面酸化層に隣接する深さでhigh―k/界面酸化層接合面を有するhigh―k絶縁層を有するMOS(metal-oxide-semiconductor)トランジスタを備え、少なくとも一つの要素のピーク濃度の少なくとも一つの深さは、実質的にhigh―k/界面酸化層接合面よりも下に位置する。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置

【課題】高集積化を図り、単位面積あたりの記憶容量を増加させた新たな構造の半導体装置を提供することを目的の一とする。高集積化に伴い増加する回路素子数の低減が可能で、かつ、素子数低減による電力削減が可能な、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ビット線と、m(mは3以上の自然数)本のワード線と、ソース線と、m本の信号線と、第1乃至mのメモリセルと、駆動回路と、を有する半導体装置において、メモリセルは、第1のトランジスタ、容量素子に蓄積された電荷を保持する第2のトランジスタを含み、第2のトランジスタは酸化物半導体層で形成されるチャネルを有する。上記構成において、駆動回路は、第j(jは3以上の自然数)の信号線に出力される信号を用いて第(j−1)の信号線に出力される信号を生成する。

(もっと読む)

液晶表示装置

【課題】ソース配線とゲート配線とが製造工程中の静電気によるショートを防止すること

が可能な液晶表示装置の素子構造を提供することを目的とする。

【解決手段】ソース配線が第1の半導体層、第2の半導体層、及び導電層によって構成さ

れる。そして、ソース配線とゲート配線の交差部において、ソース配線の端部の導電層を

除去して、半導体層がはみ出した形状とする。なお、ゲート配線、第1の半導体層、第2

の半導体層、及び導電層の材料はTFTを形成するために用いた材料と同一の材料からな

る。

(もっと読む)

半導体装置の作製方法

【課題】金属元素を用いた結晶化法において、ゲッタリングのために必要な不純物元素の濃度が高く、その後のアニールによる再結晶化の妨げとなり問題となっている。

【解決手段】

本発明は半導体膜に、希ガス元素を添加した不純物領域を形成し、加熱処理およびレーザアニールにより前記不純物領域に半導体膜に含まれる金属元素を偏析させるゲッタリングを行なうことを特徴としている。そして、半導体膜が形成された基板(半導体膜基板)の上方または下方からレーザ光を照射してゲート電極を加熱し、その熱によってゲート電極の一部と重なる不純物領域を加熱する。このようにして、ゲート電極の一部と重なる不純物領域の結晶性の回復および不純物元素の活性化を行なうことを可能とする。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】専有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、該記憶ゲートを絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1及び第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された読み出し信号線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を形成した後、種結晶上に、第2の条件により種結晶の混相粒を成長させて混相粒の隙間を埋めるように、種結晶上に微結晶半導体膜を積層形成する。第1の条件は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を1333Paより大きく13332Pa以下とする条件である。第2の条件は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を100倍以上2000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を1333Pa以上13332Pa以下とする条件である。

(もっと読む)

デバイスの製造方法

【課題】基板側面に付着した異物の効率的な除去が可能な、デバイスの製造方法を提供する。

【解決手段】基板10Aの側面に保護材3を形成する工程と、基板10Aの少なくとも一方の主面に機能層4Aを形成する工程と、保護材3を基板10Aから剥離する工程と、

を有することを特徴とする、デバイスの製造方法。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】単結晶半導体層のテーパー形状を有する端部の特性を良好にすることを課題とする。

【解決手段】加速されたイオンを単結晶半導体基板に照射することによって、単結晶半導体基板中に脆化領域を形成し、単結晶半導体基板とベース基板とを、絶縁膜を介して貼り合わせ、脆化領域において単結晶半導体基板を分離して、ベース基板上に絶縁膜を介して第1の単結晶半導体層を形成し、第1の単結晶半導体層に対してドライエッチングを行って、端部の形状がテーパー形状である第2の単結晶半導体層を形成し、第2の単結晶半導体層の端部に対して、ベース基板側の電位を接地電位としたエッチングを行う。

(もっと読む)

EL表示装置の作製方法

【課題】画素構造を最適化することにより、開口率を向上させたEL表示装置を提供する。

【解決手段】スイッチング用TFTのゲート電極に近接して設けられた半導体層と、電流制御用TFTのゲート電極に近接して設けられた半導体層と、スイッチング用TFTのゲート電極および電流制御用TFTのゲート電極と同一面上に設けられたソース配線と、スイッチング用TFTのゲート電極、電流制御用TFTのゲート電極、およびソース配線を覆う絶縁膜と、ソース配線および前記スイッチング用TFTの半導体層に電気的に接続された第1の接続配線と、電流制御用TFTのゲート電極および前記スイッチング用TFTの半導体層に電気的に接続された第2の接続配線と、電流制御用TFTの半導体層と電気的に接続された画素電極と、発光層と、画素電極と対向する電極とを有するEL素子とを有するEL表示装置。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】メモリセルアレイを構成する複数のメモリセルが、複数行ごとに複数のブロックに分割され、共通ビット線は、各ブロックにおいて、選択トランジスタを介して分割ビット線と電気的に接続されており、メモリセルの一は、第1のチャネル形成領域を含む第1のトランジスタと、第2のチャネル形成領域を含む第2のトランジスタと、容量素子と、を有し、ソース線は、第1のソース電極と接続され、分割ビット線は、第1のドレイン電極および第2のソース電極と接続され、ワード線は、容量素子の電極の一方と接続され、信号線は、第2のゲート電極と接続され、第1のゲート電極と、第2のドレイン電極と、容量素子の電極の他方とが接続される半導体装置を提供する。

(もっと読む)

半導体膜の作製方法、半導体装置の作製方法、及び光電変換装置の作製方法

【課題】抵抗率の低い不純物元素を有する非晶質半導体を形成する。また、電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】プラズマCVD法により不純物元素を有する非晶質半導体を形成する方法において、パッシェンの法則で最小放電開始電圧を満たす圧力及び電極間隔において、パルス変調した放電開始電圧を電極に印加することより、抵抗率の低い不純物元素を有する非晶質半導体を形成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】半導体領域または導電領域を被覆する絶縁膜に、溝及び該半導体領域または導電領域に達するコンタクトホールの少なくともいずれかを形成し、溝及びコンタクトホールの少なくともいずれかに第一の導電膜を形成し、酸化性ガス及びハロゲン系ガスの混合ガスから生成するプラズマに暴露した後、水を含む雰囲気に暴露して、第一の導電膜の一部または全部を流動化し、その後、第一の導電膜上に第二の導電膜を形成する。

(もっと読む)

配線基板、半導体装置、及びそれらの作製方法

【課題】集積化が進む配線基板、又は半導体装置において、導通不良を軽減する。信頼性の高い配線基板、又は半導体装置を歩留まり良く作製する。

【解決手段】多層配線構造を有する配線基板、又は半導体装置において、該配線に用いる導電層の接続構造に曲面を有する導電層を用いる。周囲の絶縁層の除去によって露出された下層の導電層の先端部は曲面であり、下層の導電層上に積層する上層の導電層の被覆性を良好とすることができる。曲面な表面を有するレジストマスクを用いて導電層をエッチング加工することによって曲面な表面を有する導電層を形成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタと第2のトランジスタを有し、第1のトランジスタと第2のトランジスタとは少なくとも一部が重畳する第1のメモリセルと、第3のトランジスタと第4のトランジスタを有し、第3のトランジスタと第4のトランジスタとは少なくとも一部が重畳する第2のメモリセルと、駆動回路と、を有し、第2のメモリセルは、第1のメモリセル上に設けられ、第1のトランジスタは、第1の半導体材料を含んで構成され、第2のトランジスタ、第3のトランジスタ、および第4のトランジスタ、は、第2の半導体材料を含んで構成される半導体装置である。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を形成した後、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように、種結晶上に微結晶半導体膜を積層形成する。第1の条件は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を67Pa以上1333Pa以下とする条件である。第2の条件は、シリコンまたはゲルマニウムを含む堆積性気体と、水素との流量比を周期的に増減させながら処理室に供給し、且つ処理室内の圧力を1333Pa以上13332Pa以下とする条件である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】n型及びp型の少なくともいずれかの不純物が添加された不純物領域を有する半導体膜と、配線とを有し、配線は、導電性を有する金属酸化物を含む拡散防止膜と、該拡散防止膜上の低抵抗導電膜とを有し、配線と半導体膜とのコンタクト部において、拡散防止膜と不純物領域とが接する。拡散防止膜は、導電膜を酸化性ガス及びハロゲン系ガスの混合ガスから生成されるプラズマに暴露して該導電膜に含まれる金属材料の酸化物を形成し、金属材料の酸化物が形成された導電膜を、水を含む雰囲気に暴露して導電膜を流動化させ、流動化した導電膜を固化することで形成する。

(もっと読む)

141 - 160 / 1,130

[ Back to top ]