Fターム[5F110GG03]の内容

Fターム[5F110GG03]に分類される特許

161 - 180 / 1,130

半導体基板、ナノワイヤトランジスタ及びその製造方法

【課題】従来よりも電気的信頼性を向上できる半導体基板、ナノワイヤトランジスタ及びその製造方法を提案する。

【解決手段】シリコン層5と埋め込み酸化膜3との間にシリコン窒化膜4を形成することにより、熱酸化の際に、耐酸化性膜によりシリコン基板表面6にまで酸素が到達することを妨げることで、シリコン基板表面6に酸化シリコンが形成され難くなり、その分だけ当該酸化シリコンの体積膨張を抑制して、チャネル層形成時のストレスを制御できることで、当該ストレスによるナノワイヤ13の意図しない変形又は当該変形によるナノワイヤ13の断線を防止でき、かくして、従来よりも電気的な信頼性及び特性の低下を防止できる。

(もっと読む)

半導体基板の作製方法、及び半導体装置の作製方法

【課題】絶縁表面に欠陥の少ない単結晶半導体膜を有する半導体基板の、簡便な作製方法を提供することを課題の一つとする。また、歩留まりの良い半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】単結晶半導体基板の表面に絶縁層を形成し、絶縁層をエッチングしながら、絶縁層を介して単結晶半導体基板にイオン照射を行うことで、脆化領域を形成し、単結晶半導体基板の表面に接合層を形成し、単結晶半導体基板と、支持基板とを、接合層を介して貼り合わせ、熱処理を行うことにより、脆化領域内に劈開面を形成して、単結晶半導体基板の一部を分離する、半導体基板の作製方法を提供する。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ、および表示装置

【課題】信頼性を向上させると共に、電気的特性を改善することができる薄膜トランジスタの製造方法を提供する。

【解決手段】ガラス基板11上に成膜された非晶質シリコン膜20に、ガラス基板11の裏面側からレーザ光を照射することによって、縦成長モードで多結晶シリコン膜30を形成する。多結晶シリコン膜30は、溶融した半導体の表面に高い密度で形成された種結晶からガラス基板11側に向かって固化することにより形成される。これにより、多結晶シリコン膜30の表面付近には、微結晶シリコン領域を多く含む不完全結晶層32が形成される。そこで、不完全結晶層32をエッチングにより除去して、多結晶シリコン膜33を形成し、多結晶シリコン膜33を活性層とするTFTを製造する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを各々含む複数のメモリセルをマトリクス状に配置し、メモリセルの一と他のメモリセルとを接続する配線(ビット線とも呼ぶ)と、第1のトランジスタにおけるソース領域またはドレイン領域と、が、導電層および第2のトランジスタにおけるソース電極またはドレイン電極を介して電気的に接続した構成とした半導体装置を提供する。これにより、第1のトランジスタにおけるソース電極またはドレイン電極と、第2のトランジスタにおけるソース電極またはドレイン電極と、をそれぞれ異なる配線に接続する場合と比較して配線の数を削減することができるため、半導体装置の集積度を向上させることができる。

(もっと読む)

記憶装置、半導体装置

【課題】データを保持する期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置の提案を目的の一とする。

【解決手段】記憶素子と、記憶素子における電荷の蓄積、保持、放出を制御するための、酸化物半導体を活性層に含むトランジスタと、記憶素子に接続された容量素子とを有する記憶装置。上記容量素子が有する一対の電極の少なくとも一方は、遮光性を有している。さらに、上記記憶装置は遮光性を有する導電膜或いは絶縁膜を有しており、上記活性層が、遮光性を有する電極と、遮光性を有する導電膜或いは絶縁膜との間に位置する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

面エピ形状とソース/ドレインの部分的に覆われるシリサイド周辺とに関するフィンフェット

【課題】低い寄生抵抗(例えば、Rpara)および/または高い駆動電流の改善された特性を有するフィンフェットを提供する。

【解決手段】フィンフェット100およびフィンフェットの製造方法が提供される。フィンフェットは、半導体基板106上に、2つまたは複数のフィン102,104と、前記フィンの側面に設けられるエピタキシャル層108,110と、前記エピタキシャル層の表面上を覆うように設けられる金属−半導体化合物112,114とを備える。フィンは、前記半導体基板の表面上に対して実質的に垂直な側面を有する。前記エピタキシャル層は、前記フィンの側面に対して斜角を有して延設される表面を有する。フィンフェットは、前記金属−半導体化合物上に設けられるコンタクト116を含み得る。

(もっと読む)

積層型半導体装置

【課題】小型、簡単構造でかつ高性能な積層型電界効果トランジスタからなる積層型半導体装置を提供する。

【解決手段】第一の電極1eと第二の電極2eの間で、且つ第一の半導体層1s内に形成されるチャネル領域により構成される第一の電界効果トランジスタ11と、第四の電極4eと第五の電極5eの間で、且つ第二の半導体層2s内に形成されるチャネル領域により構成される第二の電界効果トランジスタ12と、が積層され、第三の電極3eが第一の半導体層1s、第二の半導体層2sのゲート電極であり、第一の電極1eが第一の半導体層1sのソース電極、第二の電極2eが第一の半導体層1sのドレイン電極であり、第四の電極4eが第二の半導体層2sのソース電極、第五の電極が第二の半導体層2sのドレイン電極であって、第一の電界効果トランジスタ11の導電型と第二の電界効果トランジスタ12の導電型が異なるCMOS回路を構成する。

(もっと読む)

半導体装置

【課題】貫通電流を低減させることができる相補型の論理回路を用いることで、消費電力を抑えることができる半導体装置の提案を目的の一とする。或いは、貫通電流を低減させることができる相補型の論理回路を用いることで、発熱を抑えることができる半導体装置の提案を目的の一とする。

【解決手段】通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられたnチャネル型トランジスタ、或いはpチャネル型トランジスタを、相補型の論理回路に用いる。そして、オフ電流が極めて小さい絶縁ゲート電界効果型トランジスタをスイッチング素子として用い、上記第2のゲート電極の電位を制御する。上記スイッチング素子として機能するトランジスタは、シリコン半導体よりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料を、チャネル形成領域に含む。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する第1の微結晶半導体膜を酸化絶縁膜上に形成した後、第2の条件により混相粒を結晶成長させて混相粒の隙間を埋めるように、第1の微結晶半導体膜上に第2の微結晶半導体膜を積層形成する。第1の条件は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量比を50倍以上1000倍以下にして堆積性気体を希釈し、処理室内の圧力を67Pa以上1333Pa以下とする条件であり、第2の条件は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量比を100倍以上2000倍以下にして堆積性気体を希釈し、処理室内の圧力を1333Pa以上13332Pa以下とする条件である。

(もっと読む)

半導体装置とその製造方法

【課題】良好な特性を有し且つ微細化を実現した半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、平面状シリコン層212上の柱状シリコン層208、柱状シリコン層208の底部領域に形成された第1のn+型シリコン層113、柱状シリコン層208の上部領域に形成された第2のn+型シリコン層144、第1及び第2のn+型シリコン層113,144の間のチャネル領域の周囲に形成されたゲート絶縁膜140、ゲート絶縁膜140の周囲に形成され第1の金属シリコン化合物層159aを有するゲート電極210、ゲート電極210と平面状シリコン層212の間に形成された絶縁膜129a、柱状シリコン層208の上部側壁に形成された絶縁膜サイドウォール223、平面状シリコン層212に形成された第2の金属シリコン化合物層160、及び第2のn+型シリコン層144上に形成されたコンタクト216を備える。

(もっと読む)

半導体基板、半導体装置、および半導体装置の製造方法

【課題】半導体装置の製造工程において、十分にゲッタリング効果を得ることができる半導体基板を提供する。

【解決手段】半導体からなる基板本体8と、前記基板本体8上に形成されたリンを含有したシリコン酸化膜からなる絶縁層6と、該絶縁層6上に設けられた半導体層7と、を備えることを特徴とする半導体基板3を提供する。また、半導体からなる基板本体8と、前記基板本体8上に形成されたリンを含有したシリコン酸化膜からなる絶縁層6と、該絶縁層6上に設けられた半導体層7を備える半導体基板3と、前記半導体層7上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記半導体層7内であって、前記ゲート電極に対して自己整合となる位置に設けられた不純物拡散領域と、を有することを特徴とする半導体装置を提供する。

(もっと読む)

微結晶半導体膜の作製方法及び半導体装置の作製方法

【課題】良質な微結晶半導体膜を形成することが可能な複数の結晶核を生成し、該複数の結晶核を成長させる微結晶半導体膜の作製方法を提供することを課題とする。

【解決手段】微結晶半導体膜の作製に際して、連続放電によりプラズマを発生させて複数の結晶核を生成させる第1の工程と、パルス放電によりプラズマを発生させて前記複数の結晶核の間隙を埋める第2の工程と、を行い、前記第2の工程は前記第1の工程の後に行う。前記第1の工程と前記第2の工程は更に複数回繰り返してもよい。

(もっと読む)

半導体表示装置及びその駆動方法

【課題】消費電力の低減を実現することができる、タッチパネルを有する半導体表示装置の提案を課題とする。

【解決手段】画素部、及び、画素部への画像信号の入力を制御する駆動回路が設けられたパネルと、画素部においてパネルと重なる位置に設けられたタッチパネルとを有する。画素部は、入力される画像信号の電圧に従って表示を行う表示素子と、電圧の保持を制御するトランジスタとを有する。トランジスタは、そのチャネル形成領域に酸化物半導体を含んでいる。そして、駆動回路の駆動周波数、すなわち一定期間内における画像信号の書き込み回数を、タッチパネルから入力される操作信号に従って変更する。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置の作製工程数を減少させること、半導体装置の歩留まりを向上させること、半導体装置の作製コストを低減することを課題とする。

【解決手段】基板上に、単結晶半導体層をチャネル形成領域に有する第1のトランジスタと、当該第1のトランジスタと絶縁層を介して分離され、酸化物半導体層をチャネル形成領域に有する第2のトランジスタと、当該単結晶半導体層及び酸化物半導体層を有するダイオードを有する半導体装置、及び、その作製方法に関する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体薄膜基板および半導体薄膜基板を用いた半導体装置の作製方法

【課題】一層の半導体層から膜厚の異なる半導体層を有する半導体薄膜基板を提供することを目的の一とする。または、半導体薄膜基板を適用した半導体装置を提供することを目的の一とする。

【解決手段】基板上に半導体層を形成し、半導体層を加工して第1の島状半導体層および第2の島状半導体層を形成し、第1の島状半導体層にレーザー照射を行うことにより第1の島状半導体層を溶融させ、第1の島状半導体層から第2の島状半導体層より膜厚が厚い第3の島状半導体層を形成する、半導体薄膜基板の作製方法である。

(もっと読む)

成膜方法及び半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供することを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でスパッタリングを行う。

(もっと読む)

結晶化半導体薄膜の製造方法および結晶化半導体薄膜

【課題】アモルファス薄膜の溶融結晶化時に生じる凹凸の影響を受けないようなトップゲート型TFT素子などの作製が可能な結晶化半導体薄膜の製造方法および該凹凸が表面にない結晶化半導体薄膜を提供する。

【解決手段】本発明の結晶化半導体薄膜の製造方法は、第1基板1上層に剥離層2を介して剥離可能に形成したアモルファス半導体薄膜4aを溶融結晶化させ、その後、結晶化した結晶化半導体薄膜4pの表面側を接合面にして接着剤6を介して第2基板5上層に前記結晶化半導体薄膜4pを接合するとともに該結晶化半導体薄膜4pを第1基板側1から剥離する。本発明の結晶化半導体薄膜は、基板上層に設けられた結晶化半導体薄膜であって、該結晶化半導体薄膜は、前記基板上層に接合層を介して接合されており、かつ該接合層に対する接合面側に溶融結晶化に伴う凹凸形状を有する。

(もっと読む)

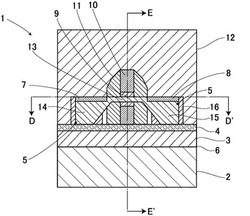

半導体構造体及びその製造方法

【課題】 埋め込み型DRAM構造のための半導体構造体及びその製造方法を提供する。

【解決手段】 ノード誘電体及び深いトレンチを充填する導電性トレンチ充填領域がセミコンダクター・オン・インシュレータ(SOI)層の上面とほぼ同一面となる深さにまで窪まされる。浅いトレンチ分離部が深いトレンチの上部の一方の側に形成され、一方深いトレンチの上部の他方の側は、導電性充填領域の半導体材料の露出された表面となる。選択的エピタキシャル成長プロセスが、レイズド・ソース領域及びレイズド・ストラップ領域を付着するために行われる。レイズド・ソース領域は、SOI層内のプレーナ・ソース領域上に直接形成され、そしてレイズド・ストラップ領域は、導電性充填領域上に直接形成される。レイズド・ストラップ領域は、プレーナ・ソース領域及び導電性充填領域の間の導電性通路を与えるためにレイズド・ソース領域に接触する。

(もっと読む)

161 - 180 / 1,130

[ Back to top ]