Fターム[5F110GG03]の内容

Fターム[5F110GG03]に分類される特許

61 - 80 / 1,130

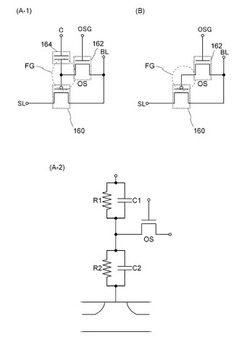

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

【課題】印刷可能半導体素子を製造するとともに、印刷可能半導体素子を基板表面上に組み立てるための方法及びデバイスを提供する。

【解決手段】デバイス、デバイス部品は、幅広いフレキシブル電子デバイス及び光電子デバイス並びにデバイスの配列を高分子材料を備える基板上に形成する。伸張形態で良好な性能が得られる伸縮可能な半導体構造及び伸縮可能な電子デバイスを形成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

半導体装置およびその駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のチャネル形成領域と、第1のゲート電極と、第1のソース領域およびドレイン領域と、を有する第1のトランジスタと、少なくとも第1のソース領域またはドレイン領域の一部と重畳するように設けられた、酸化物半導体材料からなる第2のチャネル形成領域と、第2のソース電極と、第1のゲート電極に電気的に接続される第2のドレイン電極と、第2のゲート電極と、を有する第2のトランジスタと、第1のトランジスタと第2のトランジスタとの間の絶縁層と、を含むメモリセルを有し、第2のトランジスタをオフ状態とすべき期間において、少なくとも第1のソース領域またはドレイン領域に正の電位が与えられるときに第2のゲート電極に負の電位が与えられる半導体装置。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗が小さく高性能なナノワイヤトランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、第1方向に延在するナノワイヤ形状のチャネル領域3と、チャネル領域3を間に挟むように離間して設けられかつチャネル領域3よりも幅が広いソース領域およびドレイン領域8,9と、チャネル領域3、ソース領域およびドレイン領域8,9と基板との間に設けられ膜厚が薄い凹形状の領域を有する絶縁膜2と、チャネル領域3上の半導体層の少なくとも側面に設けられたゲート絶縁膜と、前記ゲート絶縁膜に対して前記第1領域上の前記半導体層と反対側に設けられたゲート電極6と、ゲート電極6の、ソース領域およびドレイン領域8,9に対向する側面に設けられた絶縁体のゲート側壁7と、を備え、半導体層は半導体層直下の前記凹形状の領域の部分に延在している。

(もっと読む)

多層膜構造体及びその形成方法

【課題】新規な多層膜構造体及びその形成方法を提供すること。

【解決手段】半導体素子用の多層膜構造体の形成方法であって、シリコンを含む基板上に、ゲルマニウム錫混晶からなる半導体層を形成する半導体層形成工程と、前記半導体層上に表面保護層を形成する表面保護層形成工程と、前記半導体層に熱処理を施すことにより、前記ゲルマニウム錫混晶と前記シリコンを含む基板との固相反応を進め、シリコンゲルマニウム錫混晶からなる半導体歪印加層を形成する半導体歪印加層形成工程と、前記表面保護層を除去する除去工程と、前記半導体歪印加層の上方に、前記除去工程後に、歪半導体層を積層する積層工程とを含むことを特徴とする多層膜構造体の形成方法。

(もっと読む)

半導体装置

【課題】ソース配線とゲート配線とが製造工程中の静電気によるショートを防止すること

が可能な液晶表示装置の素子構造を提供することを目的とする。

【解決手段】ソース配線が第1の半導体層、第2の半導体層、及び導電層によって構成さ

れる。そして、ソース配線とゲート配線の交差部において、ソース配線の端部の導電層を

除去して、半導体層がはみ出した形状とする。なお、ゲート配線、第1の半導体層、第2

の半導体層、及び導電層の材料はTFTを形成するために用いた材料と同一の材料からな

る。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート

電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第

2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジ

スタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトラ

ンジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】溝部および該溝部を挟んで形成された一対の低抵抗領域を有する半導体基板と、半導体基板上の第1のゲート絶縁膜と、第1のゲート絶縁膜を介し、溝部と重畳するゲート電極と、ゲート電極を覆って設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜上の、溝部を挟んで設けられた一対の電極と、一対の電極と接する半導体膜と、を有し、一対の低抵抗領域の一方と、一対の電極の一方が電気的に接続されている積層されたトランジスタを形成し、一方はn型半導体からなるトランジスタであり、他方はp型半導体からなるトランジスタにより形成させることによって、相補型MOS回路を形成する。

(もっと読む)

二重仕事関数金属ゲート構造体及びその製造方法

【課題】二重金属ゲートを有する構造体において金属膜の仕事関数を調整する為の改善した方法および半導体素子を提供する。

【解決手段】半導体素子は単一金属膜に対し、NMOSにおいてはフッ素、PMOSにおいては炭素をそれぞれ選択的にドーピングすることによって形成される二重仕事関数の金属ゲート電極108’、109’を有する。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】電界効果トランジスタであって、半導体基板10上に垂直に形成され、且つ第1の領域が第2の領域よりも高く形成された半導体フィン31と、第1の領域の両側面にゲート絶縁膜40を介して設けられたゲート電極50と、第2の領域に第1の領域の上端よりも低い位置まで設けられた、合金半導体からなるソース・ドレイン下地層63,73と、下地層63,73上に第1の領域の上部を挟むように設けられた、下地層63,73とは格子定数の異なるソース・ドレイン領域60,70とを備えている。チャネル領域には応力が付与され、下地層63,73は、空乏層が収まる厚さよりも厚く、熱平衡状態で結晶にミスフィット転位が導入される熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

半導体記憶装置

【課題】電力の供給がない状況でも記憶内容の保持が可能かつ、書き込み回数にも制限がない新たな構造の半導体記憶装置を提供する。

【解決手段】第1のトランジスタのソースまたはドレインの一方が第2のトランジスタのソースまたはドレインの一方と接続し、第1のトランジスタのゲートが第3のトランジスタのソースまたはドレインの一方、およびキャパシタを構成する一対の容量電極の一方と接続し、第1のトランジスタのソースまたはドレインの他方および第3のトランジスタのソースまたはドレインの他方がビット線と接続し、第3のトランジスタのゲートがワード線と接続し、第2のトランジスタのゲートおよびソースまたはドレインの他方がソース線と接続し、キャパシタを構成する一対の容量電極の他方が共通配線と接続し、共通配線はGNDに接続し、共通配線は上面から見て網状に設けられ、第3のトランジスタはその網の目に設けられる半導体記憶装置。

(もっと読む)

記憶素子および信号処理回路

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路を提供する。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、アモルファスシリコン、ポリシリコン、微結晶シリコン、あるいは酸化物半導体等の化合物半導体をチャネル形成領域に含み、そのチャネル長が最小加工線幅の10倍以上あるいは、1μm以上であるトランジスタを用いる。上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

ナノワイヤの配列方法、及び分離方法

【課題】所望の長さのナノワイヤを、所望の向き、位置に配列させる方法。

【解決手段】ナノワイヤの配列方法であって、二つの電極を有する基板上に、両末端が互いに異なる二つの極性であるナノワイヤを静置、第1電極に第1極性の電圧を印加し、その反対の第2極性の片末端を第1電極上に固定、第1電極に第1極性の電圧を印加した状態で、第1電極から第2電極に流体を流す、第1電極の電圧を自然電位に設定後、第2極性の電圧を第2電極に印加し、第1極性の片末端を第2電極に固定、第2電極に第2極性の電圧を印加した状態で、第2電極から第1電極に流体を流す、第2電極の電圧を自然電位に設定後、第1電極に第1極性の電圧を印加し、第2極性の片末端を第1電極上に固定、第1電極に第1極性の電圧を印加した状態で、第2電極から第1電極に流体を流す、第1電極に第1極性の電圧を印加した状態で、第1電極から第2電極に流体を流す、を順次行う。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接する、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタを有し、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第1の酸化絶縁膜上に位置する。

(もっと読む)

ナノワイヤの配列方法、及び分離方法

【課題】所定の長さのナノワイヤを所定の向きに、所定の位置に配列させる方法、並びに所定の長さのナノワイヤを分離抽出する方法を提供する。

【解決手段】基板上の所定の位置にナノワイヤを配置するためのナノワイヤの配列方法であって、前記ナノワイヤの両端を固定するための、所定の距離を離間させた対となる固定化部位を設けた基板を作製する工程と、両末端に前記基板上の固定化部位と特異的な結合を形成するための結合部位を有するナノワイヤを作製する工程と、前記ナノワイヤを含有する液を前記基板上に分散させ、前記ナノワイヤの結合部位を前記基板上の固定化部位に結合させる工程と、前記対となる固定化部位の相対する方向に対して略垂直に流体を流す工程とを順次行うことを特徴とする。

(もっと読む)

61 - 80 / 1,130

[ Back to top ]