Fターム[5F110GG58]の内容

Fターム[5F110GG58]に分類される特許

1,781 - 1,790 / 1,790

平面デュアルゲート半導体装置

デュアルゲート半導体装置の製造方法は、シリコン体(16)の第1の表面(14)の一部分上に第1のゲート(12)が形成された後であるが、前記第1の表面の反対側のシリコン体の第2の表面(44)上に第2のゲート(52)を形成する前に行われるソース及びドレインコンタクト領域(34,36)のシリサイド化を備える。第1のゲート(12)はソース及びドレインコンタクト領域がシリコンチャネル(18)に位置合わせされることを保証するマスクの働きをする。さらに、製造の早い段階でシリサイド化を行うことにより、第2のゲートの材料の選択が高温処理により制限されない。シリサイド化によるシリコン体の第2の表面での材料特性の違いがシリサイドのソースコンタクト領域とドレインコンタクト領域との間に前記第2のゲートを横方向に位置合わせされることを可能にすることが有利である。  (もっと読む)

(もっと読む)

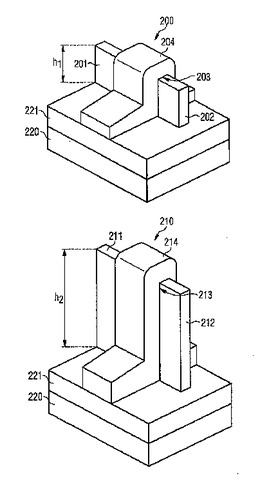

Fin電界効果トランジスタの配列及びFin電界効果トランジスタの配列の形成方法

本発明は、基板と、フィンにおける第1,第2のソース/ドレイン領域の間にチャネル領域が形成され、かつ、フィンの上部にゲート領域が形成されるフィンを有する、上記基板上および/または上記基板中に形成される、第1のFin電界効果トランジスタと、フィンにおける第1,第2のソース/ドレイン領域の間にチャネル領域が形成され、かつ、当該フィンの上部にゲート領域が形成されるフィンを有する、上記基板上および/または上記基板中に形成される、第2のFin電界効果トランジスタとを備えた、Fin電界効果トランジスタ配置に関する。上記第1のFin電界効果トランジスタのフィンの高さは、上記第2のFin電界効果トランジスタのフィンの高さよりも高くなっている。  (もっと読む)

(もっと読む)

溶融技術により有機半導体デバイスを形成する方法

本発明は、有機半導体材料を有する半導体デバイスを形成する方法であって、溶融物を形成するために、有機半導体材料を有する組成物をこの組成物の融点若しくはガラス転移温度に又はそれよりも高い温度に加熱することと、溶融物を組成物の融点又はガラス転移温度よりも低い温度に冷却することとを有し、加熱する前又は加熱中にディウェッティングを抑制及び/又は防止することができる第1の物質若しくは物体が組成物に隣接するか、又は組成物がディウェッティングを抑制及び/又は防止することができる作用物質を更に有する方法を提供する。  (もっと読む)

(もっと読む)

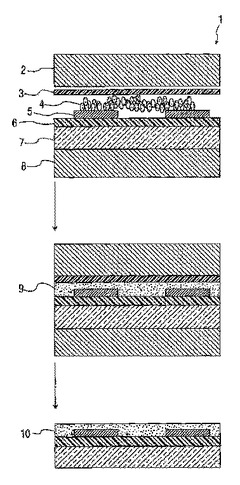

ダイアモンド状のカーボンチャネルを有する電界効果トランジスタの製造方法、及び該製造方法により製造されるトランジスタ

ダイアモンド状のカーボンチャネルを有する電界効果トランジスタの製造方法、及び該製造方法により製造されるトランジスタ。

前記電界効果トランジスタは、ゲート絶縁膜(3)によりチャネル(7)から分離されたゲート電極(5)により制御されるチャネル(7)により接続されるソース(10)及びドレイン(11)を含む。前記チャネル(7)はダイアモンド状のカーボン層により形成される。前記トランジスタの製造方法は、続いて、ダイアモンド状のカーボン層を基板上(2)に堆積させ、ゲート絶縁層(3)を堆積させ、そして、少なくとも1つの導電層(4)を堆積させることを含む。前記導電層(4)は前記ゲート電極(5)からエッチングされる。次に、側面の絶縁膜(6)を形成するために、前記ゲート電極(5)の側面に絶縁材料が堆積される。次に、前記ゲート絶縁層(3)がエッチングされ、そして、前記ダイアモンド状のカーボン層がチャネル(7)の輪郭を描くようにエッチングされる。次に、前記ソース(10)を形成するための半導体材料、及び前記ドレイン(11)を形成するための半導体材料がチャネル(7)の両側に堆積される。  (もっと読む)

(もっと読む)

歪みFINFETチャネルの製造方法

例示的実施形態はFinFETチャネル構造の形成法に関する。当該方法において、絶縁層(130)上に化合物半導体層(140)を提供し、化合物半導体層(140)上にトレンチ(142)を提供し、かつ、化合物半導体層(140)上およびトレンチ(142)内に歪み半導体層(144)を提供する。該方法において、さらに、化合物半導体層(140)上から歪み半導体層(144)を除去し、その結果、トレンチ(142)内に歪み半導体層(144)を残し、化合物半導体層(140)を除去して、歪み半導体層(144)を残し、かつ、フィン形のチャネル領域(152)を形成する。  (もっと読む)

(もっと読む)

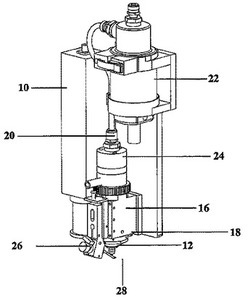

感熱性中規模デポジションのレーザ処理

マスクなし中規模材料デポジション(Maskless Mesoscale Material Deposition, M3DTM)処理のための方法および装置が開示され、これはエアロゾルを作るのに好ましくは超音波トランスデューサまたは圧縮空気噴霧器(22)を用い、このエアロゾルは流入口(20)を経由してフローヘッド(12)に入り、その際に随意的に、ガス量を低減するため事実上のインパクタ(24)ならびに溶剤を除去するまたは粘度を調整するためヒータアセンブリ(18)の両方を、あるいはそのいずれかを経由するようにしてもよい。機械的シャッター(28)のついた材料シャッターアセンブリ(26)が好ましくはフローヘッドの出口についており、鞘状のガスが流入口(18)を通って入り、エアロゾルがフローヘッドから出る前にそれを囲む。熱に弱いターゲットの上のエアロゾルデポジット材料は好ましくはレーザモジュール(10)からのビームで処理し、これによってそのターゲットを損傷閾値以上に加熱することなく、たとえば化学分解、焼結、重合などにより希望の状態を得るためにデポジットした材料を加熱する。1ミクロンの線幅の形状をデポジットすることができる。 (もっと読む)

絶縁構造部上の半導体チャンネル

半導体装置基板上に貫通誘電体層を形成するステップと、貫通誘電体層の上部にトレンチ誘電体層を形成するステップと、貫通誘電体層を露出させるため、トレンチ誘電体層を貫通する溝を形成するステップと、基板を露出させるため、前記溝内の貫通誘電体層に貫通孔を形成するステップと、溝内および前記貫通孔内に半導体材料を形成するステップと、を有する方法を示した。装置基板と、該装置基板の表面に形成された誘電体層と、誘電体層上に形成された、装置基板と相間する結晶構造を有する装置基部と、を有する装置を示した。  (もっと読む)

(もっと読む)

フロントゲート型SOI−MOSFETの製造方法

【課題】ソース/ドレイン拡張とフロントゲート(front gate)に自己整合させたバックゲートを含む、FD型SOI−CMOSデバイスの製造方法に関する。

【解決手段】

SOI−CMOS技術は、ポリシリコン、即ちポリSiバックゲートは、フロントゲート・デバイスの閾値電圧を制御するために使用され、nMOS及びpMOSバックゲートは、互いに独立に、及びフロントゲートと独立に、スイッチされる。

特に、バックゲートが、デバイスのフロントゲート及びソース/ドレイン拡張に自己整合されたバックゲートFD型CMOSデバイスの製造方法を提供する。バックゲートFD型CMOSデバイスは、SIMOX又は結合SOI−ウエハ、ウエハボンディングと薄膜化、ポリSiエッチング、LP−CVD、機械化学研磨(CMP)を用いて製造される。

(もっと読む)

ポリマーデバイスの製造

(i)ポリマーまたはオリゴマーおよび架橋部分を含む溶液を基板上に成膜して層を形成する工程、および(ii)不溶性架橋化ポリマーを形成する条件下で工程(i)で形成された層を硬化する工程を備え、架橋部分が溶液中のポリマーまたはオリゴマーおよび架橋部分の繰返し単位のモル総数に対して0.05から5モル%の範囲の量で工程(i)に存在することを特徴とする、ポリマーデバイスを形成する方法。 (もっと読む)

有機薄膜トランジスタ

【課題】特殊な技術を要せず、簡単な製造方法でキャリア移動度が高い有機薄膜トランジスタを提供すること。

【解決手段】有機半導体層に重量平均分子量2000以上のπ共役系ポリマー及び分子量2000以下のπ共役系オリゴマーを含有することを特徴とする有機薄膜トランジスタ。

(もっと読む)

1,781 - 1,790 / 1,790

[ Back to top ]