Fターム[5F110HJ12]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物領域の製法 (6,364) | 不純物の導入方法 (4,201)

Fターム[5F110HJ12]の下位に属するFターム

Fターム[5F110HJ12]に分類される特許

121 - 140 / 903

表示装置

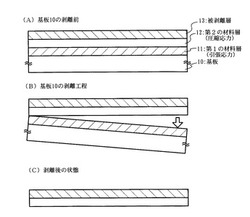

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って歩留まりよく剥離することを可能とすることを目的としている。また、様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。特に、フレキシブルなフィルムにTFTを代表とする様々な素子を貼りつけ、軽量された半導体装置およびその作製方法を提供する。

【解決手段】基板上に第1の材料層11を設け、前記第1の材料層11に接して第2の材料層12を設け、さらに積層成膜または500℃以上の熱処理やレーザー光の照射処理を行っても、剥離前の第1の材料層が引張応力を有し、且つ第2の材料層が圧縮応力であれば、物理的手段で容易に第2の材料層12の層内または界面において、きれいに分離することができる。

(もっと読む)

EL表示装置

【課題】開口率の高い表示装置又は素子の面積の大きい半導体装置を提供することを課題

とする。

【解決手段】隣接する画素電極(又は素子の電極)の間に設けられた配線との下方にマル

チゲート構造のTFTのチャネル形成領域を設ける。そして、複数のチャネル形成領域の

チャネル幅の方向を前記画素電極の形状における長尺方向と平行な方向とする。また、チ

ャネル幅の長さをチャネル長の長さよりも長くすることでチャネル形成領域の面積を大き

くする。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

表示装置及び電子機器

【課題】アクティブマトリクス型基板において、薄膜トランジスタと、その端子接続部を

同時に作り込み、少ないマスク数で歩留まりの良い表示装置を提供する。

【解決手段】画素部および外部入力端子を有する表示装置であって、画素部は、ゲート電

極と、半導体膜と、ゲート電極上に形成された絶縁膜、および絶縁膜上に半導体膜と電気

的に接続された電極を有するTFTを有し、外部入力端子は、ゲート電極と同じ層に形成

された第1の配線と、電極と同じ層に形成され、絶縁膜に形成されたコンタクトホールを

介し第1の配線と接続された第2の配線と、第2の配線に接続され、第2の配線上に形成

された透明導電膜と、第2の配線と透明導電膜が接続している位置で透明導電膜と電気的

に接続するフレキシブルプリント配線板を有する表示装置。

(もっと読む)

半導体装置の作製方法

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成する。

(もっと読む)

レーザ照射装置

【課題】小型のレーザ照射装置で光干渉がなく、連続した結晶成長を実現することである。

【解決手段】メガヘルツレーザビームを用い、分割したレーザビームを半導体膜に照射して、半導体膜を結晶化する。その際に分割ビームに光路差を設けて光干渉を抑える。光路差はメガヘルツレーザビームのパルス幅に相当する長さ以上、パルス発振間隔に相当する長さ未満に設定され、非常に短い光路差で光干渉を抑えることができる。そのためレーザのエネルギー劣化がなく効率的に且つ連続的にレーザビームを照射することができる。

(もっと読む)

液晶表示装置

【課題】動作性能および信頼性の高い液晶表示装置を提供する。

【解決手段】第1のチャネル形成領域713と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域714と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜664と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線668と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線672と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

半導体装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安

価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピン

グ法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時

に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300

℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶

質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

半導体装置

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って剥離することを可能とする。

【解決手段】基板上に金属層を形成する工程と、前記金属層上に酸化物層を形成する工程と、前記酸化物層上に絶縁層を形成する工程と、前記絶縁層上に薄膜トランジスタを形成する工程と、前記薄膜トランジスタ上に発光素子を形成する工程と、人間の手又は前記薄膜トランジスタを引き剥がす装置を用いることにより、前記酸化物層の層内または界面において前記基板から前記薄膜トランジスタを剥離する工程とを有する。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、少ない工程で多層配線化を実現し、小面積で高機能な機能回路を有する配線基板及び半導体装置を提供する。またこのような高機能な機能回路を表示装置と同一基板上に一体形成した半導体装置を提供することを課題とする。

【解決手段】本発明は、絶縁表面を有する基板上に、第1の配線と、第2の配線と、第3の配線と、第1の層間絶縁膜と第2の層間絶縁膜と、第1のコンタクトホールと第2のコンタクトホールを有し、前記第2の配線の幅を前記第1の配線の幅より広いか、あるいは前記第3の配線の幅を前記第1の配線の幅もしくは前記第2の配線の幅より広く、且つ前記第2のコンタクトホールの直径を前記第1のコンタクトホールの直径より大きく形成することを特徴とする。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いる半導体装置において、電気特性の良好な半導体装置を提供する。

【解決手段】基板上に酸化物半導体膜および絶縁膜を有し、酸化物半導体膜の側面は絶縁膜と接しており、酸化物半導体膜は、チャネル形成領域と、チャネル形成領域を挟んで形成されたドーパントを含む領域とを含み、酸化物半導体膜上に接して形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、サイドウォール絶縁膜を有するゲート電極と、酸化物半導体膜、および絶縁膜に接して形成されたソース電極およびドレイン電極とを有する半導体装置である。

(もっと読む)

酸化物半導体素子及び半導体装置

【課題】半導体層に結晶性を有する酸化物半導体を用いた、移動度の高い酸化物半導体素子を提供する。

【解決手段】第1の酸化物半導体膜及び、第1の酸化物半導体膜に接して第1の酸化物半導体膜よりバンドギャップが大きい第2の酸化物半導体膜の積層構造を有する層を酸化物半導体層として用いた。これにより、チャネル領域は、第2の酸化物半導体膜と接する第1の酸化物半導体膜の界面近傍(つまり、バンドギャップが小さい酸化物半導体膜の界面近傍)に形成される。また、第1の酸化物半導体膜と第2の酸化物半導体膜の界面は、お互いの未結合手が結合し合っている。このため、第2の酸化物半導体膜と接する第1の酸化物半導体膜の界面近傍に形成されるチャネル領域では、未結合手による電子トラップなどに起因した移動度の低下を低減できる。

(もっと読む)

半導体装置

【課題】簡素でかつ占有面積の小さな駆動回路を提供すること。

【解決手段】本発明のシフトレジスタ回路は、複数のレジスタ回路を有している。各レジスタ回路は、クロックドインバータ回路およびインバータ回路を有している。クロックドインバータ回路の出力信号がインバータ回路の入力信号となるよう両者が直列に接続されている。さらに、レジスタ回路は、インバータ回路の出力信号が伝達される信号線を有している。該信号線には接続されている素子が多く寄生容量が大きいため高負荷である。本発明のシフトレジスタ回路は、信号線の寄生容量が大きいために高負荷であることを用いている。

(もっと読む)

半導体装置

【課題】同一の層間膜上に画素電極と、ゲート配線を形成した半導体装置において、マス

ク枚数を追加することなく、液晶の焼きつきや特性劣化を低減する。

【解決手段】ゲート配線上に絶縁膜を設けることで、ゲート配線が非選択の期間に液晶に

かかるゲート電圧の絶対値を減少させることができる。絶縁膜は遮光性樹脂膜、柱状スペ

ーサーで形成すると、マスク枚数の増加を抑えることができる。また、絶縁膜上に画素電

極を形成し、ゲート配線と画素電極が重なり合うようにすることで、画素電極の電界遮蔽

効果によって、液晶にかかるゲート電圧を減少させることができる。

(もっと読む)

記憶装置

【課題】誤書込みを防止することが可能な記憶装置を提供する。

【解決手段】複数のメモリセルが直列に接続されたNANDセルユニットと、NANDセルユニットの一方の端子に接続する第1の選択トランジスタと、NANDセルユニットの他方の端子に接続する第2の選択トランジスタと、第1の選択トランジスタと接続するソース線と、該ソース線と交差し、且つ第2の選択トランジスタと接続するビット線とを有し、第1の選択トランジスタ及び第2の選択トランジスタは、チャネル領域が酸化物半導体層で形成されたトランジスタである。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。酸化物半導体層の側壁はサイドウォール絶縁層により覆われている。なお、該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】ノイズによるデータ信号への影響を抑制する半導体記憶装置を提供する。

【解決手段】記憶回路を具備し、記憶回路は、それぞれが電界効果トランジスタであり、1個目の電界効果トランジスタ111a−1のソース及びドレインの一方にデジタルデータ信号が入力され、k個目(kは2以上n(nは2以上の自然数)以下の自然数)の電界効果トランジスタのソース及びドレインの一方がk−1個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続されるn個の電界効果トランジスタと、それぞれ一対の電極を有し、m個目(mはn以下の自然数)の容量素子の一対の電極の一方が、n個の電界効果トランジスタのうち、m個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続され、少なくとも2つの容量素子における容量値が異なるn個の容量素子112aー1〜112aーnとを備える。

(もっと読む)

半導体装置、モジュール及び電子機器

【課題】本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】本発明は、上層と、上層よりも広い幅を有する下層とからなる2層構造とする。TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。上層の端面から突出させた下層部分と、ITOとを接合させる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】基板上に第1の酸化絶縁膜を形成し、該第1の酸化絶縁膜上に第1の酸化物半導体膜を形成した後、加熱処理を行い、第1の酸化物半導体膜に含まれる水素を脱離させつつ、第1の酸化絶縁膜に含まれる酸素の一部を第1の酸化物半導体膜に拡散させ、水素濃度及び酸素欠陥を低減させた第2の酸化物半導体膜を形成する。次に、第2の酸化物半導体膜を選択的にエッチングして、第3の酸化物半導体膜を形成した後、第2の酸化絶縁膜を形成して、当該第2の酸化絶縁膜を選択的にエッチングして、第3の酸化物半導体膜の端部を覆う保護膜を形成する。この後、第3の酸化物半導体膜及び保護膜上に一対の電極、ゲート絶縁膜、及びゲート電極を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

121 - 140 / 903

[ Back to top ]