Fターム[5F110HK42]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層の製法 (10,751) | 低抵抗層形成後の処理 (709)

Fターム[5F110HK42]に分類される特許

41 - 60 / 709

電界効果型トランジスタ、その製造方法及びスパッタリングターゲット

【課題】トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供すること。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】酸化物半導体膜を有するボトムゲート構造のトランジスタの作製工程におい

て、熱処理による脱水化または脱水素化処理、及び酸素ドープ処理を行う。熱処理による

脱水化または脱水素化処理を行った酸化物半導体膜を含み、且つ、作製工程において酸素

ドープ処理されたトランジスタは、バイアス−熱ストレス試験(BT試験)前後において

もトランジスタのしきい値電圧の変化量が低減できており、信頼性の高いトランジスタと

することができる。

(もっと読む)

テラヘルツ波素子

【課題】テラヘルツ波を発生又は検出するテラヘルツ波素子において、単色性が良いテラヘルツ波を効率良く出射する。

【解決手段】テラヘルツ波素子は、基板101の上に形成された第1の半導体層102と、第1の半導体層102の上に形成された第2の半導体層104と、第2の半導体層104の上に形成されたゲート電極106と、第2の半導体層104の上にゲート電極106を挟んで対向するように形成されたソース電極107及びドレイン電極108と、第2の半導体層104の上におけるゲート電極106とソース電極107との間及びゲート電極106とドレイン電極108との間に形成され、複数の金属膜109が周期的に配置された周期構造を有する周期金属膜109A,109Bと、ゲート電極106及び複数の金属膜109の上方に配置された第1のミラー111と、基板101の下に形成された第2のミラー112とを備えている。

(もっと読む)

導電膜パターンの形成方法

【課題】信頼性の高い導電膜パターンの製造方法を提供する。

【解決手段】本発明に係る導電膜パターンの製造方法は、基板10上に導電膜21を成膜し、導電膜21の表面に対して他の層を積層する前に、酸素をプラズマ化したプラズマアッシング処理を施し、表面処理した導電膜21上に、当該導電膜21をパターン形成するためのマスクパターン30を形成する。次いで、マスクパターン30を用いて導電膜21をウェットエッチングによりパターン形成する。基板10は、半導体基板であることが好ましい。導電膜パターンは、例えば、配線、電極パッド等である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

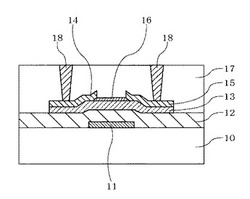

電子デバイス及び半導体装置の製造方法

【課題】簡素な装置で、短時間にて形成することができ、しかも、電極と能動層との間のコンタクト抵抗の低減を確実に図ることができる電荷注入層を備えた電子デバイスを提供する。

【解決手段】電子デバイスは、第1電極15、第1電極と離間して設けられた第2電極15、及び、第1電極15の上から第2電極15の上に亙り設けられた、有機半導体材料から成る能動層14を少なくとも備えており、第1電極15と能動層14との間、及び、第2電極15と能動層14との間には、電荷注入層16が形成されており、電荷注入層16は、酸化されることで電気伝導度の値が増加した有機材料から成る。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインが、第1半導体結晶層を構成する原子とニッケル原子との化合物、第1半導体結晶層を構成する原子とコバルト原子との化合物または第1半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなり、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、第2半導体結晶層を構成する原子とニッケル原子との化合物、第2半導体結晶層を構成する原子とコバルト原子との化合物、または、第2半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなる半導体デバイスを提供する。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板1aの活性領域1cが素子分離絶縁膜2で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極8a、ソース・ドレイン領域及び被覆応力膜を有するNTrを有し、ソース・ドレイン領域の両側部に位置する素子分離絶縁膜2aの表面は、ソース・ドレイン領域の表面より低い位置に形成されており、ゲート電極8a、活性領域1c、及び表面がソース・ドレイン領域の表面より低い位置に形成された素子分離絶縁膜2aを被覆して、チャネル形成領域に対し引張応力を印加する被覆応力膜が形成されている構成とする。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層104に形成された第1チャネル型の第1MISFET120の第1ソース124および第1ドレイン126が、第1半導体結晶層104を構成する原子と、ニッケル原子との化合物、または、コバルト原子との化合物、またはニッケル原子とコバルト原子との化合物からなり、第2半導体結晶層106に形成された第2チャネル型の第2MISFET130の第2ソース134および第2ドレイン136が、第2半導体結晶層106を構成する原子と、ニッケル原子との化合物、または、コバルト原子との化合物、または、ニッケル原子とコバルト原子との化合物からなる。

(もっと読む)

半導体装置

【課題】半導体集積回路における消費電力を低減する。また、半導体集積回路における動作の遅延を低減する。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気特性を持つ、酸化物半導体を用いた薄膜トランジスタを有する、信

頼性の高い半導体装置の作製方法の提供を目的の一とする。

【解決手段】絶縁表面上において、ゲート絶縁膜を間に挟んでゲート電極上に酸化物半導

体膜を形成し、酸化物半導体膜上に、チタン、モリブデンまたはタングステンを含む第1

の導電膜を形成し、第1の導電膜上に、電気陰性度が水素より低い金属を含む第2の導電

膜を形成し、第1の導電膜及び第2の導電膜をエッチングすることでソース電極及びドレ

イン電極を形成し、酸化物半導体膜、ソース電極及びドレイン電極上に、酸化物半導体膜

と接する絶縁膜を形成する半導体装置の作製方法。

(もっと読む)

半導体デバイス及びその製造方法

【課題】グラフェンの特性を生かしつつ、高耐圧デバイスや紫外発光・受光デバイスを実現する。

【解決手段】半導体デバイスを、2次元構造のグラフェン電極2、3と、グラフェン電極のグラフェン端に結合した2次元構造のボロンナイトライド半導体層5とを備えるものとする。

(もっと読む)

化合物半導体装置の製造方法

【課題】 短チャンネル効果が抑制され、メタルS/Dを有するInGaAs−MOSFETの低消費電力化をはかり得る化合物半導体装置を製造する。

【解決手段】 InGaAsをチャネルに用いた化合物半導体装置の製造方法であって、基板上のInGaAs層10上に、ゲート絶縁膜11を介してゲート電極12を形成した後、ゲート電極12の両側に露出するInGaAs層10上に、厚さ5.5nm以下のNi膜14を形成する。次いで、250℃以下の温度で熱処理を施すことにより、Ni膜14とInGaAs層10とを反応させて、ショットキー・ソース/ドレインとなるNi−InGaAs合金層15を形成する。

(もっと読む)

液晶表示装置

【課題】液晶表示装置の消費電力を低減すること及び表示の劣化を抑制すること。また、温度などの外部因子による表示の劣化を抑制すること。

【解決手段】各画素に設けられるトランジスタとして、チャネル形成領域が酸化物半導体層によって構成されるトランジスタを適用する。なお、酸化物半導体層を高純度化することで、トランジスタの室温におけるオフ電流値を10aA/μm以下且つ85℃におけるオフ電流値を100aA/μm以下とすることが可能である。そのため、液晶表示装置の消費電力を低減すること及び表示の劣化を抑制することが可能になる。また、上述したようにトランジスタは、85℃という高温においてもオフ電流値を100aA/μm以下とすることが可能である。そのため、温度などの外部因子による液晶表示装置の表示の劣化を抑制することができる。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板(1a,1b)の活性領域(1c,1d)が素子分離絶縁膜(2,6a)で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極(8a,8b)、ソース・ドレイン領域及び被覆応力膜を有するNTrとPTrを有し、活性領域におけるゲート長方向が<100>方向であり、素子分離絶縁膜としてNTrにおけるソース・ドレイン領域の両端部に第1の引張応力膜6aが形成され、ソース・ドレイン領域の両端部以外に第1の圧縮応力膜2が形成され、PTrの素子分離絶縁膜は第1の圧縮応力膜2が形成され、被覆応力膜としてNTrに第2の引張応力膜が形成され、PTrに第2の圧縮応力膜が形成されている構成とする。

(もっと読む)

記憶素子の駆動方法及び半導体装置の駆動方法

【課題】記憶素子(DRAM)の保持情報の多値化を簡便に行うこと。

【解決手段】記憶素子(DRAM)が有するトランジスタがオン状態の期間において、当該記憶素子(DRAM)に対して情報の書き込みを行う配線(ビット線)の電位を変動させることで、当該記憶素子(DRAM)が有する容量素子に蓄積される電荷量を制御する。これにより、当該記憶素子(DRAM)を有する半導体装置の構造を複雑化せずとも記憶素子(DRAM)の保持情報を多値化することが可能である。

(もっと読む)

半導体装置、表示装置

【課題】グローバルシャッタ方式で電荷の蓄積を行うイメージセンサにおいて、蓄積期間

終了時から最後の行を読み出すまでの期間、蓄積電荷保持部からの電荷の流出を極力抑制

することのできる半導体装置の提供を目的とする。

【解決手段】画素がマトリクス状に複数配置されたCMOSセンサ型のイメージセンサに

おいて、画素部の電荷蓄積制御トランジスタ及びリセットトランジスタにチャネル形成領

域が酸化物半導体で形成されたトランジスタを使用し、マトリクス状に配置された全ての

画素で信号電荷蓄積部のリセット動作を行った後、全ての画素でフォトダイオードによる

電荷の蓄積動作を行い、行毎に画素から信号の読み出し動作を行うことで歪みの無い撮像

を可能とする。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】高性能なIII−V族MISFETの実現を可能にする、より効果的なIII−V族化合物半導体表面のパッシベーション技術を提供する。

【解決手段】エピタキシャル成長により化合物半導体層をベース基板上に形成するステップと、前記化合物半導体層の表面をセレン化合物を含む洗浄液で洗浄するステップと、前記化合物半導体層の上に絶縁層を形成するステップと、を有する半導体基板の製造方法を提供する。前記セレン化合物として、セレン酸化物が挙げられる。前記セレン酸化物として、H2SeO3が挙げられる。前記洗浄液が、水、アンモニアおよびエタノールからなる群から選択された1以上の物質をさらに含んでもよい。前記化合物半導体層の表面がInxGa1−xAs(0≦x≦1)からなる場合、前記絶縁層がAl2O3からなるものであることが好ましく、Al2O3は、ALD法により形成されることが好ましい。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】絶縁破壊耐性に優れた化合物半導体積層構造を備えて基板の絶縁破壊の十分な抑止を実現し、ピンチオフ状態とする際にもリーク電流が極めて少ない信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上に形成された化合物半導体積層構造2は、その厚みが10μm以下であって、AlNからなる厚い第1のバッファ層を有しており、III族元素(Ga,Al)の総原子数のうち、Al原子の比率が50%以上とされ、換言すれば、V族元素のNとの化学結合(Ga−N,Al−N)の総数のうち、Al−Nが50%以上とされる。

(もっと読む)

41 - 60 / 709

[ Back to top ]