Fターム[5F110HK42]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層の製法 (10,751) | 低抵抗層形成後の処理 (709)

Fターム[5F110HK42]に分類される特許

101 - 120 / 709

有機半導体素子の製造方法

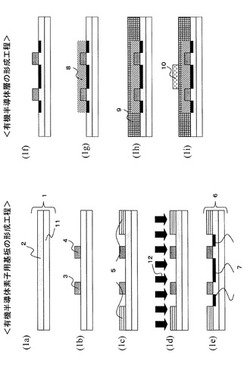

【課題】高い精度で効率良く有機半導体をパターニングすることができる有機半導体素子の製造方法を提供する。

【解決手段】有機半導体層形成用溶液に対して撥液性がある撥液部2を有する基体1と、前記基体1上に形成されたソース電極3及びドレイン電極4と、前記基体1の撥液部2の一部上に形成された遮蔽層5とを有し、前記ソース電極3及び前記ドレイン電極4に金もしくは/及び白金、又は酸化還元電位が銀以下の金属が含まれている有機半導体素子用基板6上に紫外線又は含酸素プラズマを前記有機半導体素子用基板6に照射して、前記有機半導体層形成用溶液に対して親液性がある親液部7に変性する有機半導体素子用基板6の形成工程と、有機半導体層8の形成工程と、前記ソース電極3及び前記ドレイン電極4に酸化還元電位が銀以下の金属が含まれている場合は還元工程と、を有する有機半導体素子の製造方法。

(もっと読む)

薄膜トランジスタ構造および表示装置

【課題】酸化物半導体上の保護膜形成時などにおける酸化物半導体表面の欠陥(ダメージ)に伴うTFT特性の劣化を、新たな処理工程を設けることなく簡易に且つ確実に低減することができ、製造コストの低減化、生産性および歩留まりの向上を実現できる技術を提供する。

【解決手段】本発明の薄膜トランジスタ構造は、薄膜トランジスタの半導体層に用いられ、In、Zn、およびSnの金属元素を含むIn−Zn−Sn酸化物と;前記In−Zn−Sn酸化物の上部に表面層と、を有している。保護膜形成前の表面層をX線光電子分光法(XPS)で検出し、酸素の1s電子(O1s)に帰属するピークエネルギーの強度をピーク分離によって求めたとき、下記式(1)の関係を満足する。

B/(A+B)≧0.33 ・・・ (1)

Aは、金属元素と結合するO1sのピークエネルギーの強度、

Bは、Cおよび/またはHの非金属元素と結合するO1sのピークエネルギーの

強度を意味する。

(もっと読む)

高分子化合物及びそれを用いた有機トランジスタ

【課題】有機トランジスタの活性層の構成材料として優れた電界効果移動度を発揮することができる高分子化合物を提供すること。

【解決手段】下式で表される第1構造単位とチオフェン環、又は、少なくとも1つのチオフェン環を含む縮合環を表し、且つ、前記第1構造単位とは異なる構造を有する第2構造単位とを含む高分子化合物。 (もっと読む)

(もっと読む)

Cu合金膜、及びそれを備えた表示装置または電子装置

【課題】基板及び/又は絶縁膜との高い密着性を有し、且つ、液晶表示装置などの製造過程で施される熱処理の後も低い電気抵抗率を有する新規なCu合金膜を提供すること。

【解決手段】表示装置用Cu合金膜であって、前記Cu合金膜は、Cu−Mn−B合金で構成されており、前記Cu合金膜の基板側の界面(I)から、前記Cu合金膜の最表面に向って50nm(II)までの深さ方向のMn量およびB量をそれぞれ、Mn量(MnI−II)およびB量(BI−II)とすると共に、前記Cu合金膜の深さ50nm(II)から、前記Cu合金膜最表面(III)までの深さ方向のMn量およびB量をそれぞれ、Mn量(MnII−III)およびB量(BII−III)とし、前記Mn量のMnI−IIとMnII−IIIとの関係が、2.0≦(MnI−II/MnII−III)であると共に、前記B量のBI−IIとBII−IIIとの関係が、1.5≦(BI−II/BII−III)であること。

(もっと読む)

ワイヤチャンネルを有する電界効果トランジスタ及びその製造方法

【課題】ワイヤチャンネルを有する電界効果トランジスタ及びその製造方法を提供する。

【解決手段】半導体基板100と、半導体基板100上に形成されたソース/ドレイン

領域142と、ソース/ドレイン領域142と電気的に連結され、2列及び少なくとも2

行で配列された複数個のワイヤチャンネル112e、114eと、複数個のワイヤチャン

ネル112e、114eをそれぞれ取り囲むゲート絶縁膜142aと、それぞれの複数個

のワイヤチャンネル112e、114e及びゲート絶縁膜142aを取り囲むゲート電極

と、を備える。

(もっと読む)

薄膜トランジスタの製造装置およびその製造方法、ならびにプログラム

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法、ならびにプログラムを提供する。

【解決手段】本発明は、基板上にゲート電極、ゲート絶縁層、半導体層、ソース電極およびドレイン電極が少なくとも設けられた薄膜トランジスタの製造方法である。ソース電極およびドレイン電極を形成する工程において、基板の歪み、または基板の伸縮率に基づいて、露光データを、スケーリング処理を用いて薄膜トランジスタのチャネル長を固定した状態で補正して第1の補正データを作成する。この第1の補正データに基づいて、ソース電極およびドレイン電極の形成領域にレーザ光を照射し、その形成領域を親液性にする。この形成領域に、ソース電極およびドレイン電極となる液滴を、打滴データに基づいて打滴する。

(もっと読む)

薄膜トランジスタの製造装置およびその製造方法

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法を提供する。

【解決手段】本発明は、基板上に薄膜トランジスタを製造する製造装置であり、基板に関する基板情報を取得する取得部と、取得部で得られた基板に関する基板情報に基づいて、基板の伸縮強度が高い方向を特定し、伸縮強度が高い方向と薄膜トランジスタのチャネル領域を挟んでソース電極およびドレイン電極が配置される配置方向とが直交するように薄膜トランジスタを形成する向きを設定する設定部とを有する。

(もっと読む)

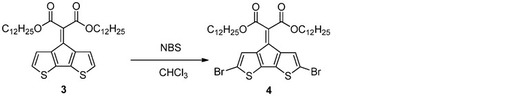

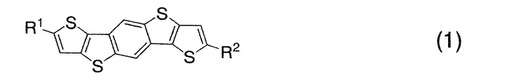

ジチエノベンゾジチオフェン誘導体溶液及び有機半導体層

【課題】 高いキャリア移動度を与えると共に容易に効率よく有機半導体層を製膜することが可能となるドロップキャスト製膜用溶液を提供する。

【解決手段】 純度98%以上を有する下記一般式(1)で示されるジチエノベンゾジチオフェン誘導体0.01〜10重量%及び炭素数7〜13の芳香族系炭化水素99.99〜90重量%からなるドロップキャスト製膜用溶液。

【化1】

(ここで、置換基R1及びR2は同一又は異なって、炭素数1〜20のアルキル基を示す。)

(もっと読む)

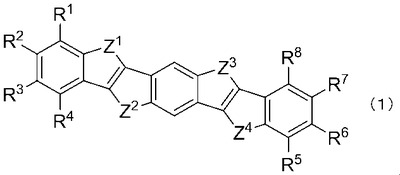

可溶性ヘテロアセン化合物及び該化合物を含有する薄膜および有機トランジスタ

【課題】有機半導体材料として好適な新規化合物の提供。

【解決手段】下記式(1)で示される化合物。

[式中、Z1〜Z4はそれぞれ独立に、硫黄原子又はセレン原子を表す。R1〜R8はそれぞれ独立に、水素原子、フッ素原子で置換されていてもよい炭素数1〜30のアルキル基、フッ素原子で置換されていてもよい炭素数1〜30のアルコキシ基、又は特定な置換シリル基を表す。]

(もっと読む)

微結晶半導体膜、及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜の作製方法を提供することを課題とする。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、種結晶上に、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を形成し、第2の微結晶半導体膜上に、第2の微結晶半導体膜に含まれる混相粒の隙間を埋めつつ、結晶成長を促す第4の条件で、第3の微結晶半導体膜を積層形成する。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

ジチエノベンゾジチオフェン誘導体及びこれを用いた有機薄膜トランジスタ

【課題】 溶媒への溶解性に優れることから容易に有機半導体材料等への展開が可能となると共に、高キャリア移動度が期待できる新規なジチエノベンゾジチオフェン誘導体及びこれを用いた有機薄膜トランジスタを提供する。

【解決手段】 下記一般式(1)で示されるジチエノベンゾジチオフェン誘導体。

【化1】

(ここで、置換基R1及びR2は同一又は異なって、n−ヘプチル基、n−オクチル基、炭素数10のアルキル基、炭素数12のアルキル基及び炭素数14のアルキル基からなる群より選択される置換基を示す。)

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜界面材料としてGeO2 を用いた場合においてもGeO2 層の劣化を抑制することができ、素子の信頼性向上をはかると共に、プロセスの歩留まり向上をはかる。

【解決手段】本発明の実施形態による電界効果トランジスタは、Geを含む基板10上の一部に設けられた、少なくともGeO2 層を含むゲート絶縁膜20と、ゲート絶縁膜20上に設けられたゲート電極30と、ゲート電極30下のチャネル領域を挟んで前記基板に設けられたソース/ドレイン領域50と、前記ゲート絶縁膜20の両側部に形成された窒素含有領域25と、を備えた。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】半導体記憶装置におけるデータ保持のためのリフレッシュ動作の回数を低減し、消費電力の小さい半導体記憶装置を提供する。また、三次元の形状を適用することで、集積度を高めても短チャネル効果の影響が低減され、かつ従来に比べてフォトリソグラフィ工程数の増加を抑えた半導体記憶装置を提供する。

【解決手段】溝部の設けられた絶縁膜103と、溝部を挟んで離間した一対の電極116と、溝部の側面および底面と接し、溝部の深さよりも厚さの薄い、一対の電極116と接する酸化物半導体膜106と、酸化物半導体膜106を覆うゲート絶縁膜112と、ゲート絶縁膜112を介して酸化物半導体膜106と重畳して設けられたゲート電極112と、を有するトランジスタ150と、キャパシタ160と、を有する半導体記憶装置である。

(もっと読む)

半導体基板、電界効果トランジスタ、半導体基板の製造方法および電界効果トランジスタの製造方法

【課題】DWB法における貼り合わせ時にIII-V族化合物半導体層が受けるダメージを小さくするとともに、受けたダメージの影響および界面準位の影響を低く抑え、高いキャリアの移動度を有するIII-V族MISFETを提供する。

【解決手段】ベース基板102と第1絶縁体層104と半導体層106とを有し、ベース基板102、第1絶縁体層104および半導体層106が、ベース基板102、第1絶縁体層104、半導体層106の順に位置し、第1絶縁体層104が、アモルファス状金属酸化物またはアモルファス状金属窒化物からなり、半導体層が、第1結晶層108および第2結晶層110を含み、第1結晶層108および第2結晶層110が、ベース基板102の側から、第1結晶層108、第2結晶層110の順に位置し、第1結晶層108の電子親和力Ea1が、第2結晶層110の電子親和力Ea2より大きい半導体基板を提供する。

(もっと読む)

有機薄膜積層体の製造方法および有機薄膜積層体

【課題】ポリオルガノシロキサンをスタンプとして用いて有機薄膜積層体を製造する方法において、スタンプへのインクの塗布と、インクから形成された薄膜のスタンプからの剥離の両方を好適に行うことができる方法を提供する。

【解決手段】スピロピラン化合物がポリオルガノシロキサン基材表面に配され又は結合したスタンプ1を用いて有機薄膜積層体5を製造する方法であって、(a)スピロピラン化合物がメロシアニン体の状態で、スタンプ1の表面に有機材料を含有するインク2を塗布して有機薄膜3を形成する工程と、(b)スピロピラン化合物がスピロ体の状態で、有機薄膜3をスタンプ1から被転写体4上に転写する工程とを有することを特徴とする有機薄膜積層体の製造方法。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

MOSトランジスタの製造方法

【課題】メタルソース/ドレインを有する極薄SOIMOSトランジスタにおいて、ゲート電極/ゲート絶縁膜の側壁につけた保護膜エッジからゲートエッジまでソース/ドレインの位置の制御とショットキーバリアハイトの制御の両者が実現できるMOSトランジスタの製造方法を提供する。

【解決手段】SOI層上にゲート電極を形成する工程と、該ゲート電極の側面にスペーサーを形成する工程と、該ゲート電極及び該保護膜をマスクにSOI層上に窒素添加Ni膜を成膜する工程と該Ni膜上にTiN膜を形成する工程と、窒素中でアニールしSOI層中にソース及びドレインとなるエピタキシャルNiSi2層を形成する工程と、TiNと残ったNi膜を除去する工程と、該ゲート電極及び該保護膜をマスクに該エピタキシャルNiSi2層中にPイオンを注入する工程と、該Pイオンを活性化する工程とを含むMOSトランジスタの製造方法。

(もっと読む)

TiC膜を含む半導体構造を形成する方法

【課題】 TiC膜を含む半導体構造を形成する方法を提供する。

【解決手段】 高誘電率(k)の誘電体14および界面層12を含む積層体を基板10の表面上に設けるステップと、Heによって希釈された炭素(C)源およびArを含む雰囲気において、Tiターゲットをスパッタすることにより、前記積層体上にTiC膜16を形成するステップとを含む、半導体構造を形成する方法である。

(もっと読む)

101 - 120 / 709

[ Back to top ]