Fターム[5F110HM05]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 形状 (2,461) | 他の構成要素との相対的な大きさが規定 (146)

Fターム[5F110HM05]に分類される特許

81 - 100 / 146

薄膜トランジスタ、アクティブマトリックス回路並びに表示装置

【課題】フィードスルー電圧ΔVがTFT基板全面において一定である薄膜トランジスタ、該薄膜トランジスタから構成されるアクティブマトリックス回路を用いることにより画素ごとの表示特性のバラツキに影響を及ぼすことの無い画像表示装置を提供する。

【解決手段】ソース電極1003は、長手をy方向に延設される少なくとも1つの矩形で、ゲート電極1002の上の目標位置に配置される領域S2からなり、ドレイン電極1004は、ゲート電極1002の上をx方向に横断し、該ゲート電極1002両端からのはみ出し部分それぞれの長さが△d以上である矩形の領域D1と、領域D1からy方向に延設され領域S2と長手方向同士を並行に隣接してチャネル部を形成する矩形で、該矩形の長手方向の一端部が最も近いゲート電極1002の端部位置よりも△d以上内側となるゲート電極1002の上の目標位置に配置される領域D2と、からなる。

(もっと読む)

電気光学装置、電子機器及び電気光学装置の設計方法

【課題】従来の電気光学装置では、製造工程を効率化することが困難である。

【解決手段】第1基板と、前記第1基板に対向する第2基板と、前記第1基板及び前記第2基板の間に挟持された電気光学物質と、複数の画素と、前記画素に対応して前記第1基板及び前記電気光学物質の間に設けられた、前記電気光学物質から前記第1基板側に向かう光151を前記第2基板側に反射させる画素電極95と、前記画素に対応して前記第1基板及び画素電極95の間に設けられたトランジスタ素子と、互いに隣り合う画素電極95同士間に設けられた絶縁膜97と、を有しており、光151の波長をλとし、絶縁膜97の屈折率をnとし、互いに隣り合う画素電極95同士間の間隙の幅をdとしたときに、d<0.61×λ/n(式1)を満たすことを特徴とする電気光学装置。

(もっと読む)

半導体装置及びその製造方法

【課題】所望の特性が得られるフィン型CMISFETを実現する。

【解決手段】ゲート絶縁膜14bの外側に位置するn型のフィン型半導体領域13bにおける上部コーナーの曲率半径r1’は、ゲート絶縁膜14bの下側に位置するn型のフィン型半導体領域13bにおける上部コーナーの曲率半径r1よりも大きく且つ2×r1以下である。ゲート絶縁膜914cの外側に位置するp型のフィン型半導体領域913cにおける上部コーナーの曲率半径r2’は、ゲート絶縁膜914cの下側に位置するp型のフィン型半導体領域913cにおける上部コーナーの曲率半径r2よりも大きく且つ2×r2以下である。

(もっと読む)

液晶表示装置

【課題】poly−Si層およびa−Si層が積層されたボトムゲートのTFTにおいて、リーク電流の増大を防止する。

【解決手段】最下層には、ゲート電極103が縦方向に細長く形成されている。このゲート電極103の上に、図示しないゲート絶縁膜104を挟んでpoly−Si層107およびa−Si層108からなる半導体層が形成されている。半導体層の上に、ソース電極110あるいはドレイン電極111が形成されている。ソース電極110あるいはドレイン電極111と半導体層の間にはn+Si層が形成されている。ソース電極110あるいはドレイン電極111の端部EDは、半導体層の端部ESよりも内側に形成されているので、半導体層の端部ESにおけるリーク電流を無くすことが出来る。

(もっと読む)

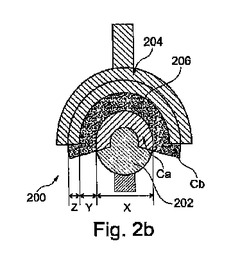

アクティブマトリクスOLEDディスプレイおよびその駆動回路

ディスプレイが、それぞれが関連画素駆動回路をもつ複数の有機発光ダイオード(OLED)画素と、複数の選択線と、複数のデータ線とを有する。画素駆動回路のそれぞれは、選択線およびデータ線に結合される。画素駆動回路は、OLEDを駆動するように構成された駆動トランジスタを含むとともに、選択線に結合された第1の端子と、データ線に結合された第2の端子とを有する選択トランジスタを含み、選択トランジスタの端子の一方は、選択トランジスタのゲート接続を備え、端子の他方は、選択トランジスタのドレイン接続およびソース接続の一方を備え、選択トランジスタは、ソース領域と、ドレイン領域と、ゲート領域とを備え、ゲート領域は、ソース領域およびドレイン領域に少なくとも部分的に重なり、ゲート接続と、ドレイン接続およびソース接続の一方との間の静電容量が、ゲート接続と、接続の他方との間の静電容量よりも小さくなるように、ゲート領域の、ソース領域およびドレイン領域の一方との重なりの面積が、領域の他方との重なりの面積よりも大きくなっている。  (もっと読む)

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】薄膜トランジスタ及びその製造方法を提供すること。

【解決手段】薄膜トランジスタ及びその製造方法において、薄膜トランジスタはゲート電極、ゲート絶縁膜、及びチャンネル膜が積層された構造物を具備する。前記チャンネル膜と接するように位置し、前記ゲート電極を横切る方向に延長され、両側は下部に位置するゲート電極の一側の縁内に配置するソースラインが具備される。また、前記チャンネル膜と接するように位置し、チャンネルの長さほど前記ソースラインと離隔されながら、前記ソースラインと対称である形状を有するようにドレインラインが配置される。前記薄膜トランジスタは、ゲートとソースライン及びドレイン間ラインのオーバーラップ面積が狭くてカットオフ周波数が高い。

(もっと読む)

表示装置

【課題】ソース電極およびドレイン電極とゲート電極との間の寄生容量の変化に起因するフリッカを抑制するとともに、薄膜トランジスタの動作速度の向上を図ることが可能な表示装置を提供する。

【解決手段】この表示装置100の薄膜トランジスタ1のゲート電極31は、平面的に見て、ゲート線3から突出するとともにY方向に延びるように形成されている。また、ソース電極6およびドレイン電極7は、平面的に見て、ゲート電極31の延びる長手方向(Y方向)と同じ方向に互いに略平行に対向して延びるとともに、ゲート電極31と半導体層5とが重なる領域のゲート電極31の長手方向(Y方向)に沿った外縁部よりも内側に配置されている。

(もっと読む)

表示装置およびその製造方法

【課題】オフ電流の増加を抑制できる薄膜トランジスタを備える表示装置の提供。

【解決手段】薄膜トランジスタが基板に形成されている表示装置であって、

前記薄膜トランジスタは、前記基板側から、ゲート電極、前記ゲート電極をも被って形成されるゲート絶縁膜、前記ゲート絶縁膜の上面に前記ゲート電極を跨いで形成される半導体層を備え、

前記半導体層は、チャネル領域、ソース・ドレイン領域が形成されているとともに、前記チャネル領域とソース・ドレイン領域の間にLDD領域を有し、

平面的に観て、前記チャネル電極は前記LDD領域側に張り出すことなく前記ゲート領域と重ねられて形成され、非導電性の光吸収材層が、前記LDD領域と重ねられて、前記ゲート電極と同層にあるいは前記ゲート電極の下層に形成されている。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】薄型軽量画像表示装置や、フレキシブル電子装置を構成するTFT回路の、TFTの配置をより稠密に行う。更には、小さい製造工程数により製造コストを低減する。

【解決手段】塗布法、滴下法、印刷法で、TFTの第1層目の電極のパターニングを行った後、基板の裏面からの露光を利用した自己整合技術により、第2層目の電極の位置合わせを、第1層目の電極に整合させて、塗布法、滴下法、印刷法で第2層目の電極を形成する。この際、第2層目の電極の配置を、前記の露光工程において、第1層目の電極の形状の投影像を遮光マスク用いて分離状態を実現する。例えば、TFTが並置される場合は、各電極の透光性基板の主面への投影像の関係が、第2層目の電極の配置が第1層目の電極に囲まれる形態か、第2層目の電極の配置より、分離するための第1層目の電極の一部が突き出す形態をとる。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法および表示装置

【課題】結晶化半導体層をチャネル領域に用いた薄膜トランジスタにおいて、トランジスタ特性の不均一性を低減すること。

【解決手段】本発明は、結晶化半導体層13におけるドレイン電極15bと接する端部からゲート電極11のドレイン電極15a側の端部と対応する位置までの距離をΔL1、結晶化半導体層13におけるソース電極15bと接する端部からゲート電極11のソース電極15b側の端部と対応する位置までの距離をΔL2、ドレイン電極15a側の不純物ドープ層14aにおける結晶化半導体層13と接する長さをドレイン側コンタクト長CT1、ソース電極15b側の不純物ドープ層14bにおける結晶化半導体層13と接する長さをソース側コンタクト長CT2とした場合、ΔL2がΔL1より長く、ソース側コンタクト長CT2がドレイン側コンタクト長CT1より長い薄膜トランジスタ1である。

(もっと読む)

薄膜トランジスタ及び表示装置

【課題】薄膜トランジスタのオン電流及びオフ電流に係る問題点を解決する。また、高速動作が可能な薄膜トランジスタを提供する。

【解決手段】ゲート絶縁層を介してゲート電極と重畳するアクセプターとなる不純物元素を添加した半導体層と、アクセプターとなる不純物元素を添加した半導体層上に重ねて設けられたバッファ層と、バッファ層の上面と、バッファ層及びアクセプターとなる不純物元素を添加した半導体層の側面を被覆する非晶質半導体層と、一端部がバッファ層と重なり、非晶質半導体層上に設けられ、ソース領域及びドレイン領域を形成する一導電型を付与する不純物元素を添加した一対の不純物半導体層とを有し、バッファ層の膜厚が、非晶質半導体層の膜厚よりも厚い薄膜トランジスタである。

(もっと読む)

薄膜トランジスタ及び表示装置

【課題】薄膜トランジスタのオン電流及びオフ電流に係る問題点を解決する。また、高速動作が可能な薄膜トランジスタを提供する。

【解決手段】ゲート絶縁層を介して、少なくとも一部がゲート電極と重畳するように離間して設けられた、ソース領域及びドレイン領域を形成する一導電型を付与する不純物元素が添加された一対の不純物半導体層と、ゲート絶縁層上で、ゲート電極及び一導電型を付与する不純物元素が添加された一対の不純物半導体層と少なくとも一部が重畳し、チャネル長方向に離間して配設された一対のアクセプターとなる不純物元素を添加した半導体層と、ゲート絶縁層と一対のアクセプターとなる不純物元素が添加された半導体層に接し、該一対のアクセプターとなる不純物元素が添加された半導体層間に延在する非晶質半導体層と、を有する薄膜トランジスタである。

(もっと読む)

半導体装置

【課題】横型IGBTにおいて、オン電圧を低くし、かつ、素子耐圧およびラッチアップ耐量を高くすること。

【解決手段】支持基板1上に絶縁膜2を介してn型ドリフト層3が設けられている。また、n型ドリフト層3の表面層のp型ベース層4およびn型バッファ層7に挟まれた部分に、支持基板1上の絶縁膜2よりも浅いトレンチ13が設けられている。トレンチ13は、トレンチ内絶縁膜14により埋められている。エミッタ電極11のコレクタ側の端部およびコレクタ電極12のエミッタ側の端部は、トレンチ内絶縁膜14の上方で終端となっている。エミッタ電極11のコレクタ側の端部およびコレクタ電極12のエミッタ側の端部は、層間絶縁膜22を挟んで上下に配置されている。

(もっと読む)

半導体装置およびその作製方法

【課題】工程を増やすことなく、1枚のマザーガラス基板上に所望の部分にそれぞれ精密に配線の側面の角度を異ならせた配線を提供することを課題とする。

【解決手段】多階調マスクを用いることで1つのフォトレジスト層を1枚のマザーガラス基板から遠ざかる方向に向かって断面積が連続的に減少するテーパ形状を有するフォトレジスト層を形成する。1本の配線を形成する際、1枚のフォトマスクを用い、金属膜を選択的にエッチングすることで、場所によって側面形状(具体的には基板主平面に対する角度)が異なる1本の配線を得る。

(もっと読む)

半導体装置

【課題】耐ノイズ性能等の電気的特性に優れたダブルゲート構造の半導体装置を提供する。

【解決手段】埋め込み酸化膜2の上に互いに分離して形成される複数のフィン3と、これらフィン3の一端側を共通に接続する第1のコンタクト領域4と、これらフィン3の他端側を共通に接続する第2のコンタクト領域5と、これらフィン3に跨るように配置されるゲート電極6と、ゲート電極6よりも第1のコンタクト領域4側のフィン3と第1のコンタクト領域4とを含むソース領域7と、ゲート電極6よりも第2のコンタクト領域5側のフィン3と第2のコンタクト領域5とを含むドレイン領域8と、を備えている。ドレイン側のフィン3における抵抗Rdがソース側のフィン3における抵抗Rsよりも10倍以上大きくなるようにしたため、トランジスタのコンダクタンスgmと出力抵抗routの積で表されるgm*routを大きくすることができ、耐ノイズ性能が向上する等、電気的特性がよくなる。

(もっと読む)

液晶表示装置

【課題】電気特性が良好であり、信頼性の高い薄膜トランジスタを有する液晶表示装置を量産高く作製する方法を提案することを課題とする。

【解決手段】逆スタガ型の薄膜トランジスタを有する液晶表示装置において、逆スタガの薄膜トランジスタは、ゲート電極上にゲート絶縁膜が形成され、ゲート絶縁膜上にチャネル形成領域として機能する微結晶半導体膜が形成され、微結晶半導体膜上にバッファ層が形成され、バッファ層に一対のソース領域及びドレイン領域が形成され、ソース領域及びドレイン領域の一部を露出するようにソース領域及びドレイン領域に接する一対のソース電極及びドレイン電極が形成される。

(もっと読む)

発光装置

【課題】電気特性が良好であり、信頼性の高い薄膜トランジスタを有する発光装置を量産高く作製する方法を提案することを課題とする。

【解決手段】逆スタガ型の薄膜トランジスタを有する発光装置において、逆スタガの薄膜トランジスタは、ゲート電極上にゲート絶縁膜が形成され、ゲート絶縁膜上にチャネル形成領域として機能する微結晶半導体膜が形成され、微結晶半導体膜上にバッファ層が形成され、バッファ層上に一対のソース領域及びドレイン領域が形成され、ソース領域及びドレイン領域の一部を露出するようにソース領域及びドレイン領域に接する一対のソース電極及びドレイン電極が形成される。

(もっと読む)

半導体装置

【課題】画像ムラがなく、良好な画像が得られる半導体装置を提供する。

【解決手段】第1の半導体層は、第1のNチャネル型TFTのソース及びドレインの一方と第1の配線とを電気的に接続するための第1のコンタクト領域と、前記第1のNチャネル型TFTのソース及びドレインの他方、並びに第2のNチャネル型TFTのソース及びドレインの他方と第2の配線とを電気的に接続するための第2のコンタクト領域と、前記第2のNチャネル型TFTのソース及びドレインの一方と前記第1の配線とを電気的に接続するための第3のコンタクト領域とを有し、前記第1乃至第3のコンタクト領域における前記第1の半導体層のチャネル幅方向の幅よりも、前記第1の半導体層と前記第1(第2)のNチャネル型TFTのゲート電極とが重なる領域における前記第1の半導体層のチャネル幅方向の幅の方が狭い。

(もっと読む)

半導体記憶装置とその製造方法

【課題】動作速度および信号差を維持したまま、セルサイズを縮小しかつ電極間の短絡を防止することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1の方向に延在する半導体層31と、半導体層内に設けられたソース層S、ドレイン層D、および、ボディBと、第1の方向に延在するビット線BLと、ボディの第1の側面SF1に第1のゲート絶縁膜GD1を介して設けられた第1のゲート電極GE1と、第1の方向へ延在し、第1のゲート電極の底部に接続され、第1のゲート電極と同一材料で一体形成された第1のゲート線GL1と、第1の側面の反対側にあるボディの第2の側面SF2に設けられ第2のゲート絶縁膜GD2を介して設けられた第2のゲート電極GE2と、第1の方向に対して交差する第2の方向へ延在し、第2のゲート電極の上部に接続され、第2のゲート電極と同一材料で一体形成された第2のゲート線WLとを備える。

(もっと読む)

有機半導体素子およびその製造方法、有機トランジスタアレイ、およびディスプレイ

【課題】本発明は、オフ電流が低い有機半導体トランジスタを有する有機半導体素子を提供することを主目的とする。

【解決手段】本発明は、基板、および、基板上に形成されたゲート電極と、上記ゲート電極上に形成されたゲート絶縁層と、上記ゲート絶縁層上に形成されたソース電極およびドレイン電極と、上記ソース電極およびドレイン電極の間のみに形成され、有機半導体材料からなる有機半導体層とを有する有機半導体トランジスタを有することを特徴とする有機半導体素子を提供することにより上記課題を解決するものである。

(もっと読む)

81 - 100 / 146

[ Back to top ]