Fターム[5F110HM05]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 形状 (2,461) | 他の構成要素との相対的な大きさが規定 (146)

Fターム[5F110HM05]に分類される特許

101 - 120 / 146

有機半導体素子およびその製造方法

【課題】有機半導体素子およびその製造方法の提供。

【解決手段】基板と、ソース電極と、ドレイン電極と、前記ソース電極と前記ドレイン電極とを連結する有機半導体層と、前記有機半導体層に電界を印加するためのゲート電極と、前記有機半導体層とゲート電極間に配置されるゲート絶縁膜とを備え、前記ゲート絶縁膜がハイパーブランチポリマーを成分として含有することを特徴とする有機半導体素子及びその製造方法。

(もっと読む)

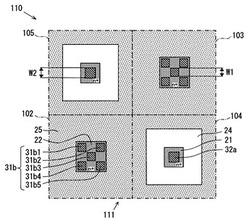

半導体装置

【課題】ソースセルとドレインセルが市松模様状に配置された低オン抵抗の横型MOSトランジスタを有してなる半導体装置であって、高密度配線に有利なプラグ技術と両立可能で、制御IC等との複合化に好適な小型の半導体装置を提供する。

【解決手段】ソースセル102,103とドレインセル104,105が、それぞれ、コンタクトプラグ31,32によって、平坦化された第1配線層41,42に接続されてなり、コンタクト31bで示されたソースコンタクトプラグが、コンタクト32aで示されたドレインコンタクトプラグのコンタクト面内における最小幅W2より小さな最小幅W1を有するコンタクト31b1〜31b5で示された小コンタクトプラグの複数個の組み合わせからなる半導体装置110とする。

(もっと読む)

液晶表示装置用アレイ基板及びその製造方法

【課題】ソース電極及びドレイン電極の下部にバリアパターンを構成しバリアパターンを通じて薄膜トランジスタのチャンネルの幅を決定することにより、チャンネル部のCDの偏差を最小化して均一な素子の特性を有する薄膜トランジスタを含むアレイ基板及びその製造方法を提供する。

【解決手段】ソース電極及びドレイン電極の下部に、ソース電極及びドレイン電極を構成する金属物質の湿式エッチング液にエッチングされない物質を利用してバリア層を形成して、バリア層を異方性の乾式エッチングによってパターニングし、望むチャンネル部のCDを得る。従って、湿式エッチングの過程でソース電極及びドレイン電極がオーバーエッチングされる場合でも、一定幅のチャンネル部を形成できる。

(もっと読む)

表示装置

【課題】薄膜トランジスタにリーク電流が発生するのを回避させた表示装置の提供。

【解決手段】基板上に、順次積層された、ゲート信号線、絶縁膜、半導体層、および導電体層を有し、

前記導電体層は、少なくとも、ドレイン信号線と接続されるドレイン電極および画素電極と接続されるソース電極を構成し、

前記半導体層は、平面的に観た場合、前記ドレイン電極の先端を除く部分において、前記導電体層に対して外方にはみ出し部を有するパターンを有することを特徴とする表示装置。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、および表示装置

【課題】半導体薄膜上で良好なソース−ドレイン耐圧を確保する。

【解決手段】薄膜トランジスタは絶縁性支持基板10上に設けられる半導体薄膜12と、半導体薄膜12上に設けられるゲート絶縁膜14と、ゲート絶縁膜14を介して半導体薄膜12上に形成されるゲート電極層16を備え、半導体薄膜12はゲート電極層16の下方に配置されるチャネル領域12Cと、チャネル領域12Cの両側に配置されるソースおよびドレイン領域12S,12Dと、チャネル領域12Cおよびドレイン領域12D間に配置されるLDD領域12LDを含む。チャネル領域12Cは不純物濃度が半導体薄膜12の厚さ方向においてゲート絶縁膜14との界面から支持基板10との界面に向かって高くなる不純物濃度プロファイルを有し、ソース領域12SおよびLDD領域12LDは不純物濃度が半導体薄膜12の厚さ方向においてゲート絶縁膜14との界面から支持基板10との界面に向かって低くなる不純物濃度プロファイルを有する。

(もっと読む)

表示装置およびその製造方法

【課題】極めて簡単な構成で、導電体層の破損に対する修復を可能にする表示装置の製造方法の提供。

【解決手段】基板上に、順次積層された、ゲート信号線、絶縁膜、非晶質の半導体層、および導電体層を有し、

前記導電体層は、少なくとも、前記半導体層の前記ゲート信号線と重畳するチャネル領域を間にして配置される薄膜トランジスタのドレイン電極およびソース電極、前記ドレイン電極と接続部を介して接続されるドレイン信号線を構成し、

前記半導体層は、前記導電体層の形成領域下に形成され、

前記導電体層に破損部が生じている場合、その破損部とその近傍における半導体層の部分を結晶化させる。

(もっと読む)

半導体装置、半導体装置の製造方法、電気光学装置および電子機器

【課題】製造が容易で、フレキシブル化に有利な両極性型の半導体装置およびその製造方法ならびにそれを備える電気光学装置および電子機器を提供すること。

【解決手段】本発明の半導体装置1は、基板8と、基板8の一方の面側に設けられ、導電体として機能するソース部3およびドレイン部4と、ソース部3およびドレイン部4との間に一体的に形成され、半導体として機能するチャネル部5とを備え、無機材料を主材料として構成された無機物層2と、無機物層2と接して設けられ、チャネル部5の極性と異なる極性を有し、有機半導体材料を主材料として構成された有機半導体層9と、無機物層2と接しないで設けられ、チャネル部5に電界を付与するゲート部7と、無機物層2とゲート部7との間に設けられ、ゲート部7に対してソース部3およびドレイン部4を絶縁するゲート絶縁層6とを有する。

(もっと読む)

薄膜トランジスタパネルおよびその製造方法

【課題】 エッチングされやすい真性酸化亜鉛からなる半導体薄膜を有する薄膜トランジスタを備えた薄膜トランジスタパネルにおいて、ゲート電極に対応する部分における半導体薄膜の周囲に空洞が生じないようにする。

【解決手段】 ガラス基板1の上面にはソース電極2およびドレイン電極3が形成され、それらの上面にITOからなる2つのオーミックコンタクト層4、5が形成されている。ソース電極2、ドレイン電極3および2つのオーミックコンタクト層4、5を含むガラス基板1の上面には、画素電極11をソース電極2に接続させるためのコンタクトホール13を有する真性酸化亜鉛からなる半導体薄膜6が形成されている。この場合、ゲート電極8下の全域およびその周囲には半導体薄膜6が形成されているため、ゲート電極8に対応する部分における半導体薄膜6の周囲に空洞が生じないようにすることができる。

(もっと読む)

表示装置

【課題】オフ時のリーク電流の発生を抑制し、画像品質を向上させる。

【解決手段】画素スイッチング素子102のチャネル端からドレイン部に渡る領域の電位と、その領域に対面する導電層の電位とが反転駆動時において同電位になるように、その対面する導電層を形成する。

(もっと読む)

半導体装置

【課題】ゲート長の微細化に対応し、完全空乏化素子として動作させることができ、ジュール熱に起因した発熱や基板浮遊効果が低減できる半導体装置を提供する。

【解決手段】p型半導体基板11上に形成された基板突起部31Aと、突起部31A上にゲート絶縁膜13を介して形成されたゲート電極14と、ゲート電極14を挟むように突起部31Aに形成されたソース領域15及びドレイン領域16と、基板突起部31Aを挟む半導体基板11上に形成された素子分離絶縁膜12と、素子分離絶縁膜12下の半導体基板11内に形成された第1、第2不純物領域17とを有する。第1及び第2不純物領域17同士が基板突起部31A下の半導体基板11内で接続され、ゲート電極14がその側面上に形成されている基板突起部31Aの高さ及び幅方向の長さは、ソース領域15及びドレイン領域16が形成される基板突起部31Aの高さ及び幅方向の長さよりそれぞれ短い。

(もっと読む)

薄膜トランジスタ基板、それの製造方法及びそれを有する表示パネル

【課題】層間ミスアラインを防止した薄膜トランジスタ基板、その製造方法及びそれを有する表示パネルを提供する。

【解決手段】薄膜トランジスタ基板はゲート電極、ゲート絶縁パターン、チャンネルパターン、有機絶縁パターン、ソース電極及びドレイン電極を含み、ゲート電極はベース基板上に形成され、ゲート絶縁パターンはゲート電極より小さい面積でゲート電極上に形成され、チャンネルパターンはゲート絶縁パターンと同一の面積でゲート絶縁パターン上に形成され、有機絶縁パターンはチャンネルパターン、ゲート絶縁パターン及びゲート電極を覆うようにベース基板上に形成され、チャンネルパターンの一部を露出させる開口部を有し、ソース電極及びドレイン電極は有機絶縁パターン上に形成され、開口部を通じてチャンネルパターンと接触し、互いに離間している

(もっと読む)

アクティブ型液晶表示パネル

【課題】アクティブ型液晶表示パネルにおいて、薄膜トランジスタのソース電極形成用のCr膜のサイドエッチング量を低減する。

【解決手段】Cr膜11SおよびAl系金属膜12Sからなるソース電極17は、画素電極9の図1の下辺部のほぼ全体の上面およびその近傍におけるゲート絶縁膜5の上面に形成されている。すると、Cr膜11Sの平面の面積が大きくなり、ひいてはCr膜11Sの周囲面の面積(周囲長×膜厚)も大きくなる。そして、このCr膜11Sの周囲面の面積の増大により、Cr膜11Sのサイドエッチング量を低減することができる。

(もっと読む)

半導体装置

【課題】ソース・ドレイン領域の構造を最適化することにより、高いIon/Ioff比を達成する電界効果トランジスタを含む半導体装置を提供する。

【解決手段】第1のゲート電極107と第2のゲート電極108は、チャネル領域101の両側に対向するように、第1のゲート絶縁膜103と第2のゲート絶縁膜104を介して、それぞれ形成され、ソース領域111および前記ドレイン領域121は、第1のゲート電極107と第2のゲート電極108の両側に、チャネル領域101を挟んで形成され、第1のゲート絶縁膜103とチャネル領域104との界面に垂直な方向のソース領域111の厚さ(TSis)が、同じ方向のチャネル領域101の厚さ(TSic)よりも厚く、かつ、ソース領域111と、第1、第2のゲート電極107、108が、ゲート長方向に離間している電界効果トランジスタを含む半導体装置。

(もっと読む)

電界効果トランジスタ、TFT駆動回路、パネルおよびディスプレイ

【課題】半導体ナノワイヤを用い良好なトランジスタ特性を有する新規な電界効果トランジスタの構造を提供する。

【解決手段】本発明の一例である電界効果トランジスタは、基板40、ゲート電極41、ゲート絶縁膜42がこの順に配置され、ゲート絶縁膜42の上に半導体ナノワイヤ45とソース電極43・ドレイン電極44が設けられている。半導体ナノワイヤ45とソース電極43・ドレイン電極44とのコンタクト領域において、半導体ナノワイヤ45の表面をソース電極43・ドレイン電極44の構成材料が覆っている。

(もっと読む)

トランジスタ

【課題】オン抵抗の上昇を抑制しつつスイッチング耐圧を確保できるトランジスタを提供する。

【解決手段】埋込絶縁層と、埋込絶縁層の主面上に設けられ、交互に配置された複数の第1導電型のソース領域と複数の第2導電型のベースコンタクト領域とを有するソース部と、第1導電型のドレイン部と、ソース部とドレイン部との間に設けられソース領域及びベースコンタクト領域に接している第2導電型のベース領域と、を有する半導体層と、ベース領域の上に設けられたゲート絶縁膜と、ゲート絶縁膜の上に設けられたゲート電極とを備え、ソース領域とベース領域との接合部を、ベースコンタクト領域とベース領域との接合部よりもドレイン部側に設けた。

(もっと読む)

半導体集積回路及びその製造方法

【課題】メモリ回路と論理回路とでしきい電圧の異なるCMOSトランジスタを容易に製造することができ、CMOSトランジスタのオフリーク電流を低減して消費電力を低減することができる半導体集積回路及びその製造方法を得る。

【解決手段】本発明に係る半導体集積回路は、絶縁膜上に半導体膜を形成した半導体基板上に第1のCMOSトランジスタ及び第2のCMOSトランジスタが形成され、第1のCMOSトランジスタに用いられた第1のゲート絶縁膜の誘電率は、第2のCMOSトランジスタに用いられた第2のゲート絶縁膜の誘電率よりも高く、第1のCMOSトランジスタによりメモリ回路が構成され、第2のCMOSトランジスタにより論理回路が構成されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ソース・ドレイン領域へのコンタクト抵抗が小さく、かつ、電気的特性が従来よりも安定したFIN型FETからなるメモリセルを備えた半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、絶縁層20と、絶縁層上に設けられ、電気的に浮遊状態のフローティングボディ領域R2、および、該フローティングボディ領域の両側にあるソース・ドレイン領域R1を含むFIN型半導体層45と、フローティングボディ領域の両側面に形成されたゲート絶縁膜50と、フローティングボディ領域の両側面にゲート絶縁膜を介して設けられたゲート電極70と、ソース・ドレイン領域の上面に接触するソース・ドレイン電極SL・BLとを備え、絶縁層の表面と平行にFIN型半導体層を切断した断面において、フローティングボディ領域における該FIN型半導体層の厚みD2が、ソース・ドレイン領域における該FIN型半導体層の厚みD1よりも薄い。

(もっと読む)

薄膜トランジスタ基板及び薄膜トランジスタ基板の生成方法

【課題】塗布電極パターンが親撥液性パターンに一致しないパターン不良が生じやすく、また塗布プロセスが煩雑で生産性が低いという課題があった。

【解決手段】基板と、その基板平面上に複数並べて形成され、複数の楕円が長軸方向に並べて形成された外縁を連続的に接続して形成されたパターン、または1つの楕円の外縁形状で形成されたパターンであるリング状平面パターンで構成されたゲート電極と、そのゲート電極上に形成されたゲート絶縁膜と、ゲート電極の形状を投影したゲート絶縁膜上の平面領域を除いたゲート絶縁膜上に形成されたソース電極及びドレイン電極と、を有する薄膜トランジスタ基板。

(もっと読む)

フィールドプレートを具える半導体デバイス及びその製造方法

半導体の製造方法は、半導体デバイス層中に浅溝隔離構造14の形成を具える。前記浅溝隔離構造は、前記半導体デバイス層を形成するフィールド領域を囲んだU字形又はO字形であり、前記半導体デバイス層は、導電性を得るためにドープ及び/又は自滅される。前記半導体デバイスは、延在したドレイン領域50又はドリフト領域、及び、ドレイン領域42を有する。絶縁ゲート26は、本体領域の上部に設けられる。ソース領域34、40は、深ソース領域40及び浅ソース領域34を有するように加工されている。前記本体と同じ導電型のコンタクト領域60は、前記深ソース領域40に隣接して設けられる。前記本体は、前記浅ソース領域34の下で、前記コンタクト領域60と接触するように延在している。  (もっと読む)

(もっと読む)

半導体装置

【課題】LOCOS酸化膜が存在しない領域よりも先にLOCOS酸化膜が存在する領域が空乏化し、ソースからドレインに流れる電流経路の途中で電界方向が逆となり、この領域が高抵抗領域化し、電圧電流特性の劣化を引き起こし、ON抵抗の増大を招いている。

【解決手段】P型半導体基板1上のN- 型ウェル拡散層2中に形成されたドレインP+ 型拡散層6とソースP+ 型拡散層7と、LOCOS酸化膜5と、ゲート酸化膜8と、ゲート電極9と、ドレインP+ 型拡散層6の底面部からゲート酸化膜9下に達する電界緩和用の低濃度P- 型拡散層3と、低濃度P- 型拡散層3内に形成された中濃度P- 型拡散層4とを備え、ゲート電極9下部の低濃度P- 型拡散層3における表面部分で、低濃度P- 型拡散層3におけるLOCOS酸化膜5が存在しない領域Aの長さLAをLOCOS酸化膜5の存在する領域Bの長さLB よりも長くしてある。

(もっと読む)

101 - 120 / 146

[ Back to top ]