Fターム[5F110HM05]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 形状 (2,461) | 他の構成要素との相対的な大きさが規定 (146)

Fターム[5F110HM05]に分類される特許

41 - 60 / 146

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】酸化物半導体膜を含むトランジスタにおいて、酸化物半導体膜の上面部に、チャネル保護膜として機能する、酸化物半導体膜と同種の成分でなる金属酸化物膜が積層されているトランジスタを提供する。また、トランジスタの活性層に用いる酸化物半導体膜は、熱処理によって、水素、水分、水酸基または水素化物などの不純物を酸化物半導体より排除し、かつ不純物の排除工程によって同時に減少してしまう酸化物半導体を構成する主成分材料である酸素を供給することによって、高純度化および電気的にi型(真性)化されたものである。

(もっと読む)

電子装置

【課題】電流駆動能力を大きくできる静電対策素子を備える電子装置を提供する。

【解決手段】複数のスイッチング素子20が配置されたスイッチング素子配置領域10と、スイッチング素子配置領域10の外側に設けられ、複数の非線形素子60、70が配置された保護素子配置領域50とを備え、非線形素子60、70はスイッチング素子20を静電気から保護する保護素子であり、非線形素子60、70の活性層が酸化物半導体で構成され、活性層の幅がソース電極とドレイン電極の幅よりも大きく、スイッチング素子20の活性層が酸化物半導体で構成され、活性層の幅がソース電極とドレイン電極の幅よりも小さく、スイッチング素子20よりも非線形素子60、70の方が電流が流れやすい。

(もっと読む)

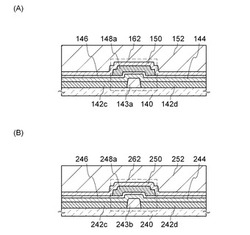

半導体装置および半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さ(RMS)が1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、または絶縁層表面の一部とドレイン電極表面との高低差は、5nm未満の半導体装置である。

(もっと読む)

薄膜トランジスタ

【課題】プラスチック基板上に薄膜トランジスタアレイを集積したアクティブマトリクス基板に用いられる薄膜トランジスタを提供することにある。

【解決手段】本発明の薄膜トランジスタは、基板と、基板上に形成されたゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜を介してゲート電極の上方に形成された半導体層と、半導体層と交差するように形成されたソース電極と、半導体層と交差するように形成されたドレイン電極とを備える。半導体層の側面のうち、ソース電極およびドレイン電極が延びる方向に平行な側面は、ソース電極およびドレイン電極の外側の側面に整合している。

(もっと読む)

薄膜トランジスタ、その製造方法、及び表示装置並びに電子機器

【課題】製造コストが少なく、光リーク電流が抑制された薄膜トランジスタを提供する。

【解決手段】透明基板上に作製される薄膜トランジスタであって、透明基板上に、少なくともチャネル領域と重畳しないように配置された遮光膜、下地層、結晶性シリコン膜、ゲート絶縁膜、ゲート電極膜を順次形成してなるトップゲート型結晶性シリコン薄膜トランジスタの構造を具え;結晶性シリコン膜には、チャネル長Lのチャネル領域、それを挟むLDD長dのLDD領域、ソース領域、ドレイン領域が形成されており;遮光膜はチャネル領域を挟んで分割されており;分割された遮光膜の間隔xは、チャネル長L以上、チャネル長LとLDD長dの2倍の和(L+2d)以下に選択されていることを特徴とする。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタのオン電流の安定を図る。

【解決手段】ELパネル1において、駆動素子として用いるスイッチトランジスタ5、駆動トランジスタ6などの薄膜トランジスタにおけるチャネル保護膜6d(5d)に鋭角なエッジ部6p(5p)を設けて、そのエッジ部6d(5d)でソース電極6i(5i)と不純物半導体膜6g(5g)の積層体を破断するようにして、その積層体がチャネル保護膜6d(5d)の上面に重ならない構造にすることで、チャネルとなる領域を覆うチャネル保護膜6d(5d)に作用するバックゲート効果を抑制することができ、チャネルの乱れを抑えることができるので、薄膜トランジスタ6(5)のオン電流(Id)を従来のものより増加させ、好適な値に安定させることを可能にした。

(もっと読む)

半導体装置及びその製造方法

【課題】低容量且つ高温特性が良好な素子分離領域を有する高速なMIS電界効果トランジスタを提供する。

【解決手段】半導体基板1にウエル領域2が設けられ、ウエル領域2内には上部、下部及び側面にシリコン酸化膜3を有し、内部が空孔4に形成されたトレンチ素子分離領域が選択的に設けられ、トレンチ素子分離領域により画定されたウエル領域2が設けられた半導体基板1上にゲート酸化膜9を介してゲート電極10が設けられ、ゲート電極10の側壁にサイドウォール11が設けられ、ウエル領域2が設けられた半導体基板1には、ゲート電極10に自己整合して低濃度のソースドレイン領域(6、7)及びサイドウォール11に自己整合して高濃度のソースドレイン領域(5、8)が設けられ、高濃度のソースドレイン領域にはそれぞれバリアメタル14を有する導電プラグ15を介してバリアメタル17を有する配線18が接続されている構造からなるMIS電界効果トランジスタ。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極及びドレイン電極は、第1の導電層と、第1の導電層の端部よりチャネル長方向に伸長した領域を有する第2の導電層と、を含む半導体装置である。

(もっと読む)

薄膜トランジスタ、その製造方法、およびそれを利用した表示基板

【課題】酸化物半導体層に対する外部光の照射を遮断し、その半導体特性の劣化を防止できる薄膜トランジスタ、その製造方法、およびそれをスイッチング素子として利用し、表示品質を向上した表示基板を提供する。

【解決手段】本発明による薄膜トランジスタは、酸化物半導体層と、前記酸化物半導体層のチャネル領域と重なるように前記酸化物半導体層の上に形成された第1保護層と、前記酸化物半導体層と前記第1保護層との間に形成された不透明層と、前記酸化物半導体層の一側に配置されたソース電極と、前記チャネル領域を介して前記ソース電極と対向するように前記酸化物半導体層の他側に配置されたドレーン電極と、前記酸化物半導体層に電界を印加するゲート電極と、前記ゲート電極と前記酸化物半導体層との間に形成されたゲート絶縁層と、を含み構成される。

(もっと読む)

横型IGBT及び横型IGBTの製造方法

【課題】ボンディングパッドを直上に配置して小型化を可能にしつつ電界集中による耐圧低下を防止する。

【解決手段】n型半導体エピタキシャル層5の表面に、エミッタ電極18、コレクタ電極20及びゲート電極16を形成した横型IGBT1において、前記コレクタ電極20及び前記ゲート電極16の上に絶縁層30を設け、この絶縁層30の上に前記エミッタ電極18に繋がるボンディングパッド32を設け、前記n型半導体エピタキシャル層5の内部には、前記ボンディングパッド32の電位により電界が集中する箇所であるエリアBに絶縁部40を設けた。

(もっと読む)

液晶表示装置及びその製造方法

【課題】本発明は、金属パターンの下に配置される半導体パターンを適切に処理することを目的とする。

【解決手段】半導体パターン16及び金属パターン18を、半導体パターン16が、金属パターン18の下に積層された第1部分26と、第1部分26から金属パターン18の外側にはみ出す第2部分28と、を有するように形成する。金属パターン18及び半導体パターン16を覆う絶縁層30を形成する。絶縁層30の、金属パターン18の上方の第1領域と、半導体パターン16の少なくとも第2部分28の上方の第2領域と、に対してエッチングを行う。エッチング工程で、第1領域では絶縁層30をエッチングして金属パターン18との電気的接続のための貫通穴34を形成し、第2領域では絶縁層30及び半導体パターン16をエッチングして、半導体パターン16の第2部分28を除去する。

(もっと読む)

薄膜トランジスタ、発光装置、電子機器、及び、薄膜トランジスタの形成方法

【課題】ソース−ドレイン間等の電圧−電流特性を改善することができる薄膜トランジスタ、発光装置、電子機器、及び、薄膜トランジスタの形成方法を提供する。

【解決手段】薄膜トランジスタ100は、半導体膜119と、半導体膜119の上方に形成されたソース電極層140と、半導体膜119の上方に形成されたドレイン電極層142と、ソース電極層140とドレイン電極層142との間、かつ、半導体膜119の上方に形成されたチャネル保護膜113と、を備える薄膜トランジスタであって、ソース電極層140とドレイン電極層142の少なくとも何れか一方は、チャネル保護膜113と接し、その上面がチャネル保護膜113の上面を超えない接触領域を有して、チャネル保護膜113の上面と重なっていない。

(もっと読む)

電気化学デバイス

本発明は、そのレドックス状態を電気化学的の変える能力を有する電気化学的活性層(205)を含んでなる電気化学デバイスに関わる。電解質(201)と電気化学的活性層(205)との間に、耐食性材料の電極(210)の部分(210)を供することにより、電気化学デバイスの電気化学反応による、望ましくない変色が減少する。  (もっと読む)

(もっと読む)

半導体デバイスおよび表示装置

【課題】オン抵抗を犠牲にしないで寄生容量とリーク電流のトレードオフを解消または緩和する。

【解決手段】TFT部10Bは、2つのソース・ドレイン電極18,19が、半導体膜15の平面視でチャネル形成領域を挟んで位置する一方と他方の半導体領域に接する。ソース・ドレイン電極18,19は、半導体膜15と接する領域(斜線部)の当該ソース・ドレイン電極の輪郭部分30において、その両端のエッジポイント31の各々が、平面視でゲート電極13の外側に位置している。

(もっと読む)

トランジスタ及びトランジスタの製造方法

【課題】トランジスタにおけるオン電流の向上とリーク電流の低減を図る。

【解決手段】結晶性微結晶シリコンの第一半導体膜51と、非晶質シリコンの第二半導体膜52とが重なっている積層領域の両端側が、非晶質シリコンからなる第二半導体膜52の単層領域となる半導体膜5bを備えるスイッチトランジスタ5において、チャネル保護膜5dが、半導体膜5bにおける積層領域を覆いつつ、そのチャネル保護膜5dの両端側で非晶質シリコンの単層領域の一部を覆い、また、ドレイン電極5hとソース電極5iが、不純物半導体膜5f,5gを介して半導体膜5bにおける非晶質シリコンの第二半導体膜52と接し、その半導体膜5bと電気的に接続することになるので、結晶性シリコン内の欠陥に起因する電気的欠陥の発生が抑えられて、リーク電流の低減が図られる。

(もっと読む)

半導体装置およびその作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】ボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部にチャネル保護層となる酸化物絶縁層を形成し、その酸化物絶縁層の形成時に酸化物半導体層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。酸化物半導体層の周縁部(側面を含む)を覆う酸化物絶縁層は、ゲート電極層と、その上方または周辺に形成される配線層(ソース配線層や容量配線層など)との距離を大きくし、寄生容量の低減を図る。酸化物半導体層の周縁部を覆う酸化物絶縁層は、チャネル保護層と同一工程で形成されるため、工程数の増加なく、寄生容量を低減できる。

(もっと読む)

アレイ

【課題】基板上に製造される回路を提供し、ゲート/チャネルリードの過剰オーバーラップの問題を軽減する技法を提供する。

【解決手段】アレイはセルを含み、各セル16が底部ゲートアモルファスシリコン薄膜トランジスタ(a−SiTFT)20を有する。各a−SiTFT20は、そのゲート領域60上に、そのエッジ84、86を越えて延出する未ドープアモルファスシリコン層64を有する。各a−SiTFT20は、そのゲート領域60のエッジ84、86とほぼ整合されるエッジ80、82を有する絶縁領域66を有する。微晶質シリコン又は多結晶質シリコンのような、ドープ半導体材料からなる2つのチャネルリード70、72は未ドープアモルファスシリコン層64上にあり、その各々は、絶縁領域のエッジに、最大オーバーラップ距離(1.0μm)以下の距離だけオーバーラップする。

(もっと読む)

トランジスタ基板及びトランジスタ基板の製造方法

【課題】微結晶シリコンをチャネル領域として用い、良好にリーク電流を抑制することが可能なトランジスタを備えるトランジスタ基板及びトランジスタ基板の製造方法を提供する。

【解決手段】トランジスタ基板におけるトランジスタ100は、基板11と、ゲート電極112と、ゲート絶縁膜113と、半導体層(チャネル領域)114と、ドレイン領域116、ソース領域117と、ドレイン電極118と、ソース電極119と、を備える。ドレイン領域116と半導体層114が接触する箇所及びソース領域117と半導体層114が接触する箇所のうち少なくとも一方は、ゲート電極112と比較し、薄膜トランジスタ100のチャネル長方向に外側に位置するように形成されている。このようにストッパ膜115を形成することにより、電界の急激な変化を抑制することができ、良好にリーク電流を抑制することができる。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】Vthのシフト量のばらつきが抑えられ、Vthが安定した薄膜トランジスタ及びその製造方法を提供する。

【解決手段】本発明の薄膜トランジスタ200は、ゲート電極112と、ゲート電極112上に配置されたゲート絶縁膜120と、ゲート絶縁膜120上に配置された微結晶Si層133と、酸化珪素膜142と酸化珪素膜142上に配置されたa−Si層152とからなり、微結晶Si層133におけるゲート電極112の上方に位置する部分上に配置された積層体156と、積層体156の両側の微結晶Si層133上にそれぞれが配置され、微結晶Si層133と電気的に接続されたソース電極172及びドレイン電極173とを備える。

(もっと読む)

41 - 60 / 146

[ Back to top ]