Fターム[5F110NN71]の内容

Fターム[5F110NN71]の下位に属するFターム

Fターム[5F110NN71]に分類される特許

341 - 360 / 2,024

半導体装置

【課題】半導体基板へのリーク電流が少ないMOS構造をダイオードとして用いる半導体装置を提供する。

【解決手段】電界効果トランジスタと、抵抗素子20と、を備える。前記抵抗素子は、前記電界効果トランジスタのバックゲート電極24と一方のソース・ドレイン領域16との接続点23と、前記電界効果トランジスタのゲート電極19との間に接続されている。そして、前記電界効果トランジスタの他方のソース・ドレイン領域15と前記ゲート電極19との間に電圧が印加される。

(もっと読む)

光電変換装置

【課題】電圧降下が小さい整流素子を得ること、及び、コンバータ回路の作製コストを抑制することを課題とする。

【解決手段】光電変換素子と、当該光電変換素子の出力を昇圧又は降圧し、スイッチング素子及び整流素子を有するコンバータ回路と、を有する光電変換装置において、当該スイッチング素子として、ノーマリオフの第1の酸化物半導体トランジスタと、当該整流素子として、ダイオード接続されたノーマリオンの第2の酸化物半導体トランジスタとを有する光電変換装置に関する。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】柱状結晶構造を有する金属を用いた場合でも、簡便な方法で、再現性良く階段構造状のテーパーを有する電極を形成する。

【解決手段】真空状態を保ったままの状態において、同一種類の金属を用いて、スパッタリング法で少なくとも2層の金属膜を成膜する成膜工程と、該成膜工程によって成膜された複数の金属膜にエッチング処理を施すことにより、階段構造状のテーパー形状を端部に有する、ゲート電極、ソース電極およびドレイン電極のうちの少なくとも1つを形成するエッチング工程とによって薄膜トランジスタを製造する。

(もっと読む)

薄膜トランジスタアレイ基板、及びその製造方法、並びに表示装置

【課題】製造工程中に生じる静電気に起因する不良を防止しつつ、簡便なプロセスで製造可能であり、かつ、薄膜トランジスタ特性を維持しつつ検査に適した薄膜トランジスタアレイ基板を提供する。

【解決手段】本発明に係る薄膜トランジスタアレイ基板は、ゲート配線1及びソース配線2の少なくとも一方と、抵抗体4を介して電気的に接続されるショートリング配線3を備える。抵抗体4は、ソース配線2及びショートリング配線3と同一の層からなり、ショートリング配線3と一体的に形成されたメタル膜13と、メタル膜13の直下に形成された第2半導体膜12と、その直下に形成された第1半導体膜11の積層体からなる。抵抗体4の平面視上の形状は、少なくとも一部の領域において第1半導体膜11の幅W1に比して第2半導体膜12及び前記メタル膜13の幅W2を小さくし、抵抗体4の抵抗値は、メタル膜13の形状により調整する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一つとする。

【解決手段】酸化物半導体層を有するボトムゲート構造のトランジスタの作製工程において、酸化物半導体層の脱水化または脱水素化処理として、酸素を含む雰囲気での加熱処理と、真空中での加熱処理を段階的に行う。また、加熱処理と同時に短波長の光照射を行い、水素やOH等の脱離を助長させる。この様な熱処理による脱水化または脱水素化処理を施した酸化物半導体層を有するトランジスタは、光照射やバイアス−熱ストレス試験(BT)試験前後における電気特性の不安定性を改善することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する脱水化または脱水素化された酸化物半導体層に接する絶縁層に、シリコン過酸化ラジカルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

液晶表示装置

【課題】オフ電流の低い半導体装置などを提供することを課題とする。または、正確な表示を行う半導体装置などを提供することを課題とする。または、視野角の広い表示装置などを提供することを課題とする。または、画面の焼き付きを低減した表示装置などを提供することを課題とする。

【解決手段】上記課題を解決するために、酸化物半導体(OS:オキサイドセミコンダクター)を有するトランジスタ、特に、酸化物半導体を有する薄膜MOSトランジスタを用いて、回路を構成する。その酸化物半導体は、実質的に真性な半導体となっている。そのため、非常にオフ電流が低い。

(もっと読む)

半導体装置

【課題】ゲート電極層がゲート絶縁層を介して、チャネル領域を形成する酸化物半導体層に重畳するトップゲート構造のトランジスタにおいて、ゲート絶縁層と対向し、かつ酸化物半導体層と接する絶縁層に水素が多く含まれている場合、酸化物半導体層に水素が拡散し、トランジスタの電気特性が不良となる。そこで、良好な電気特性を有する半導体装置を提供する。

【解決手段】酸化物半導体層と接する絶縁層に水素濃度が6×1020atoms/cm3未満である絶縁層を用いる。さらに、水素濃度が6×1020atoms/cm3未満であるゲート絶縁層を用いてもよい。このようにすることで、酸化物半導体層に水素が拡散することを抑制することができ、良好な電気特性を有する半導体装置を提供することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを課題の一とする。

【解決手段】ゲート絶縁層上に膜厚が2nm以上15nm以下の薄い第1の酸化物半導体膜を形成し、第1の加熱処理を行って第1の酸化物半導体膜の表面から内部に向かって結晶成長させて第1の結晶層を形成し、第1の結晶層上に第1の酸化物半導体膜よりも厚い第2の酸化物半導体膜を形成し、第2の加熱処理を行って第1の結晶層からその上の第2の酸化物半導体膜表面に向かって結晶成長させて第2の結晶層を形成し、第2の結晶層を形成した後、さらに酸素ドープ処理を行って第2の結晶層に酸素原子を供給する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する酸化物半導体層に接する絶縁層に、シリコン過酸化ラジカルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

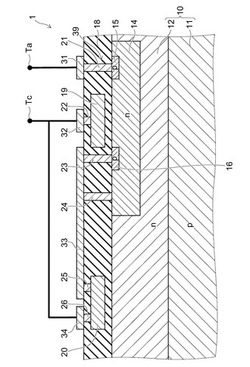

電界効果トランジスタの高電圧動作方法とそのバイアス回路

【課題】 ICないしLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該ICないしLSI中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートを分割してドレインにより近い分割ゲートへドレイン電位により近い電位でかつドレイン電位に応じて変化する電位を供給する手段をとる。

(もっと読む)

薄膜トランジスタおよび表示装置

【課題】ゲート絶縁膜に固定電荷を注入することなく閾値電圧をプラス方向にシフトさせることが可能な薄膜トランジスタおよびこれを備えた表示装置を提供する。

【解決手段】チャネル領域40A上に絶縁材料よりなる固定電荷蓄積層50を設け、この固定電荷蓄積層50の上面側に固定電荷制御電極80を設ける。固定電荷制御電極80を正(+)電位、ドレイン電極60Dを負(−)電位とし、ソース電極60Sを電気的に浮いた状態とすると、または、固定電荷制御電極80のみを正(+)電位とすると、チャネル電界によって加速されたホットエレクトロン、または衝突電離によって生じたホットエレクトロンが、ドレイン電極60D近傍のチャネル領域40Aから固定電荷蓄積層50に注入され、蓄積される。これにより、チャネル領域40Aの電位が制御され、閾値電圧Vthがプラス方向にシフトする。

(もっと読む)

半導体装置、光学装置及びセンサ装置

【課題】ソース電極及びドレイン電極と有機半導体材料層との間の接触抵抗を低下させることができ、これを簡便な製造プロセスで実現できる半導体装置、光学装置及びセンサ装置を提供すること。

【解決手段】ソース電極5と、ドレイン電極6と、少なくともこれらの電極間に設けられた有機半導体材料層7とを有し、有機半導体材料層7を介してソース電極5とドレイン電極6との間で電荷を移動させるように構成された有機電界効果トランジスタにおいて、ソース電極5及びドレイン電極6が、導電性高分子材料と電荷移動錯体との混合物からなる、有機電界効果トランジスタ1a。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。信頼性の高い半導体装置を歩留まり良く作製する。

【解決手段】酸化物半導体膜を有するトップゲート構造のスタガ型トランジスタにおいて、酸化物半導体膜と接する第1のゲート絶縁膜を、プラズマCVD法によりフッ化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成し、該第1のゲート絶縁膜上に積層する第2のゲート絶縁膜を、プラズマCVD法により水素化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成する。

(もっと読む)

薄膜トランジスタ回路基板の製造方法及び薄膜トランジスタ回路基板

【課題】静電気による薄膜トランジスタの閾値電圧変動や絶縁破壊短絡を抑制できる薄膜トランジスタ回路基板の製造方法及び薄膜トランジスタ回路基板を提供する。

【解決手段】薄膜トランジスタと、静電気誘導素子と、を基板上に有する薄膜トランジスタ回路基板の製造方法であって、基板に設けられた半導体層の上に、薄膜トランジスタの半導体層のパターンを形成する第1のフォトリソ工程と、静電気誘導素子の半導体層のパターンを形成する第2のフォトリソ工程と、基板に設けられた半導体層をエッチングする工程と、を実施することにより薄膜トランジスタの半導体層及び静電気誘導素子の半導体層を形成し、第1のフォトリソ工程におけるフォトレジストの硬化温度は、第2のフォトリソ工程におけるフォトレジストの硬化温度よりも高いことを特徴とする薄膜トランジスタ回路基板の製造方法。

(もっと読む)

インバータ回路

【課題】1チップ化しつつ、高温化による誤動作を抑制し、かつ、半導体パワー素子に流れる電流を低減し、チップサイズの増大を抑制することができるインバータ回路を提供する。

【解決手段】コンバータ電源回路部2の電源供給ライン8中、例えば、IPD20におけるパワーMOSFET220のハイサイド側に電流制限抵抗240を備える。この電流制限抵抗240によって電源供給ライン8に流れる電流の電流値を制限することができるため、パワーMOSFET220での発熱を抑制することが可能となる。したがって、インバータ回路1内の素子の定格温度を超えることを防止することが可能となり、誤動作が生じることを抑制できる。これにより、インバータ回路1の信頼性の向上を図ることが可能となる。また、パワーMOSFET220として必要な能力を軽減することが可能となり、大面積な素子としなくても済む。

(もっと読む)

発光装置

【課題】鮮明な多階調カラー表示の可能な発光装置及びそれを具備する電気器具を提供する。

【解決手段】画素104に設けられたEL素子109の発光、非発光を時間で制御する時分割駆動方式により階調表示を行い、電流制御用TFT108の特性バラツキによる影響を防ぐ。また、基板上に形成されるTFT自体も各回路又は素子が必要とする性能に併せて最適な構造のTFTを配置することで、信頼性の高いアクティブマトリクス型発光装置を実現することができる。このようなアクティブマトリクス型発光装置を表示ディスプレイとして具備することで、画像品質が良く、信頼性の高い高性能な電気器具を生産することが可能となる。

(もっと読む)

半導体装置及びその作製方法

【課題】微小なコンタクトホールを形成し、集積回路を微細化することを目的とする。

【解決手段】スイッチング素子および各配線を覆う層間絶縁膜111として有機材料を用い、且つ、金属膜112のマスクを用い、ドライエッチング法によってコンタクトホールを形成し、配線114を形成する。

(もっと読む)

薄膜の作製方法、およびトランジスタの作製方法

【課題】膜応力の制御が可能なシリコン元素を有する薄膜の作製方法を提供することを目的の一とする。さらに、このシリコン元素を有する薄膜の作製方法を用いて、歩留まりを向上させることができるトランジスタの作製方法を提供することである。

【解決手段】プラズマCVD装置内の反応室の内壁を加熱して、反応室内壁に吸着している不純物を放出させる。次いで、反応室の内壁を加熱し続けしながらフッ素化合物ガスを用いたプラズマまたは反応室内の排気によって、反応室内壁に吸着している不純物および反応室内に残留している不純物を除去した後、反応室の内壁を加熱し続けしながらシリコン元素を有する薄膜を形成する。また、前記シリコン元素を有する薄膜を用いてトランジスタを作製する。

(もっと読む)

有機発光表示装置およびその製造方法

【課題】製造過程で用いられるフォトエッチング工程数を最小化できるように簡素な構造を有する有機発光表示装置を提供する。また、前記有機発光表示装置の製造方法を提供する。

【解決手段】本発明の実施形態に係る有機発光表示装置は、基板本体と、基板本体上に形成された多結晶アクティブ層および第1キャパシタ電極を含む多結晶シリコン層パターンと、多結晶シリコン層パターン上に形成されたゲート絶縁膜パターンと、ゲート絶縁膜パターン上に形成されたゲート電極および第2キャパシタ電極を含む第1導電膜パターンと、第1導電膜パターン上に形成された層間絶縁膜パターンと、層間絶縁膜パターン上に形成されたソース電極、ドレイン電極、および画素電極を含む第2導電膜パターンとを含む。ゲート絶縁膜パターンは、多結晶シリコン層パターンおよび第1導電膜パターンのうちのいずれか1つと共にパターニングされる。

(もっと読む)

341 - 360 / 2,024

[ Back to top ]