Fターム[5F110PP34]の内容

Fターム[5F110PP34]に分類される特許

81 - 100 / 815

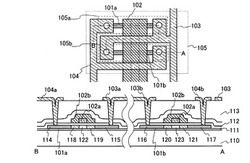

半導体装置

【課題】大面積基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような半導体素子の提供すること。また、そのような半導体素子を搭載し、薄膜半導体回路及び薄膜半導体装置を提供すること。さらに、多少のマスクずれが生じたとしても、その影響を受けずに動作するような半導体素子を提供する。

【解決手段】ドレイン領域114、117側の半導体層の低濃度不純物領域と重なるように形成した複数のゲート電極102を有し、それぞれのゲート電極102が形成するチャネル領域122、123に流れる電流の向きが一方向と一方向と反対の方向となるようにそれぞれのゲート電極102に対応するソース領域115、116とドレイン領域114、117を形成し、一方向に電流が流れるチャネル領域122と一方向と反対の方向に電流が流れるチャネル領域123の数が等しい薄膜トランジスタ。

(もっと読む)

半導体膜の形成方法、並びに、その半導体膜を用いた半導体装置、ディスプレイ装置。

【課題】結晶欠陥が低減されて結晶性が良好な半導体膜の形成方法及びその成方法を用いて製造された半導体装置並びにディスプレイ装置を提供する。

【解決手段】ガラス基板11上に非晶質シリコン膜12を形成する工程と、非晶質シリコン膜12の表面に、結晶化を促進する触媒物質であるニッケルを含むニッケル薄膜13を形成する工程と、非晶質シリコン膜12を熱処理して、非晶質シリコン膜12を結晶性シリコン膜12に結晶化する工程と、結晶性シリコン膜12に、隣接する各結晶粒の結晶方位角度差が、概略10°以下あるいは58°〜62°を保持する最も高い値になるようなエネルギー密度を有するエキシマレーザーを照射して、結晶性シリコン膜12の結晶性をさらに向上させて多結晶半導体膜とする工程とを包含する。

(もっと読む)

表示装置

【課題】本発明は、アクティブマトリクス型表示装置の製造コストを低減するこ

とを課題とし、安価な表示装置を提供することを課題とする。また、本発明の表

示装置を表示部に用いた安価な電子装置を提供することを目的とする。

【解決手段】 アクティブマトリクス型表示装置の製造コストを低減するために

画素部に用いるTFTを全て一導電型TFT(ここではpチャネル型TFTもし

くはnチャネル型TFTのいずれか一方を指す)とし、さらに駆動回路もすべて

画素部と同じ導電型のTFTで形成することを特徴とする。これにより製造工程

を大幅に削減し製造コストを低減することが可能となる。

(もっと読む)

半導体装置の作製方法

【課題】樹脂基板等の可撓性を有する基板を用いて、柔軟性を有する半導体装置を作製す

るための技術を提供する。

【解決手段】分離層を有する固定基板上に樹脂基板を形成する工程と、前記樹脂基板上に

少なくともTFT素子を形成する工程と、前記分離層にレーザー光を照射することにより

、前記分離層の層内または界面において前記固定基板から前記樹脂基板を剥離する工程と

を行い、前記樹脂基板を用いた柔軟性を有する表示装置を作製する。

(もっと読む)

半導体装置、液晶モジュール、電子機器及び配線

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

発光装置の作製方法

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って剥離することを可能とする。

【解決手段】基板上に金属層を形成する工程と、前記金属層上に酸化物層を形成する工程と、前記酸化物層上に絶縁層を形成する工程と、前記絶縁層上に薄膜トランジスタを形成する工程と、前記薄膜トランジスタ上に発光素子を形成する工程と、人間の手又は前記薄膜トランジスタを引き剥がす装置を用いることにより、前記酸化物層の層内または界面において前記基板から前記薄膜トランジスタを剥離する工程とを有する。

(もっと読む)

半導体装置の作製方法及び表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して、信頼性の高い半導体

装置を作製する方法を提供する。

【解決手段】基板上に導電層を形成し、該導電層上に光透過層を形成し、該光透過層上か

らフェムト秒レーザを照射して、該導電層及び該光透過層を選択的に除去する工程を有す

る。なお、該導電層の端部は、該光透過層の端部より内側に配置されるように該導電層及

び該光透過層を除去されていてもよい。また、フェムト秒レーザを照射する前に、該光透

過層表面に撥液処理を行ってもよい。

(もっと読む)

半導体装置、発光装置、モジュール、及び電子機器

【課題】電気光学装置において、新規の構成を有する画素回路を用いることにより、従来の構成の画素よりも高い開口率を実現することを目的とする。

【解決手段】i行目を除くゲート信号線の電位は、i行目のゲート信号線106が選択されている以外の期間においては定電位となっていることを利用し、i−1行目のゲート信号線111をi行目のゲート信号線106によって制御されるEL素子103への電流供給線として兼用することで配線数を減らし、高開口率を実現する。

(もっと読む)

半導体装置及びその作製方法

【課題】従来では、LDD構造を備えたTFTやGOLD構造を備えたTFTを形成しようとすると、その製造工程が複雑なものとなり工程数が増加してしまう問題があった。

【解決手段】第2のドーピング工程によって低濃度不純物領域24、25を形成した後、第4のエッチング工程を行うことによって、第3の電極18cに重なる低濃度不純物領域の幅と、第3の電極に重ならない低濃度不純物領域の幅とを自由に調節できる。こうして、第3の電極18cと重なっている領域は、電界集中の緩和が達成されてホットキャリアによる防止ができるとともに、第3の電極18cと重なっていない領域は、オフ電流値を抑えることができる。

(もっと読む)

半導体装置

【課題】本願発明で開示する発明は、従来と比較して、さらに結晶成長に要する熱処理時間を短縮してプロセス簡略化を図る。

【解決手段】

一つの活性層204を挟んで二つの触媒元素導入領域201、202を配置して結晶化を行い、触媒元素導入領域201からの結晶成長と、触媒元素導入領域202からの結晶成長とがぶつかる境界部205をソース領域またはドレイン領域となる領域204bに形成する。

(もっと読む)

電子機器

【課題】本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】本発明は、配線または電極をアルミニウム合金膜の単層とし、そのアルミニウム合金膜の組成を調節してITOとの良好なオーミック接合を目指すのではなく、3層構造とすることで課題を解決する。本発明は、アルミニウム原子のチャネル形成領域への拡散を防止するために、TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。さらに、その第2導電層の上に、ITOと反応しないアルミニウム合金からなる第3導電層を設け、配線又は電極を3層構造としてITOと接合させる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】現在、良質な膜を得るために、下地膜から非晶質シリコン膜までの形成プロセスは、各々の成膜室にて行われている。これらの成膜条件をそのまま用いて同一成膜室にて下地膜から非晶質シリコン膜までを連続形成すると、結晶化工程で十分に結晶化されない。

【解決手段】水素希釈したシランガスを用いて非晶質シリコン膜を形成することにより、下地膜から非晶質シリコン膜までを同一成膜室内で連続形成しても、結晶化工程で十分に結晶化可能となる。

(もっと読む)

半導体装置の作製方法

【課題】必要十分なキャパシティをもつ保持容量を備えた半導体装置を提供する。

【解決手段】金属表面を有する基板11と、前記金属表面を有する基板上に形成された絶縁膜12と、前記絶縁膜上に形成された画素部とを有する半導体装置において、前記画素部は、TFTと、該TFTと接続する配線21とを有しており、保持容量は、前記金属表面を有する基板、前記絶縁膜および前記配線により構成されている。前記絶縁膜の膜厚が薄いほど、また、前記絶縁膜と前記配線の接する領域の面積が大きいほど、大きなキャパシティを得られるので有利である。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置に於けるLDD構造とGOLD構造の形成は、従来、ゲート電極をマスクにセルフアラインで形成しているが、ゲート電極が2層構造となる場合が多く、成膜工程とエッチング工程が複雑になる。またドライエッチング等のプロセスのみでLDD構造及びGOLD構造の形成を行っている為、トランジスタ構造が全て同一構造となり、回路毎にLDD構造とGOLD構造及びシングルドレイン構造を別々に形成することが困難である。

【解決手段】 回折格子パターン或いは半透膜から成る光強度低減機能を有する補助パターンを設置したフォトマスク或いはレチクルをゲート電極形成用フォトリソグラフィ工程に適用することにより、ドライエッチング及びイオン注入工程を通し、回路毎にGOLD構造及びLDD構造及びシングルドレイン構造のトランジスタを簡単に形成することができることを特徴としている。

(もっと読む)

薄膜トランジスタ基板およびそれの製造方法

【課題】薄膜トランジスタ基板およびこれの製造方法を開示する。

【解決手段】本発明の薄膜トランジスタ基板は、基板上に形成されたゲート電極、前記ゲート電極上に前記ゲート電極と重なるように形成され、多結晶シリコンを含むアクティブ層、前記アクティブ層上に前記ゲート電極を中心に両側に分離して形成された第1オーミックコンタクト層、前記第1オーミックコンタクト層上に形成された第2オーミックコンタクト層および前記第2オーミックコンタクト層上に形成されたソース電極およびドレーン電極を含む。

(もっと読む)

表示装置

【課題】画素電極上に金属膜を形成して積層構造とする際に、1つのレジストマスクを用

いて、画素電極及び金属膜を形成することを課題とする。

【解決手段】画素電極となる導電膜と金属膜を積層させる。金属膜上に半透部を有する露

光マスクを用いて、膜厚の厚い領域と該領域よりも膜厚が薄い領域とを有するレジストパ

ターンを形成する。レジストパターンを用いて画素電極と、画素電極上の一部に接する金

属膜を形成する。以上により、1つのレジストマスクを用いて、画素電極及び金属膜を形

成することが可能となる。

(もっと読む)

半導体装置の作製方法及び液晶表示装置の作製方法

【課題】作製工程を増やすことなく、凹凸形状の画素電極を作製することを目的とする。

【解決手段】凸部は、フォトマスクを用いて作製すると再現性の高いものが得られるため、画素TFT1203の作製工程にしたがって作製すればよい。画素TFT1203の作製と同様に積層される半導体層、ゲート絶縁膜および導電膜を積層して凸部を形成する。こうして形成された凸部および同一工程で形成された画素TFT、駆動回路に含まれるTFTを覆うように層間絶縁膜を形成する。凹凸を有する層間絶縁膜が形成されたら、その上に画素電極を形成する。画素電極の表面も絶縁膜の凹凸の影響を受け表面が凹凸化する。

(もっと読む)

半導体装置の作製方法及びレーザ照射装置

【課題】レーザ光のエネルギー強度の弱い部分を遮断し、かつ光の回折による縞を発生させることなく、線状レーザ光を照射面に照射することができる、照射面上に均一強度の線状ビームを照射するレーザアニール方法及びレーザアニール装置の提供。

【解決手段】レーザ発振器101から射出されたレーザ光をスリット102を通過させて強度の弱い部分を遮断し、ミラー103で偏向させ、スリットにできた像を凸型シリンドリカルレンズ104によって照射面106に投影して照射面上に均一強度の線状ビームを照射することでレーザアニールを行う。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板901上に画素と不揮発性メモリとを備え、不揮発性メモリは、基板901上に形成される半導体活性層と、半導体活性層上に形成される絶縁膜923と、絶縁膜923上に形成されるフローティングゲイト電極907と、フローティングゲイト電極907を酸化して得られる酸化膜908,915,922と、酸化膜908,915,922に接して形成されるコントロールゲイト電極929と、を備え、画素と不揮発性メモリとは、基板901上に一体形成される。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

81 - 100 / 815

[ Back to top ]