Fターム[5F110QQ10]の内容

Fターム[5F110QQ10]に分類される特許

1 - 20 / 50

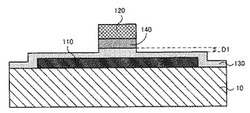

薄膜トランジスターの製造方法

【課題】例えば製造工程数の増加を招くことなく、複数の半導体層に水素化処理を確実に行う。

【解決手段】薄膜トランジスターの製造方法は、基板(10)上に、複数の半導体層(110)を同一層として形成する工程と、複数の半導体層を覆うようにシリコン酸化膜(130)を形成する工程と、シリコン酸化膜上に複数の半導体層を覆うようにシリコン窒化膜(140)を形成する工程と、シリコン窒化膜上に複数の半導体層を覆うように導電膜(121)を形成する工程と、導電膜及びシリコン窒化膜をエッチングにより一括でパターニングすることで、導電膜の一部からなるゲート電極(120)を形成するとともに、このエッチングの際、シリコン酸化膜の上層をオーバーエッチングする工程と、オーバーエッチングする工程の後に、半導体層にオーバーエッチングされたシリコン酸化膜を介して水素化処理を行う工程と、を有する。

(もっと読む)

歪チャネルを有するMOSトランジスタを製造する方法

【課題】歪チャネルを有するMOS トランジスタを製造するための比較的簡単な方法を提供する。

【解決手段】歪チャネルを有するMOS トランジスタ(M) を製造する方法は、(a) 半導体基板(10)の表面に、ソース領域及びドレイン領域とMOS トランジスタを囲む絶縁領域(22)に部分的に延びる絶縁された犠牲ゲートとを備えたMOS トランジスタを形成するステップと、(b) 犠牲ゲートの上面と略同一の高さの上面を有する絶縁層を形成するステップと、(c) 犠牲ゲートを除去するステップと、(d) 露出した絶縁領域(22)の少なくとも上部分をエッチングしてトレンチを形成するステップと、(e) 半導体基板(10)を歪ませることが可能な材料(24)をトレンチに充填するステップと、(f) 犠牲ゲートの除去によって空いた空間にMOS トランジスタの絶縁ゲート(12)を形成するステップとを有する。

(もっと読む)

薄膜トランジスタ、及びこれを備えた表示装置、並びにそれらの製造方法

【課題】相対的に大面積化した表示装置に効果的に用いることができる薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ、及びこれを備えた表示装置、並びにその製造方法において、本発明の実施形態に係る薄膜トランジスタは、基板上に形成されたアクティブ層と、前記アクティブ層の一部領域の上に形成されたゲート絶縁膜パターンと、前記ゲート絶縁膜パターンの一部領域の上に形成されたゲート電極と、前記ゲート絶縁膜パターン及び前記ゲート電極を覆うエッチング防止膜パターンと、前記アクティブ層及び前記エッチング防止膜パターンの上に形成されたソース部材及びドレイン部材とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】簡便な製造方法によって製造された良好なTFT特性を有する半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置は、絶縁基板11と、絶縁基板11に支持されたチャネル領域33A、ソース領域34Aおよびドレイン領域35Aを含む半導体層30Aと、チャネル領域33Aの導電性を制御するゲート電極51とを有する。半導体層30Aは、チャネル領域33Aとソース領域34Aとの間に形成された第1低濃度領域31A、および、チャネル領域33Aとドレイン領域35Aとの間に形成された第2低濃度領域32Aとを有する。チャネル領域33A、第1および第2低濃度領域31Aおよび32Aは、ソースおよびドレイン領域34Aおよび35Aの不純物濃度より低い第1不純物濃度を有する。ゲート電極51は、第1および第2低濃度領域31Aおよび32Aの全部を覆うように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易なプロセスで、高い埋め込み性を確保する必要のない半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法では、まず支持基板SSと、埋め込み絶縁膜BOXと半導体層SLとがこの順で積層された構成を有する半導体基板SUBが準備される。半導体層SLの主表面に、導電部分を有する素子が完成される。上記素子を平面視において取り囲む溝DTRが、半導体層SLの主表面から埋め込み絶縁膜BOXに達するように形成される。上記素子上を覆うように、かつ溝DTR内に中空を形成するように素子上および溝DTR内に第1の絶縁膜(層間絶縁膜II)が形成される。上記第1の絶縁膜に素子の導電部分に達する孔であるコンタクトホールCHが形成される。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】絶縁表面上に第1配線と、前記第1配線を覆う第1層間絶縁膜と、前記第1層間絶縁膜上の一部に接して第2層間絶縁膜と、前記第1層間絶縁膜及び前記第2層間絶縁膜上に第2配線とを有し、前記第1配線と前記第2配線とが重なっている領域には、前記第1層間絶縁膜と前記第2層間絶縁膜とが積層された半導体装置である。第1配線と第2配線間に層間絶縁膜が積層されていることで寄生容量の低減が可能となる。

(もっと読む)

TFT−LCDアレイ基板及びその製造方法

【課題】基板に形成された複数のゲートライン及び複数のデータラインを含み、ゲートラインとデータラインにより複数の画素領域が画定され、画素領域ごとに画素電極及びスイッチング素子としての薄膜トランジスタが形成されるTFT−LCDアレイ基板を提供する。

【解決手段】本発明は、TFT−LCDアレイ基板及びその製造方法に関する。アレイ基板には、基板に形成された複数のゲートライン及び複数のデータラインが含まれる。前記ゲートラインとデータラインにより複数の画素領域が画定され、画素領域ごとに画素電極及びスイッチング素子としての薄膜トランジスタが形成されている。前記薄膜トランジスタのゲート電極は連結電極を介して対応したゲートラインに電気的に接続され、前記ゲート電極と前記ゲートラインは異なる材料層により形成される。

(もっと読む)

薄膜トランジスタ搭載基板、その製造方法及び画像表示装置

【課題】活性層として用いた酸化物薄膜の安定化と高品質化を実現した薄膜トランジスタをプラスチック基板上に搭載した薄膜トランジスタ搭載基板の製造方法を提供する。

【解決手段】プラスチック基板10の上又はその上方に活性層となるアモルファス酸化物薄膜13を形成する工程と、少なくとも活性層となる部分のアモルファス酸化物薄膜13に向けてパルスレーザー20を照射する工程とを少なくとも有する。パルスレーザー20の照射工程は、プラスチック基板10に該プラスチック基板のガラス転移温度以上の温度を一定時間加えず、且つアモルファス酸化物薄膜13をアモルファス相のままで所定の比抵抗に制御する工程である。

(もっと読む)

半導体装置およびその製造方法

【課題】薄膜BOX−SOI基板に形成される電界効果型トランジスタの信頼性および動作特性の劣化を防ぐことのできる技術を提供する。

【解決手段】薄膜BOX−SOI基板の主面上に所定の間隔で配置されたnウェルnwおよびpウェルpwが形成されており、pウェルpwに形成されたnMIS1nは、SOI層1iの主面上に所定の距離を隔てて積み上げられた半導体層に形成された一対のn型ソース・ドレイン領域2nと、一対のn型ソース・ドレイン領域2nに挟まれたゲート絶縁膜3、ゲート電極4、およびサイドウォール5とを有しており、nウェルnwとpウェルpwとの間に素子分離10を形成し、素子分離10の側端部が、n型ソース・ドレイン領域2nの側端部(BOX層1bの側壁部)よりもゲート電極4側に広がっている。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を無機絶縁膜で覆うことなく加熱処理を行って酸化物半導体層が結晶化されると、結晶化による表面凹凸などが形成され、電気特性のバラツキが発生する恐れがある。

【解決手段】酸化物半導体層成膜直後から酸化物半導体層上に接して酸化シリコンを含む無機絶縁膜を形成する直前までの間に1回も加熱処理を行わず、基板上の酸化物半導体層上に接して第2の絶縁膜を形成した後に加熱処理を行うプロセス順序とする。また、酸化シリコンを含む無機絶縁膜において、膜中に含まれる水素密度は、5×1020/cm3以上、または窒素密度は、1×1019/cm3以上とする。

(もっと読む)

半導体装置

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

ホウ素ドープ半導体ナノワイヤ及びその製造方法

【課題】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤ及びその製造方法を提供する。

【解決手段】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤは、次の工程を含む製造方法により製造できる。

工程(1):半導体原料ガスを用いて、基板上にIV族半導体ナノワイヤを成長させる;

工程(2):ジボランガスのみを導入することにより、前記半導体ナノワイヤの表面にホウ素膜を堆積させる;

工程(3):表面にホウ素膜を堆積させた前記ホウ素膜付き半導体ナノワイヤを、半導体ナノワイヤ(本体)の融点以下の温度で熱アニールする。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】ゲート絶縁層の厚さを大きくすることが容易であり、ゲート絶縁層の影響によるチャネル層の半導体特性の劣化が防止された薄膜トランジスタを提供する。

【解決手段】基板1上にソース電極5及びドレイン電極6を間隔をあけて形成し、次いでこれらソース電極5、ドレイン電極6及び基板1の上に、酸化物半導体層よりなる半導体層4を形成する。この半導体層4の上に有機絶縁層よりなる絶縁層3を形成し、次いでこの絶縁層3上にゲート電極2を形成して、トップゲート構造の薄膜トランジスタ10を得る。酸化物半導体層を形成した後に有機絶縁層を形成するため、酸化物半導体層の形成時に有機絶縁層中の有機物が酸化物半導体層に混入して半導体特性が劣化することが防止される。有機絶縁層は、金属酸化物絶縁層と比べて、厚さを大きくして耐電圧特性を向上させることが非常に容易である。

(もっと読む)

薄膜トランジスタ、および薄膜トランジスタアレイ

【課題】 薄膜トランジスタの特性を良好にすると同時に、蓄積容量部に形成される金属−絶縁体−半導体構造(MIS構造)を解消しキャパシタの値を安定化させることで、フォトマスク工程数を削減しても高い性能を維持できる薄膜トランジスタ及びそれを用いた表示装置を提供する。

【解決手段】 4回以下のフォトマスク工程数で作製される薄膜トランジスタ部216と、蓄積容量部217とを有する薄膜トランジスタアレイ基板において、チャンネルの形成に寄与しない活性半導体層をシリサイド化する。

(もっと読む)

半導体装置

【課題】 LDD形成工程に於けるプラズマプロセスが原因となり生じる素子の

損傷を極力低減した半導体装置の作製方法を提供すること。

【解決手段】 基板全面を覆うように導電性膜を形成した状態で、ハードマスク

を利用した半導体装置の作製方法でLDD構造の素子を形成することにより、L

DD形成工程におけるプラズマプロセスによる素子への損傷を極力低減する。導

電性膜が全面に形成されていることにより、異方性エッチング等のプラズマによ

る処理(プラズマプロセス)においてゲート電極に蓄積される電荷密度を低減で

き、プラズマプロセスによる損傷を低減できる。

(もっと読む)

表示装置及び電子デバイス

【課題】反射型表示装置の製造工程を大幅に簡略化する。

【解決手段】薄膜トランジスタと、薄膜トランジスタの上方に配置された絶縁層及び画素電極を有し、画素電極は、薄膜トランジスタに電気的に接続され、表面に凹凸を有し、かつ、反射機能を有し、絶縁層は、酸化珪素、窒化珪素、酸化窒化珪素及び有機性樹脂から選ばれた材料を積層した構造を有し、絶縁層の少なくとも一層はカーボン系材料及び顔料の少なくともいずれか一を含む遮光膜である表示装置とする。

(もっと読む)

半導体装置の製造方法

【課題】急峻な不純物濃度のプロファイルを有するソース領域およびドレイン領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板の表面近傍に不純物を注入して不純物注入領域を形成する工程と、前記半導体基板にエッチングを施すことにより前記不純物注入領域の底部よりも深い溝を形成し、前記不純物注入領域を分断してソース領域およびドレイン領域を形成する工程と、前記溝の内部にSi系単結晶をエピタキシャル成長させてエピタキシャル結晶層を形成する工程と、前記エピタキシャル結晶層の上部にゲート絶縁膜およびゲート電極を形成する工程と、を含む。

(もっと読む)

回路基板の製造方法および半導体装置の製造方法並びに回路基板

【課題】半導体回路における、劈開分離のためのイオンのイオン残りを防止するとともに、ターゲット基板としてガラス基板等の、高温に耐えることができない絶縁基板を用いた場合でも、高温下での脱イオン処理によるシュリンク等のターゲット基板への影響を排除することができる回路基板の製造方法を提供する。

【解決手段】半導体基板上に半導体回路を有し、上記半導体基板内における上記半導体回路の下に、上記半導体基板を劈開分離するイオンが注入されたイオン注入層を有する回路基板を製造するに際し、上記イオン注入層中のイオンを保持したまま上記半導体回路から該半導体回路中に存在する上記劈開分離のためのイオンを脱イオンする。

(もっと読む)

半導体装置の作製方法

【課題】動作性能及び信頼性を向上させた半導体装置の作製方法を提供する。

【解決手段】単結晶シリコン基板の一部からなる単結晶シリコン薄膜を、単結晶シリコン基板を熱酸化して得られた第1の酸化シリコン膜上に有し、第1の酸化シリコン膜が、シリコン基板上に設けられた第2の酸化シリコン膜に貼り合わされたシリコン基板を用いる半導体装置の作製方法であって、単結晶シリコン薄膜から複数の島状シリコン層を形成し、複数の島状シリコン層の熱酸化工程後に、複数の島状シリコン層上にポリシリコンでなるゲート電極を形成し、ゲート電極の側面にサイドウォールを形成し、複数の島状シリコン層にソース領域及びドレイン領域を形成し、ゲート電極、ソース領域、ドレイン領域に金属膜を形成し、加熱してゲート電極、ソース領域、ドレイン領域にシリサイドを形成し、複数の島状シリコン層を覆って、層間絶縁膜を形成する半導体装置の作製方法を提供する。

(もっと読む)

駆動回路、アクティブマトリクス基板及び液晶表示装置

【課題】単一導電型のTFTからなる駆動回路に要求されるTFTのオフリーク電流を、簡単な製造工程で実現する。

【解決手段】TFT10のソース領域17及びドレイン領域18の不純物濃度を2×1018[cm−3]以上かつ2×1019[cm−3]以下とすることにより、シングルゲート構造でもTFT10のオフリーク電流を十分に低減できる。

(もっと読む)

1 - 20 / 50

[ Back to top ]