Fターム[5F110QQ16]の内容

Fターム[5F110QQ16]の下位に属するFターム

素子形成前に貼り合わせ (694)

Fターム[5F110QQ16]に分類される特許

601 - 611 / 611

ダブルゲート電界効果トランジスタとして用いられる層構造体、および、その製造方法

【課題】ダブルゲート電界効果トランジスタとして用いられる層構造、および、その製造方法を提供する。

【解決手段】本発明の方法では、補助基板上に、多孔質シリコン層を犠牲層として形成する。この犠牲層の上に第1半導体層、第1電気絶縁層を順次形成する。第1電気絶縁層の上に、導電層を形成し、ラテラルにパターン形成する。ラテラルにパターン形成された導電層を共通のマスクとして用いて、第1電気絶縁層、犠牲層、および、第1半導体層をラテラルにパターン形成する。さらに、パターン形成された犠牲層の側壁とパターン形成された第1半導体層の側壁とに隣接して、半導体部を形成する。基板を、パターン形成された導電層の上方に固定し、補助基板の材料を除去して、犠牲層を露出させる。さらに、犠牲層を選択的に除去することにより、トレンチを形成する。トレンチ中に、第2電気絶縁層を形成し、その上に導電部を形成する。

(もっと読む)

有機薄膜素子の製造方法、電気光学装置の製造方法及び電子機器の製造方法

【課題】

簡便な方法で素子寿命の長い有機薄膜素子を提供し得る有機薄膜素子の製造方法、それを利用した電気光学装置の製造方法及び電子機器の製造方法の提供。

【解決手段】

少なくとも一の透明電極を備えた一対の薄膜電極間に有機薄膜を含んで構成される有機薄膜素子の製造方法であって、基材上に透明電極形成材料を含む原料液を噴霧することにより透明電極を形成する工程と、前記透明電極上に有機薄膜を形成する工程と、を含む有機薄膜素子の製造方法により、上記課題を解決する。

(もっと読む)

半導体装置及びその作製方法

【課題】本発明は、低コストで大量生産が可能である半導体装置及びその作製方法を提供する。また、非常に膜厚の薄い集積回路を用いた半導体装置、及びその作製方法を提供する。更には、低消費電力である半導体装置及びその作製方法を提供する。

【解決手段】本発明は、絶縁表面上に半導体不揮発性記憶素子トランジスタを有し、メモリトランジスタのフローティングゲート電極が、複数の導電性粒子又は半導体粒子で形成されていることを特徴とする半導体装置である。

(もっと読む)

有機半導体付フィルム

本発明はフィルム(1)、特に型押フィルムまたは積層フィルム、及びそのようなフィルムの作成のためのプロセスに関する。有機半導体技術を用いて作成される少なくとも1つのデバイス、特に1つまたはそれより多くの有機電界効果トランジスタがフィルム(1)に集積される。  (もっと読む)

(もっと読む)

半導体基板の製造方法、及び半導体基板

【課題】剥離用物質を注入して半導体層を薄膜化すると共に、半導体デバイス部に対する剥離用物質による悪影響を排除する。

【解決手段】半導体装置Sの製造方法は、半導体層20の表面に絶縁層であるゲート酸化膜4を形成する絶縁層形成工程と、半導体層20に対し、半導体層における上記剥離用物質の移動を抑止するためのホウ素イオンを注入し、該半導体層20に拡散抑止層35を形成する拡散抑止層形成工程と、拡散抑止層35のホウ素を加熱して活性化させる活性化工程と、半導体層20に水素イオンを注入し、半導体層20の領域のうち拡散抑止層35を介してゲート酸化膜4と反対側の領域に剥離層36を形成する剥離層形成工程と、半導体層20のゲート酸化膜4側にガラス基板18を貼り合わせる貼り合わせ工程と、半導体層20を熱処理することにより、半導体層20を剥離層36に沿って分割する分割工程とを備えている。

(もっと読む)

半導体装置

【課題】同一なチップ内でNチャネルおよびPチャネルの両チャネルが高い耐圧特性を有する高耐圧MOSトランジスタを実現でき得るデバイス構造の製造方法を提供する。

【解決手段】本発明は、Nch型L−DMOS101 とPch型L−DMOS102と論理部103 から成る半導体装置であり、Nch型L−DMOS101 は、N型ドリフト領域12、Pウエル19、P型高濃度拡散層20、ソース拡散層21、ドレイン拡散層22、ソースコンタクト14、ドレインコンタクト16、ソース電極配線15、ドレイン電極17、ゲート電極18の各主要素から成り、SOI領域であるN型ドリフト領域12に形成されたこのNch型L−DMOS101のソース電極14と、領域11と、を電気的に導通して同電位になるように構成するデバイス構造である。

(もっと読む)

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

本発明は、印刷可能半導体素子を製造するとともに、印刷可能半導体素子を基板表面上に組み立てるための方法及びデバイスを提供する。本発明の方法、デバイス、デバイス部品は、幅広いフレキシブル電子デバイス及び光電子デバイス並びにデバイスの配列を高分子材料を備える基板上に形成することができる。また、本発明は、伸張形態で良好な性能が得られる伸縮可能な半導体構造及び伸縮可能な電子デバイスも提供する。 (もっと読む)

独立して歪むNチャネル型及びPチャネル型トランジスタ

第一ウェハ上に形成された第一の複数のトランジスタと、第二ウェハ上に形成された第二の複数のトランジスタとを備えた集積回路。第一トランジスタのうち少なくとも実質的に大部分が第一導電型であり、第二の複数のトランジスタのうち少なくとも実質的に大部分が第二導電型である。ウェハ同士が結合された後、第二ウェハの一部が除去されて、第二の複数のトランジスタのチャネルの歪みの圧縮性が、第一の複数のトランジスタのチャネルの歪みの圧縮性よりも高くなる。  (もっと読む)

(もっと読む)

可撓性有機電子装置およびその作製方法

本発明は、透明導電酸化物層を含む第1の電極、有機活性層、第2の電極、および高分子基板層を少なくとも含み、透明導電層が、少なくとも250℃の温度で、除去可能な基板層上、または除去可能な基板層上に事前に適用された一つまたは複数の透明層上に適用され、高分子基板層が適用されると、除去可能な担体が除去される、可撓性有機電子装置を作製するための方法を提供する。本発明は、この方法によって得られる可撓性有機電子装置をさらに提供する。 (もっと読む)

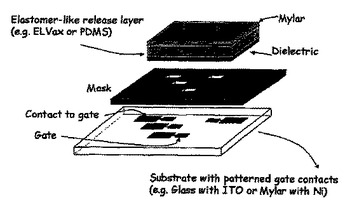

マスクを通した積層

本発明はドナー基板からレシーバ基板に材料のパターンを積層によって転写する方法である。転写された材料のパターンは、積層の際にドナーとレシーバとの間に挿入されたマスクの開口によって画定される。この技法は可撓性ポリマーレシーバ基板に適合しており、可撓性表示装置用の薄膜トランジスタを作製するのに有用である。

(もっと読む)

(もっと読む)

金属電極を備えているトランジスタデバイスおよびそのようなデバイスを形成する際に用いるための方法

金属ソース電極と、金属ドレイン電極と、金属ゲート電極と、堆積させた半導体材料内のチャネルとを有するトランジスタデバイスであって、金属ゲート電極、金属ソース電極の第1の金属部分、および金属ドレイン電極の第1の金属部分を含む第1の層と、金属ソース電極の第2の金属部分、金属ドレイン電極の第2の金属部分、堆積させた半導体材料、および半導体材料と金属ゲート電極との間にある誘電体材料を含む第2の層と、基板を含む第3の層とを含み、第1の層、第2の層および第3の層は、第2の層が第1の層と第3の層との間に配置されるような順序で構成されているトランジスタデバイス。  (もっと読む)

(もっと読む)

601 - 611 / 611

[ Back to top ]