Fターム[5F110QQ17]の内容

Fターム[5F110QQ17]に分類される特許

681 - 694 / 694

改善されたキャリア移動度を有するフィンFETとその形成方法

フィンFETデバイスが、キャリア移動度を向上させるために歪みシリコンを利用する。一方法において、フィンFET体(46)が、誘電層(40)を覆うシリコンゲルマニウム(SiGe)(42)にパターニングされる。シリコンのエピタキシャル層(34)がその後、シリコンゲルマニウムフィンFET体(46)に形成される。真性シリコン結晶格子と、エピタキシャルシリコンが成長するテンプレートとして供するシリコンゲルマニウム結晶格子の異なる形状寸法の結果、歪みが導入される。歪みシリコンでは、リラックスシリコンに比較してキャリア移動度が増大し、結果としてエピタキシャル歪みシリコンが、フィンFETにキャリア移動度の増大を与える。従って、歪みシリコンチャネル層を利用することで、比較的高い駆動電流がフィンFET内に流され得る。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 SOI基板を用いてより高性能なMISFETを実現する。

【解決手段】 SOI基板を用いた半導体装置であって、第1の絶縁膜11上に形成された第1の半導体層12と、第1の半導体層12の主面上の一部に第2の絶縁膜13を介して形成された、第1の半導体層12とは面方位が異なる第2の半導体層14と、第1の半導体層12の主面に形成された第1導電型のMISFETと、第2の半導体層14の主面に形成された第2導電型のMISFETとを備えた。

(もっと読む)

半導体基板の製造方法、及び半導体基板

【課題】剥離用物質を注入して半導体層を薄膜化すると共に、半導体デバイス部に対する剥離用物質による悪影響を排除する。

【解決手段】半導体装置Sの製造方法は、半導体層20の表面に絶縁層であるゲート酸化膜4を形成する絶縁層形成工程と、半導体層20に対し、半導体層における上記剥離用物質の移動を抑止するためのホウ素イオンを注入し、該半導体層20に拡散抑止層35を形成する拡散抑止層形成工程と、拡散抑止層35のホウ素を加熱して活性化させる活性化工程と、半導体層20に水素イオンを注入し、半導体層20の領域のうち拡散抑止層35を介してゲート酸化膜4と反対側の領域に剥離層36を形成する剥離層形成工程と、半導体層20のゲート酸化膜4側にガラス基板18を貼り合わせる貼り合わせ工程と、半導体層20を熱処理することにより、半導体層20を剥離層36に沿って分割する分割工程とを備えている。

(もっと読む)

SOIトレンチ横型IGBT

【課題】IGBTにおいて、高耐圧で、大電流での駆動を可能とし、ラッチアップ耐量を高くし、単位面積あたりのオン抵抗を低くすること。

【解決手段】n+エミッタ領域6aとp+コレクタ領域12aとの間のウェハ全面にトレンチ16a,16bを形成し、その中をトレンチ埋め込み絶縁膜17で埋めることによって、耐圧を担持するドリフト領域を折り曲げて、実効的なドリフト長を長くする。トレンチ埋め込み絶縁膜17内に、エミッタ側フィールドプレート15を埋め込み、トレンチ埋め込み絶縁膜17のエミッタ側に生じる横電界を遮蔽することによって、n-ドリフト領域3aとpベース領域4aとのPN接合で発生する電界を緩和する。

(もっと読む)

平面デュアルゲート半導体装置

デュアルゲート半導体装置の製造方法は、シリコン体(16)の第1の表面(14)の一部分上に第1のゲート(12)が形成された後であるが、前記第1の表面の反対側のシリコン体の第2の表面(44)上に第2のゲート(52)を形成する前に行われるソース及びドレインコンタクト領域(34,36)のシリサイド化を備える。第1のゲート(12)はソース及びドレインコンタクト領域がシリコンチャネル(18)に位置合わせされることを保証するマスクの働きをする。さらに、製造の早い段階でシリサイド化を行うことにより、第2のゲートの材料の選択が高温処理により制限されない。シリサイド化によるシリコン体の第2の表面での材料特性の違いがシリサイドのソースコンタクト領域とドレインコンタクト領域との間に前記第2のゲートを横方向に位置合わせされることを可能にすることが有利である。  (もっと読む)

(もっと読む)

埋め込みガードリング及び耐放射線性分離構造並びにその製造方法

【課題】大量の商業マイクロエレクトロニクスメーカーがアクセスし易い最先端の基礎設備を使用して、高性能且つ費用対効果に優れた耐放射線性集積回路(RHICs)を提供する。

【解決手段】様々な形式の放射線エネルギーによって引き起こされる有害な影響を減少し、又は排除するために、従来の設計及びプロセスを使用する一方で特殊構造を含んで半導体デバイスを作成する。このような半導体デバイスは本願で開示された1台以上の寄生的な分離デバイス、及び/又は、埋め込みガードリング構造を含む。これら新規な構造に対応する設計、及び/又は、工程ステップの導入には、従来のCMOS製作工程との互換性がある。したがって、比較的低い費用で比較的簡単に実施することができる。

(もっと読む)

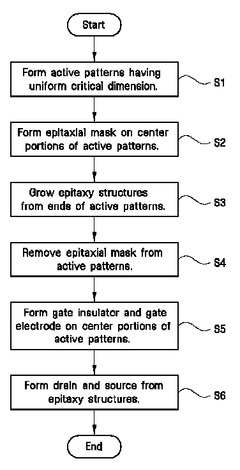

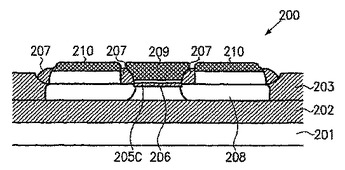

均一な臨界寸法のアクティブパターンで形成されたマルチゲートトランジスタ及びその製造方法

本発明は、均一な臨界寸法のアクティブパターンで構成されたマルチゲートトランジスタの製造方法を提供する。本発明はまた、均一な臨界寸法のアクティブパターンを具備するマルチゲートトランジスタを提供する。マルチゲートトランジスタの製造方法は先に少なくとも一つのアクティブパターンを形成する。以後、前記アクティブパターンの露出した領域から少なくとも一つのエピタキシ構造を成長させる。続いて、前記アクティブパターンの少なくとも2個の面にチャネル領域を形成する。  (もっと読む)

(もっと読む)

半導体構造および半導体構造を製造する方法

【課題】 半導体デバイスおよび半導体デバイスを製造する方法を提供することにある。

【解決手段】 この半導体デバイスは、pFETおよびnFET用のチャネルを含む。nFETチャネルのチャネル内にはSiGe層を成長させ、pFETチャネル内には炭化シリコン層を成長させる。SiGe層および炭化シリコン層は、上に重なって成長させたエピタキシャル層内に応力成分を発生させるために、下にあるSi層の格子回路網と整合する。一実現例では、これにより、pFETチャネル内に圧縮成分が発生し、nFETチャネル内に引張成分が発生する。他の一実現例では、nFETチャネルとpFETチャネルの両方にSiGe層を成長させる。この実現例では、pFETチャネル内の応力レベルは約3GPaを上回るものでなければならない。

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

フィン型電界効果トランジスタを有する半導体装置

n型電界効果トランジスタおよびp型電界効果トランジスタとを含む半導体装置であって、n型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{100}面であり、p型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{110}面である、という条件を満足する半導体装置とする。 (もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上面から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在する絶縁膜と、ソース/ドレイン領域とを有するMIS型電界効果トランジスタを備えた半導体装置であって、1つのチップ内に、前記MIS型電界効果トランジスタとして、ゲート電極下の前記半導体凸部における基板平面に平行かつチャネル長方向に垂直な方向の幅Wが互いに異なる複数種のトランジスタを有する半導体装置。 (もっと読む)

ゲートの枯渇を低減した注入ゲート電極を有する電界効果型トランジスタ、及び、このトランジスタを製造する方法

ドレイン領域及びソース領域(208)を規定する前に、注入マスク(220)を形成することにより、ゲートドーパント密度をドレインドーパント密度及びゲートドーパント密度から効果的に分離する。さらに、注入マスク(220)を除去した後に、ゲート電極(205)の横方向寸法は、十分に確立された側壁スペーサ(207)技術によって規定される。その結果、フォトリソグラフィ及び異方性エッチングに基づく従来の方法に対してデバイスの縮小に関する優位性を提供する。  (もっと読む)

(もっと読む)

フロントゲート型SOI−MOSFETの製造方法

【課題】ソース/ドレイン拡張とフロントゲート(front gate)に自己整合させたバックゲートを含む、FD型SOI−CMOSデバイスの製造方法に関する。

【解決手段】

SOI−CMOS技術は、ポリシリコン、即ちポリSiバックゲートは、フロントゲート・デバイスの閾値電圧を制御するために使用され、nMOS及びpMOSバックゲートは、互いに独立に、及びフロントゲートと独立に、スイッチされる。

特に、バックゲートが、デバイスのフロントゲート及びソース/ドレイン拡張に自己整合されたバックゲートFD型CMOSデバイスの製造方法を提供する。バックゲートFD型CMOSデバイスは、SIMOX又は結合SOI−ウエハ、ウエハボンディングと薄膜化、ポリSiエッチング、LP−CVD、機械化学研磨(CMP)を用いて製造される。

(もっと読む)

SOI基板の作製方法

【課題】 バックゲート電極を有するSOI基板を貼り合わせ法により形成する場合に、段差平坦化用polySi層の形成を不要とし、また、貼り合わせの歩留まりを向上させ、製造コストを低下させる。

【解決手段】基板貼り合わせ法によるSOI基板の作製方法において、第1の半導体基板1に段差を形成し、段差の形成面上に、所定の深さの開孔部8を有する研磨ストッパー用絶縁膜3を形成し、研磨ストッパー用絶縁膜3上にpolySiを堆積して開孔部8にpolySiを充填し、さらにディッシング防止用酸化膜9を形成し、これを平坦化することによりバックゲート電極BGを形成し、この平坦化面上に第2の半導体基板7を貼り合わせ用酸化膜10を介して貼り合わせることにより、バックゲート電極BGを有するSOI基100Aを作製する。

(もっと読む)

681 - 694 / 694

[ Back to top ]